Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Elettronica 2 - Divisore Di Frequenza

Caricato da

Salvo Skiffy SapienzaCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Elettronica 2 - Divisore Di Frequenza

Caricato da

Salvo Skiffy SapienzaCopyright:

Formati disponibili

Divisore di frequenza 1

Divisore di frequenza

Il divisore di frequenza un circuito elettronico che prende in ingresso un segnale con un certa frequenza e

genera in uscita un segnale con frequenza:

dove un intero. I sintetizzatori di frequenza ottenuti con le phase-locked loop usano i divisori di frequenza per

ottenere un'uscita a una frequenza multipla di quella di un certo segnale di riferimento. Esistono per i divisori di

frequenza sia implementazioni di tipo analogico che digitale.

Divisore di frequenza digitale contatore e FF

Un divisore di frequenza possibile realizzarlo, soprattutto per implementarlo in linguaggi di programmazione come

verilog, VHDL, C e C++, con un sommatore e una serie di registri. Il contatore conta fino a quando nell'ultimo

registro memorizzer 1 allora si riazzerer e rinizier il conteggio. Ogni volta che il conteggio alza l'ennesimo f-f

allora il clk in uscita sar alto altrimenti basso. Se si ha un clk di 50MHz in ingresso ci sar bisogno di 25 f-f per

raggiungere un clk in uscita con una frequenza di circa 1s.

Divisori analogici

Divisore di frequenza retroazionato

Un divisore di frequenza retroazionato, conosciuto anche come divisore di frequenza di Miller[1] mixa il segnale di

ingresso con il segnale retroazionato dal mixer.

Il segnale retroazionato . Esso produce le frequenza somma e differenza e in uscita al

mixer. Un filtro passa-basso rimuove la frequenza pi elevata e il segnale rimanente, a frequenza

amplificato da uno stadio amplificatore e riportato al mixer.

Uno studio a regime semplice, mentre il transitorio piuttosto complicato. Per ottenere una frequenza stabile a

sulla retroazione, il guadagno dell'amplificatore deve essere pi grande dell'unit. Lo sfasamento deve essere

inoltre un multiplo intero di 2.

Divisore di frequenza 2

Divisore di frequenza injection-locked

Un ILFD (injection locked frequency divider) funziona similmente a un injection-locked oscillator. La frequenza del

segnale di ingresso multipla della frequenza di free running di un VCO, cio della frequenza alla quale oscilla in

assenza di ingresso. Tale segnale di ingresso prodotto dallo stesso oscillatore, come componente ad alta frequenza

di oscillazione. Questi divisori di frequenza sono stati usati intensamente nello sviluppo della televisione.

Divisori digitali

Per dividere un segnale digitale di un

multiplo intero viene usato un contatore

Johnson o ad anello. Esso un tipo di

registro a scorrimento che temporizzato

dal segnale di ingresso. L'uscita

complementata dell'ultimo registro

riportata all'ingresso del primo registro. Il

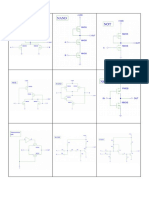

segnale di uscita ottenuto dalla Esempio di un divisore di frequenza intero modulo 8 implementato con flip-flop T.

combinazione delle uscite dei vari registri.

Per esempio, un divisore per 3 pu essere costruito con un contatore Johnson a 3 registri. I tre valori validi per ogni

registro sono000, 100, 110, 111, 011 e 001. Questo pattern si ripete ogni volta che il segnale di ingresso temporizza

il contatore. I valori000 e 111 vengono ottenuti a distanza di tre colpi di clock e controllano il cambiamento di stato

del segnale di uscita.

Per divisioni per potenze di 2, si pu usare un semplice contatore binario, temporizzato dal segnale di ingresso. Il bit

meno significativo (lsb) oscilla alla stessa frequenza dell'ingresso, il bit adiacente a met della frequenza, il terzo a

un quarto e cos via.

possibile ottenere dei divisori interi anche con particolari connessioni di flip-flop. La configurazione pi semplice

una serie dove ciascun bistabile un divisore per due. Per una serie di tre di questi, il sistema complessivo divider

per 8. Aggiungendo ulteriori gate logici alla catena, si possono ottenere altri rapporti di divisione. Le tecnologie

integrate permettono di ottenere soluzioni di questo tipo in un unico chip.

Divisori frazionari

Un divisore di frequenza frazionario pu essere ottenuto usando due divisori interi, uno che divide per n e uno per

n+1. Con un controllore, possibile scegliere di utilizzare un divisore oppure l'altro. Variando la percentuale di

tempo in cui complessivamente il sistema divide per n o n+1, si pu scegliere con una certa granularit il valore per

cui effettivamente in media la frequenza viene divisa.

Modulatori sigma-delta

Per approfondire, vedi Modulazione Sigma-Delta.

Se la sequenza di divisioni per n o n+1 periodica, all'uscita del divisore compaiono anche delle frequenze spurie

oltre a quelle desiderate. Nei modulatori sigma-delta la sequenza di n e n+1 casuale, per in media permette di

ottenere comunque il valore di divisione voluto. In questa maniera il segnale spurio si trova ad alta frequenza e pu

essere facilmente filtrato.

Potrebbero piacerti anche

- Analisi - Elementi Di Elaborazione Numerica Dei Segnali Audio SegnaleDocumento0 pagineAnalisi - Elementi Di Elaborazione Numerica Dei Segnali Audio SegnalenamagiNessuna valutazione finora

- Bianchini Bode myDAQDocumento14 pagineBianchini Bode myDAQIsacco BianchiniNessuna valutazione finora

- Radio FM Bertelli Miotto PDFDocumento23 pagineRadio FM Bertelli Miotto PDFManotti AndreaNessuna valutazione finora

- Segnali 2Documento114 pagineSegnali 2sara marziNessuna valutazione finora

- Funzionamento PLLDocumento10 pagineFunzionamento PLLRodrigo OrfeoNessuna valutazione finora

- Ricevitore SupeterodinaDocumento8 pagineRicevitore Supeterodinatigre73Nessuna valutazione finora

- Sistemi Elettroacustici I-1Documento8 pagineSistemi Elettroacustici I-1Samuele NapoliNessuna valutazione finora

- Ripasso ElettrotecnicaDocumento9 pagineRipasso ElettrotecnicaHshdhd HdhxdNessuna valutazione finora

- Excel: Fast Fourier Transform (FFT)Documento24 pagineExcel: Fast Fourier Transform (FFT)fabrcadNessuna valutazione finora

- Scheda 6 Mixer PDFDocumento11 pagineScheda 6 Mixer PDFFibro_Nessuna valutazione finora

- L'amplificatore PDFDocumento4 pagineL'amplificatore PDFMassimo PenninoNessuna valutazione finora

- Mixer SimulazioniDocumento11 pagineMixer SimulazioniCarlo PalumboNessuna valutazione finora

- Come Costruire Un ThereminDocumento6 pagineCome Costruire Un ThereminfabioboogNessuna valutazione finora

- ElettroacusticaDocumento13 pagineElettroacusticaFabio Luigi RuggieroNessuna valutazione finora

- Modulazione FMDocumento41 pagineModulazione FMPiergio FerraraNessuna valutazione finora

- Elettroacustica SintesiDocumento25 pagineElettroacustica SintesiElisa BonomoNessuna valutazione finora

- Teoria Dei FiltriDocumento13 pagineTeoria Dei FiltriMey VaioNessuna valutazione finora

- Preamplificatore Hi-Fi Stereo A ValvoleDocumento23 paginePreamplificatore Hi-Fi Stereo A Valvoleromanbun100% (3)

- Cavita ForemDocumento5 pagineCavita ForemLorenzoNessuna valutazione finora

- InformaticaDocumento6 pagineInformaticaElena PetrucciNessuna valutazione finora

- ALPHA RAY Manual ItalianoDocumento23 pagineALPHA RAY Manual ItalianofpacofNessuna valutazione finora

- 2 SintesiDocumento8 pagine2 SintesiGiona VintiNessuna valutazione finora

- Università Degli Studi Di Firenze: PLL: Anello Ad Aggancio Di FaseDocumento10 pagineUniversità Degli Studi Di Firenze: PLL: Anello Ad Aggancio Di FaseLuigi ReveruzziNessuna valutazione finora

- Conversione Analogico DigitaleDocumento24 pagineConversione Analogico DigitalePaolo MarzocchiNessuna valutazione finora

- Filtri PassiviDocumento7 pagineFiltri PassivicalailNessuna valutazione finora

- Analizzatore SPETTRO1498876110Documento4 pagineAnalizzatore SPETTRO1498876110Riccardone PeperoneNessuna valutazione finora

- Contatore NumericoDocumento15 pagineContatore NumericolebesgueNessuna valutazione finora

- Fondamenti Di Audio Digitale PDFDocumento16 pagineFondamenti Di Audio Digitale PDFhaknamNessuna valutazione finora

- Ardizzon FrancescoDocumento3 pagineArdizzon FrancescoFrancesco ArdizzonNessuna valutazione finora

- Fondamenti Di TelecomunicazioniDocumento13 pagineFondamenti Di TelecomunicazioniGiuseppe Maria VentimigliaNessuna valutazione finora

- Trasmettitore FM Stereo Con LCDocumento22 pagineTrasmettitore FM Stereo Con LCluihackerNessuna valutazione finora

- Analizzatori Di SpettroDocumento218 pagineAnalizzatori Di SpettroMarco SIMONENessuna valutazione finora

- Appunti Di ElettronicaDocumento390 pagineAppunti Di ElettronicaLuigi Ottaviani100% (1)

- 1 CampionamentoDocumento31 pagine1 CampionamentoGiuseppeLetoIoCantoNessuna valutazione finora

- Filtri AttiviDocumento13 pagineFiltri Attivialeman87Nessuna valutazione finora

- PLL e Fine Tuning CircuitDocumento42 paginePLL e Fine Tuning Circuitmanuel_papaNessuna valutazione finora

- 01-Filtri RLC e RisonanzaDocumento31 pagine01-Filtri RLC e RisonanzaFilippo CastelliNessuna valutazione finora

- 2009-scuolaestiva-AMPLIFICATORI OPERAZIONALIDocumento56 pagine2009-scuolaestiva-AMPLIFICATORI OPERAZIONALIPaolo ScaliaNessuna valutazione finora

- Sangean Versus DegenDocumento3 pagineSangean Versus DegenPaolo BertorelloNessuna valutazione finora

- SRE Oscillatore Modulato Part 8Documento5 pagineSRE Oscillatore Modulato Part 8PropostiExcelNessuna valutazione finora

- Appunti Sui Ricevitori FMDocumento17 pagineAppunti Sui Ricevitori FMDavideMaruiMedasNessuna valutazione finora

- Lezione 6Documento62 pagineLezione 6Gerardo LauroNessuna valutazione finora

- 2.analisi in Frequenza Di SegnaliDocumento9 pagine2.analisi in Frequenza Di SegnaliLeonardo RomorNessuna valutazione finora

- Va THDDocumento33 pagineVa THDfarmashNessuna valutazione finora

- SDR # Guida Rapida PDFDocumento11 pagineSDR # Guida Rapida PDFEnnio D'OnofrioNessuna valutazione finora

- Preamplificatore Hi-Fi Stereo A Valvole PDFDocumento23 paginePreamplificatore Hi-Fi Stereo A Valvole PDFebonafedeNessuna valutazione finora

- Ft-991a Om Ita Eh067m350 1705F-CS PDFDocumento152 pagineFt-991a Om Ita Eh067m350 1705F-CS PDFfrancescoNessuna valutazione finora

- Function Generator With XR2206 (VCO) - Language: ItalianDocumento15 pagineFunction Generator With XR2206 (VCO) - Language: ItalianAndonio Gonde100% (1)

- 4 MidiDocumento4 pagine4 MidiGiona VintiNessuna valutazione finora

- Conversione Analogico DigitaleDocumento16 pagineConversione Analogico Digitalestefano vanniNessuna valutazione finora

- Prova Pratica 2 OscilloscopioDocumento30 pagineProva Pratica 2 OscilloscopiobarrakkuNessuna valutazione finora

- (Elettronica) - Ingegneria Del Suono - Capitolo 5. Equalizzatori e FiltriDocumento14 pagine(Elettronica) - Ingegneria Del Suono - Capitolo 5. Equalizzatori e Filtrisalvatore_livecchi100% (1)

- Filtri CON RLDocumento8 pagineFiltri CON RLFilippo CastelliNessuna valutazione finora

- Uso Dell'OscilloscopioDocumento5 pagineUso Dell'OscilloscopioAlessandro NeriNessuna valutazione finora

- PLL Per RadioamatoriDocumento34 paginePLL Per Radioamatoricyber5tar85Nessuna valutazione finora

- 4 - Esame UT - Parte Quarta - Strumenti UT - 34 (Modalità Compatibilità)Documento34 pagine4 - Esame UT - Parte Quarta - Strumenti UT - 34 (Modalità Compatibilità)isacco89Nessuna valutazione finora

- 1 - Sistemi Elettronici A Radio-Frequenza (PLL 1 ORDINE) - 4Documento6 pagine1 - Sistemi Elettronici A Radio-Frequenza (PLL 1 ORDINE) - 4sascia_1775Nessuna valutazione finora

- DI SCIPIO, Agostino - Modi Di Interferenza 3Documento8 pagineDI SCIPIO, Agostino - Modi Di Interferenza 3tomasnomasnomastomasNessuna valutazione finora

- Impulse Response e nuovi sistemi di emulazione applicati all'amplificazione per chitarra elettricaDa EverandImpulse Response e nuovi sistemi di emulazione applicati all'amplificazione per chitarra elettricaNessuna valutazione finora

- Riduzione del rumore: Miglioramento della chiarezza, tecniche avanzate per la riduzione del rumore nella visione artificialeDa EverandRiduzione del rumore: Miglioramento della chiarezza, tecniche avanzate per la riduzione del rumore nella visione artificialeNessuna valutazione finora

- Kuehne Horst - Il Libro Dei Circuiti Hi-Fi PDFDocumento82 pagineKuehne Horst - Il Libro Dei Circuiti Hi-Fi PDFSalvo Skiffy SapienzaNessuna valutazione finora

- Kuehne Horst - Il Libro Dei Circuiti Hi-Fi PDFDocumento82 pagineKuehne Horst - Il Libro Dei Circuiti Hi-Fi PDFSalvo Skiffy SapienzaNessuna valutazione finora

- Elettronica 2 - DAC Con Rete Di Tipo R-2RDocumento3 pagineElettronica 2 - DAC Con Rete Di Tipo R-2RSalvo Skiffy SapienzaNessuna valutazione finora

- Porte Logiche Con Famiglie LogicheDocumento2 paginePorte Logiche Con Famiglie LogicheSalvo Skiffy SapienzaNessuna valutazione finora

- EserciziDocumento7 pagineEserciziSalvo Skiffy SapienzaNessuna valutazione finora

- Orali Elettronica DigitaleDocumento1 paginaOrali Elettronica DigitaleSalvo Skiffy SapienzaNessuna valutazione finora