Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Dic Lec 03 Circuits v01

Caricato da

OPTICALMIMOOFDMTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Dic Lec 03 Circuits v01

Caricato da

OPTICALMIMOOFDMCopyright:

Formati disponibili

ن ا ْلعِْلِم إِاَّل قَلِ ًيلِ وما أُوتِيتم

م

8 December 2019 1441 الثان

ربيع ي11

َ ُْ ََ

Digital IC Design

Lecture 03

Basic CMOS Circuits

Dr. Hesham A. Omran

Integrated Circuits Laboratory (ICL)

Electronics and Communications Eng. Dept.

Faculty of Engineering

Ain Shams University

This lecture is mainly based on “CMOS VLSI Design”, 4th edition, by N. Weste and D. Harris and

its accompanying lecture notes

MOSFET

❑ MOSFET: Metal Oxide Semiconductor Field Effect Transistor

❑ Four terminals: gate, source, drain, body (bulk)

❑ NMOS body is usually tied to the lowest potential (VSS, ground, 0V)

❑ PMOS body is usually tied to the highest potential (VDD, power)

▪ VDD is scaled down: 5, 3.3, 2.5, 1.8, 1.5, 1.2, 1.0, …

❑ The gate controls the flow of current between the source and drain

03: Basic CMOS Circuits 2

Transistor as a Switch

❑ NMOS

▪ Gate HIGH: Switch closed (ON)

▪ Gate LOW: Switch open (OFF)

❑ PMOS

▪ Gate LOW: Switch closed (ON)

▪ Gate HIGH: Switch open (OFF)

03: Basic CMOS Circuits 3

CMOS Inverter

❑ Ideally, there is no static (idle) power consumption

03: Basic CMOS Circuits 4

CMOS NAND Gate

❑ Rule of Conduction Complements

▪ Pull-up network is complement of pull-down

▪ Parallel -> series, series -> parallel

PDN PUN

Bubble pushing with

DeMorgan’s law

03: Basic CMOS Circuits 5

CMOS NOR Gate

❑ Rule of Conduction Complements

▪ Pull-up network is complement of pull-down

▪ Parallel -> series, series -> parallel

PDN PUN

Bubble pushing with

DeMorgan’s law

03: Basic CMOS Circuits 6

General Static CMOS Gate

❑ Crowbar (contention) is usually an unwanted condition

03: Basic CMOS Circuits 7

AND-OR-INVERT-22 (AOI22)

❑ An example of a complex logic function in a single stage (8 Ts)

❑ The wrong way of doing it (20 Ts)

03: Basic CMOS Circuits 8

Quiz

❑ What is the name of this gate?

(a) AOI31 (b) OAI33 (c) OAI31

A

B

C D

Y

D

A B C

03: Basic CMOS Circuits 9

Pass Transistors

❑ NMOS: Strong ‘0’ but Weak ‘1’

▪ That’s why we use it in the pull-down network

❑ PMOS: Strong ‘1’ but Weak ‘0’

▪ That’s why we use it in the pull-up network

03: Basic CMOS Circuits 10

Transmission Gate

❑ Strong ‘0’ and ‘1’ (if the input is strong!)

❑ Simple, but non-restoring (noisy/degraded input passed to output)

03: Basic CMOS Circuits 11

Multiplexer

❑ Non-restoring mux

❑ Restoring mux (where have we seen this schematic before?)

❑ Multiplexers are usually preferred over tristate busses (why?).

03: Basic CMOS Circuits 12

Level sensitive D-latch

❑ CLK = 1: transparent

❑ CLK = 0: hold current state

❑ How do we get a negative latch?

03: Basic CMOS Circuits 13

Master-Slave Edge-Triggered D Flip-Flop

❑ Negative latch (master) + positive latch (slave)

❑ Register: A collection of D flip-flops sharing a common clock

03: Basic CMOS Circuits 14

Thank you!

03: Basic CMOS Circuits 15

Potrebbero piacerti anche

- Saldatura di circuiti elettronici: Guida per principianti e +Da EverandSaldatura di circuiti elettronici: Guida per principianti e +Nessuna valutazione finora

- Lezione 16Documento31 pagineLezione 16Gerardo LauroNessuna valutazione finora

- Orali Elettronica DigitaleDocumento1 paginaOrali Elettronica DigitaleSalvo Skiffy SapienzaNessuna valutazione finora

- Dic Lec 07 Cap v01Documento13 pagineDic Lec 07 Cap v01OPTICALMIMOOFDMNessuna valutazione finora

- Circuiti Logichi SequenzialiDocumento44 pagineCircuiti Logichi SequenzialiAndrea BaroneNessuna valutazione finora

- Tubo DG7 32-1Documento14 pagineTubo DG7 32-1Aniello IaccarinoNessuna valutazione finora

- 5c.5cintra5cdocsprodotti5cfis5c027807 Wist02390ianDocumento44 pagine5c.5cintra5cdocsprodotti5cfis5c027807 Wist02390ianpio pippiNessuna valutazione finora

- Circuiti Di MemoriaDocumento13 pagineCircuiti Di MemoriaLuigi BarbatoNessuna valutazione finora

- Circuiti CombinatoriDocumento41 pagineCircuiti Combinatoriedo marNessuna valutazione finora

- Lezione 4Documento43 pagineLezione 4Gerardo LauroNessuna valutazione finora

- E1 Intro KirchhoffDocumento22 pagineE1 Intro KirchhoffRachele CiulliNessuna valutazione finora

- 01 IntroduzioneDocumento20 pagine01 IntroduzioneMario RaffaNessuna valutazione finora

- Dossier Tecnico SchneiderDocumento17 pagineDossier Tecnico Schneiderpeter_rungaldien100% (1)

- Calcolo Della Corrente Di CortocircuitoDocumento4 pagineCalcolo Della Corrente Di CortocircuitoFrancesco RicciNessuna valutazione finora

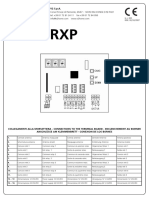

- v2 RXP InstructionsDocumento6 paginev2 RXP InstructionsandreasprovostNessuna valutazione finora

- MoSfet ElettronicaDocumento135 pagineMoSfet ElettronicaFrancesco AcunzoNessuna valutazione finora

- Vlsi 2Documento2 pagineVlsi 2Mom TimezNessuna valutazione finora

- Manuale Linear 91Documento27 pagineManuale Linear 91Zeljko Vojnic Tunic100% (1)

- Appunti Circuiti DigitaliDocumento31 pagineAppunti Circuiti DigitaliblackcoursarNessuna valutazione finora

- Riparare I PC NotebookDocumento272 pagineRiparare I PC NotebookBerserk45Nessuna valutazione finora

- Appunti TibaldiDocumento84 pagineAppunti TibaldiLuca AngeliniNessuna valutazione finora

- Educational CW Resources BookDocumento164 pagineEducational CW Resources BookLuca Di ColaNessuna valutazione finora

- ArticoloDocumento14 pagineArticoloapi-43509061Nessuna valutazione finora

- 26 Rip Alimentatori SwitchingDocumento11 pagine26 Rip Alimentatori SwitchingsalNessuna valutazione finora

- Guida Alla Misura Di Terra Chauvin Arnoux PDFDocumento32 pagineGuida Alla Misura Di Terra Chauvin Arnoux PDFJose Lenin GomezNessuna valutazione finora

- RETI TLC Lezione - Teoria - 8Documento65 pagineRETI TLC Lezione - Teoria - 8Schiano Di Cola CiroNessuna valutazione finora

- Ieee 802.3 Csma - CDDocumento12 pagineIeee 802.3 Csma - CDaleNessuna valutazione finora

- 08 Amplificatori Quasi-LineariDocumento40 pagine08 Amplificatori Quasi-LineariEricNessuna valutazione finora

- Lezione 13Documento41 pagineLezione 13Gerardo LauroNessuna valutazione finora

- Apresentacao SimoprimeDocumento56 pagineApresentacao SimoprimeTiago BorgesNessuna valutazione finora

- SpeedmasteerDocumento1 paginaSpeedmasteerjiseses540Nessuna valutazione finora

- Paka Manuale Con Scheda Monocanale AggiornatoDocumento11 paginePaka Manuale Con Scheda Monocanale AggiornatoMarioNessuna valutazione finora

- Dimmer Con PIC16F887Documento11 pagineDimmer Con PIC16F887Luis Alberto SDNessuna valutazione finora

- LTSpiceDocumento27 pagineLTSpicematteo furnariNessuna valutazione finora

- Eserciziario ElettrotecnicaDocumento127 pagineEserciziario Elettrotecnicajoe zoroNessuna valutazione finora

- 008 Lezione DSO 1Documento35 pagine008 Lezione DSO 1Gianfrancesco FlorioNessuna valutazione finora

- CKD It-En PDFDocumento4 pagineCKD It-En PDFAlberto CNessuna valutazione finora

- RG7OCR 0 - 6 1 KV PDFDocumento1 paginaRG7OCR 0 - 6 1 KV PDFenzo_60Nessuna valutazione finora

- Beginners BJTDocumento82 pagineBeginners BJTFabio Di RadoNessuna valutazione finora

- Preamplificatore AudioDocumento9 paginePreamplificatore AudioPECAFENessuna valutazione finora

- Centralina Cancello ZK2LM Manual-ITDocumento4 pagineCentralina Cancello ZK2LM Manual-ITrobyfuscoNessuna valutazione finora

- DomandeDocumento6 pagineDomandelNessuna valutazione finora

- Appunti Adc804Documento3 pagineAppunti Adc804pippoNessuna valutazione finora

- ADC0804Documento3 pagineADC0804DanielNessuna valutazione finora

- Prova Quarzi DatasheetDocumento2 pagineProva Quarzi DatasheetPeppeNessuna valutazione finora

- Sensori Al QuarzoDocumento19 pagineSensori Al QuarzoFrancoNessuna valutazione finora

- Interfacciamento Di Porte LogicheDocumento7 pagineInterfacciamento Di Porte Logichelolloso22caNessuna valutazione finora

- Relazione Laboratorio Elettronica IndustrialeDocumento5 pagineRelazione Laboratorio Elettronica IndustrialeGiovanni SferrazzaNessuna valutazione finora

- 193 - Ponte Ripetitore VHFDocumento34 pagine193 - Ponte Ripetitore VHFfernando1123Nessuna valutazione finora

- Seccionador SD6-ME6Documento13 pagineSeccionador SD6-ME6JuNessuna valutazione finora

- Scarica CondensatoreDocumento5 pagineScarica CondensatoreLorenzo ZappalaNessuna valutazione finora

- Schede Prodotti CPT PDFDocumento42 pagineSchede Prodotti CPT PDFLaurentiuNessuna valutazione finora

- Cmos TTLDocumento4 pagineCmos TTLRenny PaoloneNessuna valutazione finora

- TX Num2Documento47 pagineTX Num2bcuzwnvpdNessuna valutazione finora

- DOORINA v3.0 ITDocumento22 pagineDOORINA v3.0 ITcorpolaisla laislaNessuna valutazione finora