Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Fi Ae 11 04 11

Caricato da

francescoTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Fi Ae 11 04 11

Caricato da

francescoCopyright:

Formati disponibili

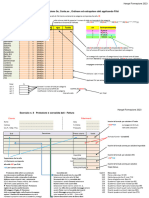

Compito N.

1

FONDAMENTI DI INFORMATICA - PROVA DI ARCHITETTURE

prova di esame del 11 aprile 2011, durata 90 minuti

————–

N.B. Negli esercizi seguenti X è la cifra meno significativa non nulla del proprio numero di matricola.

1) Si considerino una notazione binaria in virgola mobile a 16 bit con (nell’ordine da sinistra a destra) 1 bit per il segno (0=pos-

itivo), 8 bit per l’esponente rappresentato in complemento a 2 ed i rimanenti bit per la parte frazionaria della mantissa che è

normalizzata tra 1 e 2.

a) Dati i tre numeri a = 95382.21 · 1025 , b = 0.000098752 e c = 1008 · 2−130 indicare quali tra essi sono rappresentabili

nella notazione data, motivando le risposte;

b) dato il numero r rappresentato nella notazione data dalla stringa esadecimale F4XX, rappresentare nella notazione data il

numero s = r · 2−40 ;

c) dato il numero k rappresentato in eccesso 215 dalla stringa 6XD37, rappresentarlo nella notazione data;

d) calcolare l’ordine di grandezza binario e decimale dell’errore assoluto che si commette rappresentando nella notazione

data un numero dello stesso ordine di grandezza di r · 2−80 .

N.B. MOTIVARE LE RISPOSTE ILLUSTRANDO SCHEMATICAMENTE IL PROCEDIMENTO

2) Sia data la funzione booleana F (A, B, C) che assume valore vero solo quando B è falsa ed al massimo una delle altre due

variabili è vera:

a) determinare la tabella di verità della funzione F ;

b) determinare l’espressione in prima forma canonica della funzione F ;

c) determinare il circuito logico corrispondente all’espressone di cui al punto b);

d) determinare per quali valori delle variabili la funzione booleana G = F (A, B, C) AND C assume valore vero.

N.B. MOTIVARE LE RISPOSTE ILLUSTRANDO SCHEMATICAMENTE IL PROCEDIMENTO

3) Con riferimento ai bus ed alla gestione dell’I/O, indicare quali tra le seguenti affermazioni sono corrette:

A) la tastiera è un tipico esempio di dispositivo gestito tramite DMA;

B) un bus seriale con banda di 500 MB/s deve avere una frequenza di lavoro di almeno 4 GHz;

C) nel bus USB, in ciascun frame il flusso dei dati è unidirezionale;

D) un bus parallelo con 16 linee dati che lavora a 200 MHz ha una banda di 800 MB/s;

E) il bus PCI express ha una banda che cresce con il numero di dispositivi connessi;

F) il bus PCI ha una banda che cresce con il numero di dispositivi connessi;

G) l’I/O tramite DMA impegna la CPU meno dell’I/O con interrupt;

4) Con riferimento alla logica digitale e ai circuiti logici e sequenziali, indicare quali tra le seguenti affermazioni sono corrette:

A) è possibile realizzare un circuito sequenziale usando sole porte NOR;

B) qualsiasi funzione booleana può essere calcolata con un circuito realizzato con sole porte NOT;

C) una porta XOR con gli ingressi collegati tra loro si comporta come una porta NOT;

D) un multiplexer con 16 ingressi controllati può essere usato per calcolare una funzione di 4 variabili booleane;

E) un decoder a 20 ingressi ha più di un milione di uscite;

F) utilizzando coppie di DIMM con tecnologia Dual Channel e DDR vengono letti 32 byte per ciclo;

G) un chip di memoria da 256 MB può avere solo 14 piedini di indirizzo;

5) Con riferimento alle periferiche, alle unità di memoria di massa ed alla codifica dei caratteri, indicare quali tra le seguenti

affermazioni sono corrette:

A) un disco con velocità di rotazione di 6000 giri/min può avere un tempo di seek inferiore a 2 ms;

B) i tempi di accesso dei dischi sono circa un milione di volte più lunghi di quelli delle RAM;

C) per correggere errori tripli è necessario un codice con distanza di Hamming di almeno 7;

D) un codice a 16 bit con controllo di parità ha più di 30.000 codifiche valide;

E) una configurazione RAID 0 costituita da 12 dischi da 100 GB ha una capacità superiore ad 1 TB;

F) il tempo di accesso di un disco dipende dalla velocità di rotazione;

G) il tempo medio di latenza di un disco dipende esclusivamente dalla velocità di rotazione;

6) Con riferimento all’architettura della CPU alle memorie ed alle cache, indicare quali tra le seguenti affermazioni sono corrette:

A) le cache a mappa diretta sono realizzate con memorie statiche;

B) l’architettura IA-32 prevede un grande numero di registri interni visibili al programmatore;

C) l’architettura IA-64 è un’architettura RISC;

D) in una cache a mappa diretta un determinato blocco entra sempre nella stessa slot;

E) uno dei problemi che nascono con le architetture multicore è quello della condivisione della memoria;

F) nella piattaforma Intel i link PCI-express sono connessi al South Bridge;

G) la microarchitettura NetBurst prevede l’esecuzione out-of-order delle microoperazioni;

Potrebbero piacerti anche

- Z - Lezione 16Documento1 paginaZ - Lezione 16francescoNessuna valutazione finora

- Foglio 1Documento2 pagineFoglio 1francescoNessuna valutazione finora

- Foglio 4Documento2 pagineFoglio 4francescoNessuna valutazione finora

- RicevutaEsame 4Documento1 paginaRicevutaEsame 4francescoNessuna valutazione finora

- Lezione 18Documento1 paginaLezione 18francescoNessuna valutazione finora

- Lezione 19Documento1 paginaLezione 19francescoNessuna valutazione finora

- Lezione 17Documento1 paginaLezione 17francescoNessuna valutazione finora

- Z - Lezione 2Documento2 pagineZ - Lezione 2francescoNessuna valutazione finora

- C IIIb 14 15Documento21 pagineC IIIb 14 15francescoNessuna valutazione finora

- Z - Lezione 6Documento2 pagineZ - Lezione 6francescoNessuna valutazione finora

- Z - Lezione 4Documento2 pagineZ - Lezione 4francescoNessuna valutazione finora

- Z - Lezione 5Documento2 pagineZ - Lezione 5francescoNessuna valutazione finora

- Lezione 20Documento1 paginaLezione 20francescoNessuna valutazione finora

- Z - Lezione 3Documento2 pagineZ - Lezione 3francescoNessuna valutazione finora

- Z - Lezione 1Documento2 pagineZ - Lezione 1francescoNessuna valutazione finora

- Riassunto Lezione 5:04Documento3 pagineRiassunto Lezione 5:04francescoNessuna valutazione finora

- Z - Lezione 1Documento2 pagineZ - Lezione 1francescoNessuna valutazione finora

- Introduzione Al C Unità 2 - Variabili: D. Bloisi, S. Peluso, A. Pennisi, S. SalzaDocumento68 pagineIntroduzione Al C Unità 2 - Variabili: D. Bloisi, S. Peluso, A. Pennisi, S. SalzafrancescoNessuna valutazione finora

- Assegno 29 03Documento2 pagineAssegno 29 03francescoNessuna valutazione finora

- Introduzione Al C Unità 2 - Variabili: D. Bloisi, S. Peluso, A. Pennisi, S. SalzaDocumento68 pagineIntroduzione Al C Unità 2 - Variabili: D. Bloisi, S. Peluso, A. Pennisi, S. SalzafrancescoNessuna valutazione finora

- Demo CicliDocumento89 pagineDemo CiclifrancescoNessuna valutazione finora

- Riassunto Lezione 29:03:2021Documento2 pagineRiassunto Lezione 29:03:2021francescoNessuna valutazione finora

- C Iii 13 14Documento39 pagineC Iii 13 14francescoNessuna valutazione finora

- 10 C 13 14 PreprocessoreDocumento28 pagine10 C 13 14 PreprocessorefrancescoNessuna valutazione finora

- 9 C 14 15 FileDocumento37 pagine9 C 14 15 FilefrancescoNessuna valutazione finora

- Guida Di Installazione GCC: D. Bloisi, S. Peluso, A. Pennisi, S. SalzaDocumento14 pagineGuida Di Installazione GCC: D. Bloisi, S. Peluso, A. Pennisi, S. SalzafrancescoNessuna valutazione finora

- Introduzione Al C Unità 1 - Introduzione: D. Bloisi, S. Peluso, A. Pennisi, S. SalzaDocumento54 pagineIntroduzione Al C Unità 1 - Introduzione: D. Bloisi, S. Peluso, A. Pennisi, S. SalzafrancescoNessuna valutazione finora

- 12 C 13 14 Allocazione - DinamicaDocumento14 pagine12 C 13 14 Allocazione - DinamicafrancescoNessuna valutazione finora

- 11 C 13 14 Allocazione - DinamicaDocumento16 pagine11 C 13 14 Allocazione - DinamicafrancescoNessuna valutazione finora

- 9 C 14 15 File BDocumento16 pagine9 C 14 15 File BfrancescoNessuna valutazione finora

- Esercitazione 4 Mayra CayambeDocumento29 pagineEsercitazione 4 Mayra CayambeMayra CayambeNessuna valutazione finora

- Esercizi-Excel Funzione-Se-Conta-Filtri-ProtezioneDocumento2 pagineEsercizi-Excel Funzione-Se-Conta-Filtri-ProtezionezichellalauramariaNessuna valutazione finora

- Vimar Cronotermostato 16577-16577BDocumento51 pagineVimar Cronotermostato 16577-16577Bmassimo bianchiNessuna valutazione finora

- Denso SH705x OpelDocumento2 pagineDenso SH705x OpelrubenbslNessuna valutazione finora