DocumentoWAVE SHAPINGcaricato da

DocumentoWAVE SHAPINGcaricato da KavyashreeM

KavyashreeM DocumentoPDC_Notes.pdfcaricato da

DocumentoPDC_Notes.pdfcaricato da KavyashreeM

KavyashreeM Documentode1999 LPVLSI papercaricato da

Documentode1999 LPVLSI papercaricato da KavyashreeM

KavyashreeM Documentoslyw038c.pdfcaricato da

Documentoslyw038c.pdfcaricato da KavyashreeM

KavyashreeM Documentoidoc.pub_vlsi-design-interview-questions.pdfcaricato da

Documentoidoc.pub_vlsi-design-interview-questions.pdfcaricato da KavyashreeM

KavyashreeM Documentoglitch free clock multiplexer(mux) _ RTLerycaricato da

Documentoglitch free clock multiplexer(mux) _ RTLerycaricato da KavyashreeM

KavyashreeM DocumentoCH 5.pdfcaricato da

DocumentoCH 5.pdfcaricato da KavyashreeM

KavyashreeM Documentoe-2014_0.pdfcaricato da

Documentoe-2014_0.pdfcaricato da KavyashreeM

KavyashreeM DocumentoDigital_Systems_Principles_and_Applicati.pdfcaricato da

DocumentoDigital_Systems_Principles_and_Applicati.pdfcaricato da KavyashreeM

KavyashreeM DocumentoPartial_Adiabatic.pdfcaricato da

DocumentoPartial_Adiabatic.pdfcaricato da KavyashreeM

KavyashreeM DocumentoDesign_and_optimization_of_low_voltage_h.pdfcaricato da

DocumentoDesign_and_optimization_of_low_voltage_h.pdfcaricato da KavyashreeM

KavyashreeM Documento76417776-Physical-Design-Complete.pdfcaricato da

Documento76417776-Physical-Design-Complete.pdfcaricato da KavyashreeM

KavyashreeM Documento2009-11EDSSC2009caricato da

Documento2009-11EDSSC2009caricato da KavyashreeM

KavyashreeM Documento1000017819.pdfcaricato da

Documento1000017819.pdfcaricato da KavyashreeM

KavyashreeM Documentolab3_testbench_tutorial.pdfcaricato da

Documentolab3_testbench_tutorial.pdfcaricato da KavyashreeM

KavyashreeM DocumentoCummingsSNUG2002SJ_FIFO1_rev1_2caricato da

DocumentoCummingsSNUG2002SJ_FIFO1_rev1_2caricato da KavyashreeM

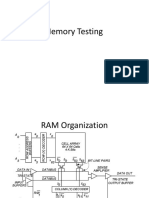

KavyashreeM DocumentoUnit4_memorytestingcaricato da

DocumentoUnit4_memorytestingcaricato da KavyashreeM

KavyashreeM DocumentoUnit4_BISTcaricato da

DocumentoUnit4_BISTcaricato da KavyashreeM

KavyashreeM Documento3145_AppB.pdfcaricato da

Documento3145_AppB.pdfcaricato da KavyashreeM

KavyashreeM Documento3145_AppF.pdfcaricato da

Documento3145_AppF.pdfcaricato da KavyashreeM

KavyashreeM Documentoperlcaricato da

Documentoperlcaricato da KavyashreeM

KavyashreeM Documento3145_AppA.pdfcaricato da

Documento3145_AppA.pdfcaricato da KavyashreeM

KavyashreeM Documentoperlcaricato da

Documentoperlcaricato da KavyashreeM

KavyashreeM DocumentoARM_AMBA3_APB.pdfcaricato da

DocumentoARM_AMBA3_APB.pdfcaricato da KavyashreeM

KavyashreeM Documentomatsuzuka2017caricato da

Documentomatsuzuka2017caricato da KavyashreeM

KavyashreeM DocumentoARM_AMBA3_APB.pdfcaricato da

DocumentoARM_AMBA3_APB.pdfcaricato da KavyashreeM

KavyashreeM Documentocapactr_inductr.pdfcaricato da

Documentocapactr_inductr.pdfcaricato da KavyashreeM

KavyashreeM DocumentoCAP & IND.pdfcaricato da

DocumentoCAP & IND.pdfcaricato da KavyashreeM

KavyashreeM Documentoedge detection.pdfcaricato da

Documentoedge detection.pdfcaricato da KavyashreeM

KavyashreeM DocumentoDadoria2018_Article_PerformanceEvaluationOfDominoLcaricato da

DocumentoDadoria2018_Article_PerformanceEvaluationOfDominoLcaricato da KavyashreeM

KavyashreeM Documento001-course-outline.pptcaricato da

Documento001-course-outline.pptcaricato da KavyashreeM

KavyashreeM DocumentoPartial_Adiabaticcaricato da

DocumentoPartial_Adiabaticcaricato da KavyashreeM

KavyashreeM DocumentoF19_L1_Op_Amp.pptxcaricato da

DocumentoF19_L1_Op_Amp.pptxcaricato da KavyashreeM

KavyashreeM DocumentoF19_L1_Op_Amp (1).pptxcaricato da

DocumentoF19_L1_Op_Amp (1).pptxcaricato da KavyashreeM

KavyashreeM DocumentoDASHBOARDcaricato da

DocumentoDASHBOARDcaricato da KavyashreeM

KavyashreeM Documentopurchase-ordercaricato da

Documentopurchase-ordercaricato da KavyashreeM

KavyashreeM DocumentoAnalog lab cadence procedure.pdfcaricato da

DocumentoAnalog lab cadence procedure.pdfcaricato da KavyashreeM

KavyashreeM DocumentoAnalog lab cadence procedure.pdfcaricato da

DocumentoAnalog lab cadence procedure.pdfcaricato da KavyashreeM

KavyashreeM DocumentoIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H.pdfcaricato da

DocumentoIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H.pdfcaricato da KavyashreeM

KavyashreeM DocumentoIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.Hcaricato da

DocumentoIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.Hcaricato da KavyashreeM

KavyashreeM Documento3 ECE - PDC UNIT - I.pdfcaricato da

Documento3 ECE - PDC UNIT - I.pdfcaricato da KavyashreeM

KavyashreeM DocumentoFSM verilog.pdfcaricato da

DocumentoFSM verilog.pdfcaricato da KavyashreeM

KavyashreeM DocumentoBubble sort.docxcaricato da

DocumentoBubble sort.docxcaricato da KavyashreeM

KavyashreeM DocumentoBubble sort.docxcaricato da

DocumentoBubble sort.docxcaricato da KavyashreeM

KavyashreeM DocumentoDesign_of_a_High_Speed_Adder (1).pdfcaricato da

DocumentoDesign_of_a_High_Speed_Adder (1).pdfcaricato da KavyashreeM

KavyashreeM DocumentoDesign_of_Parallel_Prefix_Adders.pdfcaricato da

DocumentoDesign_of_Parallel_Prefix_Adders.pdfcaricato da KavyashreeM

KavyashreeM DocumentoLOWPOWEREFFICIENTDADDAMULTIPLIER.pdfcaricato da

DocumentoLOWPOWEREFFICIENTDADDAMULTIPLIER.pdfcaricato da KavyashreeM

KavyashreeM DocumentoLOWPOWEREFFICIENTDADDAMULTIPLIERcaricato da

DocumentoLOWPOWEREFFICIENTDADDAMULTIPLIERcaricato da KavyashreeM

KavyashreeM DocumentoECE645_lecture3_fast_adders (1).pptcaricato da

DocumentoECE645_lecture3_fast_adders (1).pptcaricato da KavyashreeM

KavyashreeM

Documenti di Didattica

Documenti di Professioni

Documenti di Cultura