Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Summary: Latches: Flip-Flops

Caricato da

saepul anwarTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Summary: Latches: Flip-Flops

Caricato da

saepul anwarCopyright:

Formati disponibili

Summary : Latches

• A sequential circuit has memory. It may respond differently to the

same inputs, depending on its current state.

• Memories can be created by making circuits with feedback.

– Latches are the simplest memory units, storing individual bits.

– It’s difficult to control the timing of latches in a larger circuit.

• We’ll improve upon latches with flip-flops, which change state only at

well-defined times. We will then use flip-flops to build all of our

sequential circuits.

October 16, 2002 Flip-flops 1

An SR latch with a control input

• Here is an SR latch with a control input C.

C S R S’ R’ Q

0 x x 1 1 No change

1 0 0 1 1 No change

1 0 1 1 0 0 (reset)

1 1 0 0 1 1 (set)

1 1 1 0 0 Avoid!

• Notice the hierarchical design!

– The dotted blue box is the S’R’ latch.

– The additional NAND gates are simply used to generate the correct

inputs for the S’R’ latch.

• The control input acts just like an enable.

October 16, 2002 Flip-flops 2

D latch

• Finally, a D latch is based on an S’R’ latch. The additional gates generate

the S’ and R’ signals, based on inputs D (“data”) and C (“control”).

– When C = 0, S’ and R’ are both 1, so the state Q does not change.

– When C = 1, the latch output Q will equal the input D.

• No more messing with one input for set and another input for reset!

C D Q

0 x No change

1 0 0

1 1 1

• Also, this latch has no “bad” input combinations to avoid. Any of the

four possible assignments to C and D are valid.

October 16, 2002 Flip-flops 3

Sequential circuits and state diagrams

• To describe combinational circuits, we used Boolean expressions and

truth tables. With sequential circuits, we use another form called a

state diagram.

• We draw one node for each state that the circuit can be in. Latches

have only two states: Q=0 and Q=1.

• Arrows between nodes are labeled with “input/output” and indicate how

the circuit changes states and what its outputs are. In this case the

state and the output are the same.

• If you’ve taken CS273, this is basically the same as the finite state

automata you saw there.

• Here’s a state diagram for a D latch with inputs D and C.

0x/0 0x/1

11/1

Q=0 Q=1

10/0

October 16, 2002 Flip-flops 4

Using latches in real life

• We can connect some latches, acting as memory, to an ALU.

+1 S

ALU G

X

D

Q Latches

C

• Let’s say these latches contain some value that we want to increment.

– The ALU should read the current latch value.

– It applies the “G = X + 1” operation.

– The incremented value is stored back into the latches.

• At this point, we have to stop the cycle, so the latch value doesn’t get

incremented again by accident.

• One convenient way to break the loop is to disable the latches.

October 16, 2002 Flip-flops 5

The problem with latches

+1 S

ALU G

X

D

Q Latches

C

• The problem is exactly when to disable the latches. You have to wait

long enough for the ALU to produce its output, but no longer.

– But different ALU operations have different delays. For instance,

arithmetic operations might go through an adder, whereas logical

operations don’t.

– Changing the ALU implementation, such as using a carry-lookahead

adder instead of a ripple-carry adder, also affects the delay.

• In general, it’s very difficult to know how long operations take, and how

long latches should be enabled for.

October 16, 2002 Flip-flops 6

Flip-flops

• We’ll address some of the shortcomings of latches by using

them to build flip-flops.

– Adding a “clock” signal helps circuits synchronize their

actions.

– We’ll also need to disable memory units quickly.

October 16, 2002 Flip-flops 7

Making latches work right

• Our example used latches as memory for an ALU.

– Let’s say there are four latches initially storing 0000.

– We want to use an ALU to increment that value to 0001.

• Normally the latches should be disabled, to prevent unwanted data

from being accidentally stored.

– In our example, the ALU can read the current latch contents, 0000,

and compute their increment, 0001.

– But the new value cannot be stored back while the latch is disabled.

+1 S

ALU G

X

0001

0000

D

Q Latches

C 0

October 16, 2002 Flip-flops 8

Writing to the latches

• After the ALU has finished its increment operation, the latch can be

enabled, and the updated value is stored.

+1 S

ALU G

X

0001

0001

D

Q Latches

C 1

• The latch must be quickly disabled again, before the ALU has a chance

to read the new value 0001 and produce a new result 0010.

+1 S

ALU G

X

0010

0001

D

Q Latches

C 0

October 16, 2002 Flip-flops 9

Two main issues

• So to use latches correctly within a circuit, we have to:

– Keep the latches disabled until new values are ready to be stored.

– Enable the latches just long enough for the update to occur.

• There are two main issues we need to address:

How do we know exactly when the new values are ready?

We’ll add another signal to our circuit. When this new

signal becomes 1, the latches will know that the ALU

computation has completed and data is ready to be stored.

How can we enable and then quickly disable the latches?

This can be done by combining latches together in a

special way, to form what are called flip-flops.

October 16, 2002 Flip-flops 10

Clocks and synchronization

• A clock is a special device that whose output continuously alternates

between 0 and 1.

clock period

• The time it takes the clock to change from 1 to 0 and back to 1 is called

the clock period, or clock cycle time.

• The clock frequency is the inverse of the clock period. The unit of

measurement for frequency is the hertz.

• Clocks are often used to synchronize circuits.

– They generate a repeating, predictable pattern of 0s and 1s that

can trigger certain events in a circuit, such as writing to a latch.

– If several circuits share a common clock signal, they can coordinate

their actions with respect to one another.

• This is similar to how humans use real clocks for synchronization.

October 16, 2002 Flip-flops 11

Synchronizing our example

• We can use a clock to synchronize our latches with the ALU.

– The clock signal is connected to the latch control input C.

– The clock controls the latches. When it becomes 1, the latches will

be enabled for writing.

+1 S

ALU G

X

D

Q Latches

C

• The clock period must be set appropriately for the ALU.

– It should not be too short. Otherwise, the latches will start writing

before the ALU operation has finished.

– It should not be too long either. Otherwise, the ALU might produce

a new result that will accidentally get stored, as we saw before.

• The faster the ALU runs, the shorter the clock period can be.

October 16, 2002 Flip-flops 12

More about clocks

• Clocks are used extensively in computer architecture.

• All processors run with an internal clock.

– Modern chips run at frequencies up to 2.8 GHz.

– This works out to a cycle time as little as 0.36 ns!

• Memory modules are often rated by their clock speeds

too—examples include “PC133” and “PC800” memory.

• Be careful...higher frequencies do not always mean faster machines!

– You also have to consider how much work is actually being done

during each clock cycle.

– How much stuff can really get done in just 0.36 ns?

– Take CS232.

October 16, 2002 Flip-flops 13

Flip-flops

• The second issue was how to enable a latch for just an instant.

• Here is the internal structure of a D flip-flop.

– The flip-flop inputs are C and D, and the outputs are Q and Q’.

– The D latch on the left is the master, while the SR latch on the

right is called the slave.

• Note the layout here.

– The flip-flop input D is connected directly to the master latch.

– The master latch output goes to the slave.

– The flip-flop outputs come directly from the slave latch.

October 16, 2002 Flip-flops 14

D flip-flops when C=0

• The D flip-flop’s control input C enables either the D latch or the SR

latch, but not both.

• When C = 0:

– The master latch is enabled, and it monitors the flip-flop input D.

Whenever D changes, the master’s output changes too.

– The slave is disabled, so the D latch output has no effect on it.

Thus, the slave just maintains the flip-flop’s current state.

October 16, 2002 Flip-flops 15

D flip-flops when C=1

• As soon as C becomes 1,

– The master is disabled. Its output will be the last D input value seen

just before C became 1.

– Any subsequent changes to the D input while C = 1 have no effect on

the master latch, which is now disabled.

– The slave latch is enabled. Its state changes to reflect the master’s

output, which again is the D input value from right when C became 1.

October 16, 2002 Flip-flops 16

Positive edge triggering

• This is called a positive edge-triggered flip-flop.

– The flip-flop output Q changes only after the positive edge of C.

– The change is based on the flip-flop input values that were present

right at the positive edge of the clock signal.

• The D flip-flop’s behavior is similar to that of a D latch except for the

positive edge-triggered nature, which is not explicit in this table.

C D Q

0 x No change

1 0 0 (reset)

1 1 1 (set)

October 16, 2002 Flip-flops 17

Direct inputs

• One last thing to worry about… what is the starting value of Q?

• We could set the initial value synchronously, at the next positive clock

edge, but this actually makes circuit design more difficult.

• Instead, most flip-flops provide direct, or asynchronous, inputs that let

you immediately set or clear the state.

– You would “reset” the circuit once, to initialize the flip-flops.

– The circuit would then begin its regular, synchronous operation.

• Here is a LogicWorks D flip-flop with active-low direct inputs.

S’ R’ C D Q

0 0 x x Avoid!

0 1 x x 1 (set) Direct inputs to set or

1 0 x x 0 (reset) reset the flip-flop

1 1 0 x No change S’R’ = 11 for “normal”

1 1 1 0 0 (reset) operation of the D

1 1 1 1 1 (set) flip-flop

October 16, 2002 Flip-flops 18

Our example with flip-flops

• We can use the flip-flops’ direct inputs to initialize them to 0000.

+1 S

ALU G C

X

0000 Q0

D

Q Flip-flops G0

C

• During the clock cycle, the ALU outputs 0001, but this does not affect

the flip-flops yet.

+1 S

ALU G C

X

0001

0000 Q0

D

Q Flip-flops G0

C

October 16, 2002 Flip-flops 19

Example continued

• The ALU output is copied into the flip-flops at the next positive edge

of the clock signal.

+1 S

ALU G C

X

0001

0001 Q0

D

Q Flip-flops G0

C

• The flip-flops automatically “shut off,” and no new data can be written

until the next positive clock edge... even though the ALU produces a

new output.

+1 S

ALU G C

X

0001

0001 Q0

D

Q Flip-flops G0

C

October 16, 2002 Flip-flops 20

Flip-flop variations

• We can make different versions of flip-flops based on the D flip-flop,

just like we made different latches based on the S’R’ latch.

• A JK flip-flop has inputs that act like S and R, but the inputs JK=11 are

used to complement the flip-flop’s current state.

C J K Qnext

0 x x No change

1 0 0 No change

1 0 1 0 (reset)

1 1 0 1 (set)

1 1 1 Q’current

• A T flip-flop can only maintain or complement its current state.

C T Qnext

0 x No change

1 0 No change

1 1 Q’current

October 16, 2002 Flip-flops 21

Characteristic tables

• The tables that we’ve made so far are

called characteristic tables. D Q(t+1) Operation

– They show the next state Q(t+1) 0 0 Reset

in terms of the current state Q(t) 1 1 Set

and the inputs.

– For simplicity, the control input C

is not usually listed.

J K Q(t+1) Operation

– Again, these tables don’t indicate 0 0 Q(t) No change

the positive edge-triggered

0 1 0 Reset

behavior of the flip-flops that

1 0 1 Set

we’ll be using.

1 1 Q’(t) Complement

T Q(t+1) Operation

0 Q(t) No change

1 Q’(t) Complement

October 16, 2002 Flip-flops 22

Characteristic equations

• We can also write characteristic equations, where the next state Q(t+1)

is defined in terms of the current state Q(t) and inputs.

D Q(t+1) Operation

0 0 Reset Q(t+1) = D

1 1 Set

J K Q(t+1) Operation

0 0 Q(t) No change

0 1 0 Reset Q(t+1) = K’Q(t) + JQ’(t)

1 0 1 Set

1 1 Q’(t) Complement

T Q(t+1) Operation

Q(t+1) = T’Q(t) + TQ’(t)

0 Q(t) No change

= T Q(t)

1 Q’(t) Complement

October 16, 2002 Flip-flops 23

Flip flop timing diagrams

• “Present state” and “next state” are relative terms.

• In the example JK flip-flop timing diagram on the left, you can see that

at the first positive clock edge, J=1, K=1 and Q(1) = 1.

• We can use this information to find the “next” state, Q(2) = Q(1)’.

• Q(2) appears right after the first positive clock edge, as shown on the

right. It will not change again until after the second clock edge.

1 2 3 4 1 2 3 4

C C

J J

K K

Q Q

These values at clock cycle 1... … determine the “next” Q

October 16, 2002 Flip-flops 24

“Present” and “next” are relative

• Similarly, the values of J, K and Q at the second positive clock edge can

be used to find the value of Q during the third clock cycle.

• When we do this, Q(2) is now referred to as the “present” state, and

Q(3) is now the “next” state.

1 2 3 4 1 2 3 4

C C

J J

K K

Q Q

October 16, 2002 Flip-flops 25

Positive edge triggered

• One final point to repeat: the flip-flop outputs are affected only by the

input values at the positive edge.

– In the diagram below, K changes rapidly between the second and

third positive edges.

– But it’s only the input values at the third clock edge (K=1, and J=0

and Q=1) that affect the next state, so here Q changes to 0.

• This is a fairly simple timing model. In real life there are “setup times”

and “hold times” to worry about as well, to account for internal and

external delays.

1 2 3 4

C

J

October 16, 2002 Flip-flops 26

Summary

• To use memory in a larger circuit, we need to:

– Keep the latches disabled until new values are ready to be stored.

– Enable the latches just long enough for the update to occur.

• A clock signal is used to synchronize circuits. The cycle time reflects

how long combinational operations take.

• Flip-flops further restrict the memory writing interval, to just the

positive edge of the clock signal.

– This ensures that memory is updated only once per clock cycle.

– There are several different kinds of flip-flops, but they all serve

the same basic purpose of storing bits.

• Next week we’ll talk about how to analyze and design sequential circuits

that use flip-flops as memory.

October 16, 2002 Flip-flops 27

Potrebbero piacerti anche

- Op Amp Differential Amplifier Circuit Age SubtractorDocumento9 pagineOp Amp Differential Amplifier Circuit Age SubtractorSai Arja SaiNessuna valutazione finora

- Transistor Switching and Sequential CircuitsDa EverandTransistor Switching and Sequential CircuitsValutazione: 5 su 5 stelle5/5 (1)

- DC Motor Speed Controller Using IC 555 TimerDocumento8 pagineDC Motor Speed Controller Using IC 555 Timerfarazpayoneer21Nessuna valutazione finora

- Flip FlopsDocumento28 pagineFlip FlopssreekarscribdNessuna valutazione finora

- Sequential Circuits: Cpe 443/L Advanced Logic CircuitsDocumento35 pagineSequential Circuits: Cpe 443/L Advanced Logic CircuitsKent Genzen Corpus100% (1)

- Design of A Discrete BJT Operational AmplifierDocumento6 pagineDesign of A Discrete BJT Operational Amplifierjonesy5000Nessuna valutazione finora

- NE555 - Datasheet Timer PDFDocumento7 pagineNE555 - Datasheet Timer PDFpancho8gtzNessuna valutazione finora

- October 15, 2003 Flip-Flops 1Documento25 pagineOctober 15, 2003 Flip-Flops 1B Dheepak BalaNessuna valutazione finora

- Understanding Flip-FlopsDocumento35 pagineUnderstanding Flip-FlopsKaustav MitraNessuna valutazione finora

- Ch05-Part 1Documento28 pagineCh05-Part 1hezzat964Nessuna valutazione finora

- EE-221 Chap07 Part-01Documento42 pagineEE-221 Chap07 Part-01AliNessuna valutazione finora

- Digital Logic Circuit Design Experiemnet 10Documento7 pagineDigital Logic Circuit Design Experiemnet 10fahadNessuna valutazione finora

- Лекция По Узлам с Памятью 25 04 2022 PDFDocumento39 pagineЛекция По Узлам с Памятью 25 04 2022 PDFPoliakovNessuna valutazione finora

- 1 Unit 2 Flip FlopsDocumento23 pagine1 Unit 2 Flip FlopsShivangi SharmaNessuna valutazione finora

- EECS 150 - Components and Design Techniques for Digital SystemsDocumento41 pagineEECS 150 - Components and Design Techniques for Digital Systemsrifqi sutrisnoNessuna valutazione finora

- VHDLDocumento57 pagineVHDLAkshta KaushalNessuna valutazione finora

- LDICA Unit 5 PDFDocumento80 pagineLDICA Unit 5 PDFbhanumanuNessuna valutazione finora

- Introduction To Sequential Circuits: by Dr. Irshad Ahmad AnsariDocumento60 pagineIntroduction To Sequential Circuits: by Dr. Irshad Ahmad AnsariShubham KhandelwalNessuna valutazione finora

- Computer Architecture I: Digital DesignDocumento39 pagineComputer Architecture I: Digital DesignAli BalochNessuna valutazione finora

- Sequential Circuits: by Dr. Nermeen TalaatDocumento36 pagineSequential Circuits: by Dr. Nermeen TalaatahmedNessuna valutazione finora

- LD5 Mano Ch5Documento37 pagineLD5 Mano Ch5Amr HefnyNessuna valutazione finora

- Digital Logic Design Sequential CircuitsDocumento35 pagineDigital Logic Design Sequential CircuitsV Iv Ek ParekhNessuna valutazione finora

- Chapter 6 - Sequential Logics (EEEg4302) 2Documento31 pagineChapter 6 - Sequential Logics (EEEg4302) 2Toli fiqeeNessuna valutazione finora

- ITBP205 Digital Design and Computer Organization Memory ElementsDocumento20 pagineITBP205 Digital Design and Computer Organization Memory ElementsJawad AadiNessuna valutazione finora

- Chapter 5 Sequential CircuitsDocumento60 pagineChapter 5 Sequential CircuitsfireworkNessuna valutazione finora

- Introduction To Sequential Circuits: by Dr. Irshad Ahmad AnsariDocumento77 pagineIntroduction To Sequential Circuits: by Dr. Irshad Ahmad AnsariPrajith ReddyNessuna valutazione finora

- SEQUENTIAL LOGIC CIRCUITSDocumento34 pagineSEQUENTIAL LOGIC CIRCUITSibraheembello31Nessuna valutazione finora

- Sequential Circuits Explained: Latches, Flip-Flops, and Their ApplicationsDocumento35 pagineSequential Circuits Explained: Latches, Flip-Flops, and Their Applicationsعلوم حاسبNessuna valutazione finora

- Flip FlopDocumento29 pagineFlip FlopAndleeb juttiNessuna valutazione finora

- Combinational and SequentialCircuitsDocumento40 pagineCombinational and SequentialCircuitsbrieabrhaNessuna valutazione finora

- Synchronous Sequential Logic Lecture Flip FlopsDocumento20 pagineSynchronous Sequential Logic Lecture Flip FlopsWalrus ProduceNessuna valutazione finora

- Lecture05 Sequential LogicDocumento29 pagineLecture05 Sequential Logicusheelike666Nessuna valutazione finora

- FALLSEM2021-22 SWE1003 ETH VL2021220100826 Reference Material I 27-08-2021 Seq-Ckt2Documento108 pagineFALLSEM2021-22 SWE1003 ETH VL2021220100826 Reference Material I 27-08-2021 Seq-Ckt2Dhanwanth JPNessuna valutazione finora

- Ece5530 CH07Documento36 pagineEce5530 CH07Shubham YadavNessuna valutazione finora

- Digital Fundamentals CHAPTER 7 Latches FDocumento39 pagineDigital Fundamentals CHAPTER 7 Latches FNurul Syifa Bt EdrussalamNessuna valutazione finora

- 8 Sequential LogicDocumento76 pagine8 Sequential LogicTin TranNessuna valutazione finora

- Khaled Moussa-Lab Report 1Documento7 pagineKhaled Moussa-Lab Report 1khaledmoussa589Nessuna valutazione finora

- Chapter 5 - Sequential Circuits: Logic and Computer Design FundamentalsDocumento20 pagineChapter 5 - Sequential Circuits: Logic and Computer Design FundamentalsMuhammad MuaviaNessuna valutazione finora

- Flip Flops: Name - Marada Shamita Experiment No. - 9 Roll No. - 2101116 Date - 10Documento9 pagineFlip Flops: Name - Marada Shamita Experiment No. - 9 Roll No. - 2101116 Date - 10MOHIT MISHRANessuna valutazione finora

- Lecture 1Documento35 pagineLecture 1زياد عبدالله عبدالحميدNessuna valutazione finora

- Basic NAND S-R Latch CircuitDocumento25 pagineBasic NAND S-R Latch CircuitredionxhepaNessuna valutazione finora

- DL Unit 6 - Flip-FlopsDocumento32 pagineDL Unit 6 - Flip-Flopsyunavdc642Nessuna valutazione finora

- State and Finite State Machines: Hakim Weatherspoon CS 3410, Spring 2013Documento61 pagineState and Finite State Machines: Hakim Weatherspoon CS 3410, Spring 2013gorenganNessuna valutazione finora

- Chapter5: Synchronous Sequential Logic: Lecture2-Study Problems in Latches and Design D Flip-FlopsDocumento20 pagineChapter5: Synchronous Sequential Logic: Lecture2-Study Problems in Latches and Design D Flip-FlopsHamza RiazNessuna valutazione finora

- Lecture 06 - Sequential Logic ElementsDocumento29 pagineLecture 06 - Sequential Logic ElementsMohammed ZaitounNessuna valutazione finora

- ECE 124 Digital Circuits and Systems Assignment #6Documento4 pagineECE 124 Digital Circuits and Systems Assignment #6jahnavi thotaNessuna valutazione finora

- Basics and Overview of Flip FlopsDocumento7 pagineBasics and Overview of Flip FlopsPriyamvada VermaNessuna valutazione finora

- Bec Unit 2Documento75 pagineBec Unit 2kbkbNessuna valutazione finora

- Build Sequential Logic CircuitsDocumento31 pagineBuild Sequential Logic CircuitsNavinaash Chanthra SegaranNessuna valutazione finora

- ACTIVITY PPT Exploring Sequential CircuitsDocumento12 pagineACTIVITY PPT Exploring Sequential Circuitsks78874960% (1)

- Latches and Flip Flops CharacteristicsDocumento13 pagineLatches and Flip Flops CharacteristicsWeaam RaedNessuna valutazione finora

- Sequential Circuits: Types and Functions of Flip FlopsDocumento16 pagineSequential Circuits: Types and Functions of Flip FlopsSonam SoniNessuna valutazione finora

- Digital Electronics Sequential Circuits Design Part 1Documento14 pagineDigital Electronics Sequential Circuits Design Part 1عباس محمد عباس عبدالحسينNessuna valutazione finora

- School of Computer Science and Electronic Engineering: Level Digital Logic OperationsDocumento24 pagineSchool of Computer Science and Electronic Engineering: Level Digital Logic OperationsVlad SimizeanuNessuna valutazione finora

- 19-Sequential Circuits - Latches-19-09-2023Documento17 pagine19-Sequential Circuits - Latches-19-09-2023vanchagargNessuna valutazione finora

- Digital Logic Design Sequential Circuits: N Srikanth Prasad Assistant Professor Department of ECE +91-93 9104 9134Documento38 pagineDigital Logic Design Sequential Circuits: N Srikanth Prasad Assistant Professor Department of ECE +91-93 9104 9134nskprasad89Nessuna valutazione finora

- Lec. (3) Digital CircuitsDocumento24 pagineLec. (3) Digital CircuitsmhmedibrahimuaNessuna valutazione finora

- Digital ElectronicsDocumento34 pagineDigital ElectronicsNikhil SethNessuna valutazione finora

- L25 - Datapath Design - p1Documento46 pagineL25 - Datapath Design - p1Shanawar AliNessuna valutazione finora

- ECE 424 – Introduction to VLSI DesignDocumento32 pagineECE 424 – Introduction to VLSI DesignDineshNessuna valutazione finora

- GEC9 2nd EditionDocumento8 pagineGEC9 2nd Editionrex ceeNessuna valutazione finora

- Crossed-Field Amplifier (CFA)Documento3 pagineCrossed-Field Amplifier (CFA)Raúl VargasNessuna valutazione finora

- Dokumen - Tips - System On Chip Soc 5584a750d1651Documento21 pagineDokumen - Tips - System On Chip Soc 5584a750d1651pankaj chandankhedeNessuna valutazione finora

- Maintenance/ Discontinued: BTL 47W Audio Power Amplifier CircuitDocumento4 pagineMaintenance/ Discontinued: BTL 47W Audio Power Amplifier Circuitpradipto87Nessuna valutazione finora

- Cep, Ecd2020Documento2 pagineCep, Ecd2020Osama Asghar100% (1)

- Rt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1Documento9 pagineRt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1laptophaianhNessuna valutazione finora

- Adc Programing of Atmega32Documento9 pagineAdc Programing of Atmega32Diogo OliveiraNessuna valutazione finora

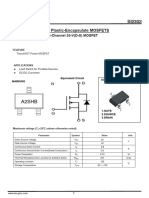

- A2shb-Sot 23Documento4 pagineA2shb-Sot 23bhffws8crfNessuna valutazione finora

- Self-Powered Fast Battery Tester SchematicDocumento3 pagineSelf-Powered Fast Battery Tester SchematicBanyu GeaNessuna valutazione finora

- Isolated 2SW 1leg 2A Smart Gate Drive ModuleDocumento11 pagineIsolated 2SW 1leg 2A Smart Gate Drive ModuleMuhammad SameerNessuna valutazione finora

- Datasheet 68HC05Documento106 pagineDatasheet 68HC05dcrazvanNessuna valutazione finora

- Integrated Circuits Kec501Documento2 pagineIntegrated Circuits Kec501childhoodtoons81Nessuna valutazione finora

- IntroCtrlSys - Final Exam - 1st Semester - 1920 - Solution PDFDocumento5 pagineIntroCtrlSys - Final Exam - 1st Semester - 1920 - Solution PDFTran Nguyen KhangNessuna valutazione finora

- Ee 2255 Digital Logic CircuitsDocumento7 pagineEe 2255 Digital Logic CircuitsjohnsamvlbNessuna valutazione finora

- Analog Power Management Ic Design CopecDocumento535 pagineAnalog Power Management Ic Design Copec王彦威Nessuna valutazione finora

- ECN 542: Microwave Integrated Circuits Lecture Module #5: Mixer DesignDocumento33 pagineECN 542: Microwave Integrated Circuits Lecture Module #5: Mixer DesignAman SharmaNessuna valutazione finora

- A Comprehensive Delay Model For CMOS InvertersDocumento8 pagineA Comprehensive Delay Model For CMOS InvertersSANT SARANNessuna valutazione finora

- RC CircuitsDocumento34 pagineRC CircuitsNader ElenanyNessuna valutazione finora

- Floyd OscillatorDocumento13 pagineFloyd Oscillatorjeanne pauline cruzNessuna valutazione finora

- Amplifiers Using FETsDocumento6 pagineAmplifiers Using FETsabdullah samdi100% (4)

- B 20170901 IC Design PhilosophyDocumento10 pagineB 20170901 IC Design Philosophym100% (1)

- 4.multiplexer & DemultiplexerDocumento3 pagine4.multiplexer & DemultiplexerSudhan HariNessuna valutazione finora

- Electronics I Lab Manual - 5 CMOS NAND GateDocumento4 pagineElectronics I Lab Manual - 5 CMOS NAND GateHarshit DuaNessuna valutazione finora

- Lab Report 7 (Open Ended Lab)Documento8 pagineLab Report 7 (Open Ended Lab)Mohammad Fahim Nur0% (1)

- Orcad / Pspice Simulator - 7400 Library - 7408, 7432 & 7486 Simulation Settings: Analysis Type - Time DomainDocumento6 pagineOrcad / Pspice Simulator - 7400 Library - 7408, 7432 & 7486 Simulation Settings: Analysis Type - Time DomainsanthoshiNessuna valutazione finora

- Over or Under Voltage Protection of Electrical AppliancesDocumento3 pagineOver or Under Voltage Protection of Electrical Appliancesanoopk778Nessuna valutazione finora