Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Soc Verif Udemy Lec 5 Methodologies Sim Formal

Caricato da

renju91Descrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Soc Verif Udemy Lec 5 Methodologies Sim Formal

Caricato da

renju91Copyright:

Formati disponibili

Verification Methods

Simulation Based

Formal Verification

Semi Formal Verificaion

Assertions

Verification with System Verilog 8/2/2017 1

Simulation Based Verification

1 Simulator

0 0

1 1

1 1 ?

=

Test

Vector Implementation

Generator

1 1

0 0 checker

1

8/2/2017 Verification with System Verilog 2

Formal Verification

What is Formal Verification?

It is the method by which we prove or disprove a design

implementation against a formal specification or

property

Uses mathematical reasoning

It algorithmically and exhaustively explores all

possible input values over time.

works well for small designs where the number of

inputs, outputs and states is small

8/2/2017 Verification with System Verilog 3

Formal - Equivalence Checking

Equivalence checker checks the logical equivalence of

the final version of the netlist with the RTL

Equivalence checker checks for functional equivalence

and not functional correctness

8/2/2017 Verification with System Verilog 4

Formal - Equivalence Checking

Design

RTLC / GatesC

Implementation

Step 2

Reference/Golden

Design

Design Equivalence

RTLA / GatesA Checker

Implementation

Reference/Golden Step C

A == B ?

Design

Design

RTLB / GatesB

Target/Modified

Design

8/2/2017 Verification with System Verilog 5

Formal Model Checking

Exhaustive search of FSM for state/property

violations

Two inputs to the algorithm

A finite state transition system (FSM) representing

the implementation

A formal property representing the specification

The algorithm checks whether the FSM models the

property correctly

8/2/2017 Verification with System Verilog 6

Formal Model Checking

Formal

G(p F q)

Property

PASS

MC

p

algorithm

p

q FAIL q

counterexample

FSM model

8/2/2017 Verification with System Verilog 7

Advantages of Formal Verification

Covers exhaustive state space, something difficult to

achieve by simulations

Does not require generation of input stimulus, since

exhaustive stimulus can be generated automatically by tool

No need to generate expected output sequences

Correctness of design guaranteed mathematically

Verification with System Verilog 8/2/2017 8

Disadvantages

Scalability

each added flop doubles the state space. Limited to

designs with small state spaces like interfaces, small FSMs.

What properties to verify?

For some methods, needs the specification to be

translated into properties to verify that properties hold

under all inputs and all states.

Verification with System Verilog 8/2/2017 9

Semi-Formal Verification

Best of both worlds (Simulation & Formal)

Use simulation to reach interesting states in the design

Then fork off formal to do exhaustive analysis around the

interesting state

Finds bugs sitting deep in the design

Useful for bug hunting

8/2/2017 Verification with System Verilog 10

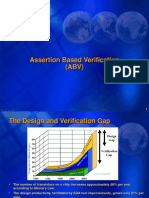

Assertion Based Verification

What is Assertion?

An Assertion is a statement about a designs intended

behavior ,which must be verified

Benefits of Assertions:

Improving Observability and debug ability

Improving integration through correct usage checking

Improving verification efficiency

Improving communication through documentation

Useful in both static and dynamic simulations

8/2/2017 Verification with System Verilog 11

Assertion Types

Immediate Assertion

assert (A == B) else $error("It's gone wrong");

Concurrent Assertion

property p1;

@(posedge clk) disable iff (Reset) not b ##1 c;

endproperty

assert property (p1) else $error(B ##1C failed);

Verification with System Verilog 8/2/2017 12

Assertion Based Verification

Using Assertions in Formal Verification

Formally specify all functional requirements and behavior

of design in a language

Use a procedure to prove that all specified properties hold

true

Using Assertions in Dynamic Simulation

Specified properties are useful as checks and for coverage

8/2/2017 Verification with System Verilog 13

Summary

Simulation based Verification is used to

find most bugs

Formal verification is useful in select areas

Assertions are a great value add

Verification with System Verilog 8/2/2017 14

Potrebbero piacerti anche

- Mastering Go Network Automation: Automating Networks, Container Orchestration, Kubernetes with Puppet, Vegeta and Apache JMeterDa EverandMastering Go Network Automation: Automating Networks, Container Orchestration, Kubernetes with Puppet, Vegeta and Apache JMeterNessuna valutazione finora

- SV Uvm RamdasDocumento182 pagineSV Uvm Ramdasankur100% (1)

- 1 Tag芯片的功能验证平台的设计 黄海蓉Documento73 pagine1 Tag芯片的功能验证平台的设计 黄海蓉donmar jrNessuna valutazione finora

- Manasa Hanakere Krishnappa - ResumeDocumento3 pagineManasa Hanakere Krishnappa - ResumesanjuNessuna valutazione finora

- Course Material SV CranesDocumento123 pagineCourse Material SV Cranesvr46shreyasNessuna valutazione finora

- Pro QMSDocumento23 paginePro QMSSudhir KumarNessuna valutazione finora

- VC Formal DsDocumento4 pagineVC Formal DsYu SuNessuna valutazione finora

- TC4 V-Cycle and Tools - Rev13Documento14 pagineTC4 V-Cycle and Tools - Rev13駱奎延Nessuna valutazione finora

- Synopsys Formality WorkshopDocumento293 pagineSynopsys Formality WorkshopBasem HeshamNessuna valutazione finora

- Testing Pega Applications: Accelerating Delivery Using Devops Practices For Pega ApplicationsDocumento35 pagineTesting Pega Applications: Accelerating Delivery Using Devops Practices For Pega ApplicationsSupriyo SantraNessuna valutazione finora

- 8-Test Automation Framework 20160729Documento21 pagine8-Test Automation Framework 20160729Jocelito WagnerNessuna valutazione finora

- Agile Test Methodology Vs VModelDocumento5 pagineAgile Test Methodology Vs VModelkamakshyiNessuna valutazione finora

- Verification of "Advanced Encryption Standard"Documento20 pagineVerification of "Advanced Encryption Standard"nnnNessuna valutazione finora

- DVCon Europe 2015 TA1 9 PresentationDocumento16 pagineDVCon Europe 2015 TA1 9 PresentationJon DCNessuna valutazione finora

- Improving Gate-Level Simulation Performance Author: Gagandeep SinghDocumento34 pagineImproving Gate-Level Simulation Performance Author: Gagandeep SinghParthasarathy NarasimhanNessuna valutazione finora

- Software Testing 6Documento13 pagineSoftware Testing 6vinitajennyNessuna valutazione finora

- Pre Silicon Validation WhitepaperDocumento3 paginePre Silicon Validation WhitepaperSrivatsava GuduriNessuna valutazione finora

- Presentation 14Documento12 paginePresentation 14Geofrey KweyuNessuna valutazione finora

- Introduction To Design VerificationDocumento60 pagineIntroduction To Design VerificationKesavaram ChallapalliNessuna valutazione finora

- Software Test Automation With Open Source SoftwareDocumento105 pagineSoftware Test Automation With Open Source SoftwareJuan FabianNessuna valutazione finora

- Cad FlowsDocumento26 pagineCad FlowsjaanuchockyNessuna valutazione finora

- Basics For System VerilogDocumento68 pagineBasics For System VerilogSamuel WhiteNessuna valutazione finora

- Objective: Krishna Chaitanya SDocumento8 pagineObjective: Krishna Chaitanya SSharukh SayedNessuna valutazione finora

- 04 VerifyDocumento68 pagine04 Verifyveena_scNessuna valutazione finora

- L4 Lifecycle Documen 15A2D0Documento64 pagineL4 Lifecycle Documen 15A2D0Lucin HuseinNessuna valutazione finora

- Accelerating SoC Verification Closure With Unified Verification Managemnet Solution - Execman-WpDocumento5 pagineAccelerating SoC Verification Closure With Unified Verification Managemnet Solution - Execman-WpSam HoneyNessuna valutazione finora

- DFT-Formal VerificationDocumento29 pagineDFT-Formal Verificationyhossam95Nessuna valutazione finora

- Key Lessons Learned in Financials During Global Upgrade From E-Business Suite 11i To R1223 - OOW16Documento26 pagineKey Lessons Learned in Financials During Global Upgrade From E-Business Suite 11i To R1223 - OOW16Narayan SubramanianNessuna valutazione finora

- Functional Checking of Design Using Formal Verification TechniquesDocumento31 pagineFunctional Checking of Design Using Formal Verification TechniquesJyoti ThakurNessuna valutazione finora

- Sample FS - IntegrationDocumento13 pagineSample FS - IntegrationKerryna HeshNessuna valutazione finora

- Supriya Khare: Experience Area of InterestDocumento4 pagineSupriya Khare: Experience Area of InterestAmit GoyalNessuna valutazione finora

- Verification OverviewDocumento123 pagineVerification OverviewSamNessuna valutazione finora

- Paper Automation Regression TestingDocumento19 paginePaper Automation Regression TestingVasu VenkatarayappaNessuna valutazione finora

- Impact Analysis of Software RequirementDocumento8 pagineImpact Analysis of Software RequirementsudheerNessuna valutazione finora

- Automation PresentationDocumento32 pagineAutomation Presentationapi-3698888Nessuna valutazione finora

- Experion PKS - Virtual Process OverviewDocumento21 pagineExperion PKS - Virtual Process OverviewProtheuss01100% (1)

- QC-Gage 40Documento2 pagineQC-Gage 40dadiNessuna valutazione finora

- Automotive Consulting Solution: EAM ChecklistsDocumento26 pagineAutomotive Consulting Solution: EAM ChecklistsKarthick Narayanan100% (2)

- Verification CVSDocumento97 pagineVerification CVSEman zakriaNessuna valutazione finora

- V-Model Description: Quick Test ProfessionalDocumento6 pagineV-Model Description: Quick Test ProfessionalSibaram SatpathyNessuna valutazione finora

- 10 Steps Crypto GuideDocumento15 pagine10 Steps Crypto GuidetdigitsNessuna valutazione finora

- Gear CamDocumento36 pagineGear CamBeny StephenNessuna valutazione finora

- Kovair ALM Studio Brochure JUNE 2018Documento4 pagineKovair ALM Studio Brochure JUNE 2018bhanumathi ksNessuna valutazione finora

- Software Development ModelsDocumento63 pagineSoftware Development ModelsAniruddha BhaleraoNessuna valutazione finora

- 01 04 PCIe 3 0 Compliance Testing FROZENDocumento52 pagine01 04 PCIe 3 0 Compliance Testing FROZENMinlongerNessuna valutazione finora

- 2014 - Curs VerifDocumento7 pagine2014 - Curs VerifMihaita SmintinaNessuna valutazione finora

- Work Flow DCMTestingDocumento6 pagineWork Flow DCMTestingapi-3738458Nessuna valutazione finora

- QTP GuideDocumento133 pagineQTP Guiderajeshtewari10Nessuna valutazione finora

- QAQC Vs Risk Management 1709443817Documento20 pagineQAQC Vs Risk Management 1709443817Umair AnsariNessuna valutazione finora

- QAQC Risk Management PDFDocumento20 pagineQAQC Risk Management PDFEng-TaYsEeRNessuna valutazione finora

- Ch4-Processes and Specifications-STMTDocumento77 pagineCh4-Processes and Specifications-STMTparvezNessuna valutazione finora

- ADV - SQA CH03A Software Verifications MSDocumento28 pagineADV - SQA CH03A Software Verifications MSxain khanNessuna valutazione finora

- How To Develop High Quality SoftwareDocumento8 pagineHow To Develop High Quality SoftwareGladiator_PraveenNessuna valutazione finora

- Verification Vs Validation in VLSIDocumento2 pagineVerification Vs Validation in VLSILearnyzenNessuna valutazione finora

- 59 5Documento11 pagine59 5SamNessuna valutazione finora

- Radha Priyanka ResumeDocumento4 pagineRadha Priyanka ResumepneelgundNessuna valutazione finora

- ABV Ali HmedatDocumento32 pagineABV Ali HmedatAli HmedatNessuna valutazione finora

- DMT Automation UI-Testing Practice7Documento25 pagineDMT Automation UI-Testing Practice7dkulinichNessuna valutazione finora

- FIFODocumento13 pagineFIFOrenju91Nessuna valutazione finora

- VerificationProjectAssignmentsMar15 PDFDocumento19 pagineVerificationProjectAssignmentsMar15 PDFrenju91100% (1)

- Syllabus S16 PDFDocumento5 pagineSyllabus S16 PDFrenju91Nessuna valutazione finora

- ECE453 SP17 NotesDocumento452 pagineECE453 SP17 Notesrenju91100% (1)

- DspqnsDocumento1 paginaDspqnsrenju91Nessuna valutazione finora

- Exam Application Tracking ReportDocumento1 paginaExam Application Tracking Reportrenju91Nessuna valutazione finora

- Theodore Sider - Logic For Philosophy PDFDocumento377 pagineTheodore Sider - Logic For Philosophy PDFAnonymous pYK2AqH100% (1)

- Case Analysis SampleDocumento22 pagineCase Analysis SampleMicaela EncinasNessuna valutazione finora

- Minerals Down The Microscope PDFDocumento8 pagineMinerals Down The Microscope PDFArijit LaikNessuna valutazione finora

- Viking Bladder Tanks - enDocumento11 pagineViking Bladder Tanks - enVINOD PAULNessuna valutazione finora

- TERZ 94OMManualRev0107 PDFDocumento66 pagineTERZ 94OMManualRev0107 PDFRoberto Andres Vasquez Campusano75% (4)

- Miscellaneous Measurements: and ControlsDocumento50 pagineMiscellaneous Measurements: and ControlsJeje JungNessuna valutazione finora

- 3 Types of Emergency Shutdown and Emergency Isolation ValvesDocumento4 pagine3 Types of Emergency Shutdown and Emergency Isolation ValvesMateusz KonopnickiNessuna valutazione finora

- SANS5847 - Flakiness Index of Course AggregatesDocumento7 pagineSANS5847 - Flakiness Index of Course AggregatesAndrew MwindililaNessuna valutazione finora

- Suárez y Melián 2021 Fluted Triangular Non Stemmed PointsDocumento22 pagineSuárez y Melián 2021 Fluted Triangular Non Stemmed PointsJuliaNessuna valutazione finora

- Midterm Exam Schedule-Summer 2022 Weekdays and WeekendDocumento14 pagineMidterm Exam Schedule-Summer 2022 Weekdays and Weekendmansoor malikNessuna valutazione finora

- Iso With Eccentric LoadingDocumento12 pagineIso With Eccentric Loadingsaubhagya majhiNessuna valutazione finora

- Riluzole For SCZDocumento11 pagineRiluzole For SCZHana Rizka AnandaNessuna valutazione finora

- Ziad Masri - Reality Unveiled The Hidden KeyDocumento172 pagineZiad Masri - Reality Unveiled The Hidden KeyAivlys93% (15)

- Grammar: Parts of Speech: 1.nounDocumento100 pagineGrammar: Parts of Speech: 1.nounrafatoNessuna valutazione finora

- Modem StandardsDocumento28 pagineModem StandardsShammer ShaNessuna valutazione finora

- Jurnal Teknologi Technoscientia Issn: 1979-8415 Vol. 5 No. 2 Februari 2013Documento7 pagineJurnal Teknologi Technoscientia Issn: 1979-8415 Vol. 5 No. 2 Februari 2013DENNIHERNessuna valutazione finora

- Update DES Day Pit 9 Per Jam 08Documento1 paginaUpdate DES Day Pit 9 Per Jam 08Iccang DewiNessuna valutazione finora

- EEE2205 Introduction To MeasurementsDocumento4 pagineEEE2205 Introduction To MeasurementsKibelennyNessuna valutazione finora

- Pay It ForwardDocumento4 paginePay It ForwardAndrew FarrellNessuna valutazione finora

- Brugg Cables Presentation ECMC PDFDocumento47 pagineBrugg Cables Presentation ECMC PDFlilcristiNessuna valutazione finora

- FM Testbank Ch08Documento6 pagineFM Testbank Ch08David LarryNessuna valutazione finora

- Partially Object-Oriented Programming LanguageDocumento3 paginePartially Object-Oriented Programming LanguageMusthafaNessuna valutazione finora

- 2020 Specimen Paper 1Documento16 pagine2020 Specimen Paper 1YuanWei SiowNessuna valutazione finora

- Sample Electrical TakeoffDocumento6 pagineSample Electrical TakeoffHafsa IjazNessuna valutazione finora

- BPCL Training ReportDocumento34 pagineBPCL Training ReportVishalVaishNessuna valutazione finora

- Ansys ManualDocumento124 pagineAnsys ManualUdamanNessuna valutazione finora

- FFT Analysis of Poorly Organized NanoporesDocumento5 pagineFFT Analysis of Poorly Organized NanoporesJuly Gonzalez BonagasNessuna valutazione finora

- Transformers 2023Documento36 pagineTransformers 2023dgongorNessuna valutazione finora

- Cisco Nexus 9300 ACI Fixed Spine Switches: Product OverviewDocumento7 pagineCisco Nexus 9300 ACI Fixed Spine Switches: Product OverviewMahmoud RamadanNessuna valutazione finora