Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

VLSI Test Process and Equipment

Caricato da

jagruthims0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

39 visualizzazioni43 pagineTitolo originale

lec2.ppt

Copyright

© © All Rights Reserved

Formati disponibili

PPT, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PPT, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

39 visualizzazioni43 pagineVLSI Test Process and Equipment

Caricato da

jagruthimsCopyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PPT, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 43

Lecture 2

VLSI Test Process and

Equipment

Motivation

Types of Testing

Test Specifications and Plan

Test Programming

Test Data Analysis

Automatic Test Equipment

Parametric Testing

Summary

Copyright 20 VLSI Test: Lecture 2 1

Motivation

Need to understand Automatic Test Equipment (ATE)

technology

Influences what tests are possible

Serious analog measurement limitations at high

digital frequency or in the analog domain

Understand capabilities for digital logic, memory,

and analog test for testing System-on-a-Chip

(SOC)

Need to understand parametric testing

For setup and hold time measurements

For determination of VIL , VIH , VOL , VOH , tr , tf , td , IOL,

IOH , IIL, IIH

Copyright 20 VLSI Test: Lecture 2 2

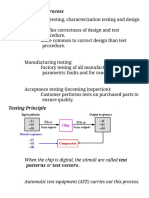

Types of Testing

Verification testing, characterization testing, or

design debug

Verifies correctness of design and correctness

of test procedure may require correction of

either or both

Manufacturing testing

Factory testing of all manufactured chips for

parametric and logic faults, and analog

specifications

Burn-in or stress testing

Acceptance testing (incoming inspection)

User (customer) tests purchased parts to

ensure quality

Copyright 20 VLSI Test: Lecture 2 3

Testing Principle

Copyright 20 VLSI Test: Lecture 2 4

Automatic Test

Equipment (ATE)

Consists of:

Powerful computer

Powerful 32-bit Digital Signal Processor (DSP)

for analog testing

Test Program (written in high-level language)

running on the computer

Probe Head (actually touches the bare or

packaged chip to perform fault detection

experiments)

Probe Card or Membrane Probe (contains

electronics to measure signals on chip pin or

pad)

Copyright 20 VLSI Test: Lecture 2 5

Characterization or

Verification Test

Ferociously expensive

Applied to selected (not all) parts

Used prior to production or manufacturing test

May comprise:

Scanning Electron Microscope tests

Bright-Lite detection of defects

Electron beam testing

Artificial intelligence (expert system) methods

Repeated functional tests

Copyright 20 VLSI Test: Lecture 2 6

Characterization

(Cont.)

Worst-case test

Choose test that passes/fails chips

Select statistically significant sample of chips

Repeat test for every combination of

environmental variables

Plot results in Shmoo plot

Diagnose and correct design errors

Continue throughout production life of chips to

improve design and process to increase yield

Copyright 20 VLSI Test: Lecture 2 7

Shmoo Plot

CS

tOTD

DATA

SRAM read operation

tOTD = time to DATA

tristated after

chip deselect

Copyright 20 VLSI Test: Lecture 2 8

Manufacturing Test

Determines whether manufactured chip meets

specification

Must cover high % of modeled faults

Must minimize test time (to control cost)

No fault diagnosis

Test every device on chip

Test at rated speed or at maximum speed

guaranteed by supplier

Copyright 20 VLSI Test: Lecture 2 9

Burn-in or Stress Test

Process:

Subject chips to high temperature and over-

voltage supply, while running production tests

Catches:

Infant mortality cases these are damaged or

weak (low reliability) chips that will fail in the first

few days of operation burn-in causes bad

devices to fail before they are shipped to

customers

Freak failures devices having same failure

mechanisms as reliable devices

Copyright 20 VLSI Test: Lecture 2 10

Incoming Inspection

Can be:

Similar to production testing

More comprehensive than production testing

Tuned to specific system application

Often done for a random sample of devices

Sample size depends on device quality and

system reliability requirements

Avoids putting defective device in a system

where cost of diagnosis and repair exceeds

incoming inspection cost

Copyright 20 VLSI Test: Lecture 2 11

Manufacturing Test

Scenarios

Wafer sort or probe test done before wafer is

scribed and cut into chips

Includes test site characterization specific

test devices are checked with specific patterns

to measure:

Gate threshold

Polysilicon field threshold

Poly sheet resistance, etc.

Packaged device tests

Copyright 20 VLSI Test: Lecture 2 12

Types of Tests

Parametric measures electrical properties of pin

electronics delay, voltages, currents, etc. fast

and cheap

Functional used to cover very high % of

modeled faults test every transistor and wire in

digital circuits long and expensive main topic

of tutorial

Copyright 20 VLSI Test: Lecture 2 13

Two Different

Meanings of

Functional Test

ATE and Manufacturing World any vectors

applied to cover high % of faults during

manufacturing test

Automatic Test-Pattern Generation World

testing with verification vectors, which determine

whether hardware matches its specification

typically have low fault coverage (< 70 %)

Copyright 20 VLSI Test: Lecture 2 14

Test Specifications &

Plan

Test Specifications:

Functional Characteristics

Type of Device Under Test (DUT)

Physical Constraints package, pin numbers, etc.

Environmental Characteristics power supply,

temperature, humidity, etc.

Reliability acceptance quality level

(defects/million), failure rate, etc.

Test plan generated from specifications

Type of test equipment to use

Types of tests

Fault coverage requirement

Copyright 20 VLSI Test: Lecture 2 15

Test Programming

Copyright 20 VLSI Test: Lecture 2 16

Test Data Analysis

Uses of ATE test data:

Reject bad DUTs

Fabrication process information

Design weakness information

Devices that did not fail are good only if tests

covered 100% of faults

Failure mode analysis (FMA):

Diagnose reasons for device failure, and find

design and process weaknesses

Improve logic and layout design rules

Copyright 20 VLSI Test: Lecture 2 17

Automatic

Automatic Test

Test

Equipment

Equipment (ATE)

(ATE)

Copyright 2001, Agr VLSI Test: Lecture 2 18

awal & Bushnell

ADVANTEST Model

T6682 ATE

Copyright 20 VLSI Test: Lecture 2 19

T6682 ATE Block

Diagram

Copyright 20 VLSI Test: Lecture 2 20

T6682 ATE

Specifications

Uses 0.35 VLSI chips in implementation

1,024 digital pin channels

Speed: 250, 500, or 1000 MHz

Timing accuracy: +/- 200 ps

Drive voltage: - 2.5 to 6 V

Clock/strobe accuracy: +/- 870 ps

Clock settling resolution: 31.25 ps

Pattern multiplexing: write 2 patterns in one ATE

cycle

Pin multiplexing: use 2 pins to control 1 DUT pin

Copyright 20 VLSI Test: Lecture 2 21

Pattern Generation

Sequential pattern generator (SQPG): stores 16

Mvectors of patterns to apply to DUT -- vector width

determined by # DUT pins

Algorithmic pattern generator (ALPG): 32

independent address bits, 36 data bits

For memory test has address descrambler

Has address failure memory

Scan pattern generator (SCPG) supports JTAG

boundary scan, greatly reduces test vector memory

for full-scan testing

2 Gvector or 8 Gvector sizes

Copyright 20 VLSI Test: Lecture 2 22

Response Checking

and Frame Processor

Response Checking:

Pulse train matching ATE matches patterns

on 1 pin for up to 16 cycles

Pattern matching mode matches pattern on a

number of pins in 1 cycle

Determines whether DUT output is correct,

changes patterns in real time

Frame Processor combines DUT input stimulus

from pattern generators with DUT output

waveform comparison

Strobe time interval after pattern application

when outputs sampled

Copyright 20 VLSI Test: Lecture 2 23

Probing

Pin electronics (PE) electrical buffering circuits,

put as close as possible to DUT

Uses pogo pin connector at test head

Test head interface through custom printed circuit

board to wafer prober (unpackaged chip test) or

package handler (packaged chip test), touches chips

through a socket (contactor)

Uses liquid cooling

Can independently set VIH , VIL , VOH , VOL, IH , IL, VT

for each pin

Parametric Measurement Unit (PMU)

Copyright 20 VLSI Test: Lecture 2 24

Pin Electronics

Copyright 20 VLSI Test: Lecture 2 25

Probe Card and Probe

Needles or Membrane

Probe card custom printed circuit board (PCB)

on which DUT is mounted in socket may

contain custom measurement hardware (current

test)

Probe needles come down and scratch the pads

to stimulate/read pins

Membrane probe for unpackaged wafers

contacts printed on flexible membrane, pulled

down onto wafer with compressed air to get

wiping action

Copyright 20 VLSI Test: Lecture 2 26

T6682 ATE Software

Runs Solaris UNIX on UltraSPARC 167 MHz CPU

for non-real time functions

Runs real-time OS on UltraSPARC 200 MHz CPU

for tester control

Peripherals: disk, CD-ROM, micro-floppy, monitor,

keyboard, HP GPIB, Ethernet

Viewpoint software provided to debug, evaluate,

and analyze VLSI chips

Copyright 20 VLSI Test: Lecture 2 27

LTX FUSION HF ATE

Copyright 20 VLSI Test: Lecture 2 28

Specifications

Intended for SOC test digital, analog, and

memory test supports scan-based test

Modular can be upgraded with additional

instruments as test requirements change

enVision Operating System

1 or 2 test heads per tester, maximum of 1024

digital pins, 1 GHz maximum test rate

Maximum 64 Mvectors memory storage

Analog instruments: DSP-based synthesizers,

digitizers, time measurement, power test, Radio

Frequency (RF) source and measurement

capability (4.3 GHz)

Copyright 20 VLSI Test: Lecture 2 29

Multi-site Testing

Major Cost Reduction

One ATE tests several (usually identical) devices

at the same time

For both probe and package test

DUT interface board has > 1 sockets

Add more instruments to ATE to handle multiple

devices simultaneously

Usually test 2 or 4 DUTS at a time, usually test 32

or 64 memory chips at a time

Limits: # instruments available in ATE, type of

handling equipment available for package

Copyright 20 VLSI Test: Lecture 2 30

Electrical

Electrical Parametric

Parametric

Testing

Testing

Copyright 2001, Agr VLSI Test: Lecture 2 31

awal & Bushnell

Typical Test Program

1. Probe test (wafer sort) catches gross defects

2. Contact electrical test

3. Functional & layout-related test

4. DC parametric test

5. AC parametric test

Unacceptable voltage/current/delay at pin

Unacceptable device operation limits

Copyright 20 VLSI Test: Lecture 2 32

DC

DC Parametric

Parametric Tests

Tests

Copyright 2001, Agr VLSI Test: Lecture 2 33

awal & Bushnell

Contact Test

1. Set all inputs to 0 V

2. Force current Ifb out of pin (expect Ifb to be 100

to 250 mA)

3. Measure pin voltage Vpin. Calculate pin

resistance R

Contact short (R = 0 W)

No problem

Pin open circuited (R huge), Ifb and Vpin large

Copyright 20 VLSI Test: Lecture 2 34

Power Consumption

Test

1. Set temperature to worst case, open circuit

DUT outputs

2. Measure maximum device current drawn from

supply ICC at specified voltage

ICC > 70 mA (fails)

40 mA < ICC 70 mA (ok)

Copyright 20 VLSI Test: Lecture 2 35

Output Short Current

Test

1. Make chip output a 1

2. Short output pin to 0 V in PMU

3. Measure short current (but not for long, or the

pin driver burns out)

Short current > 40 A (ok)

Short current 40 A (fails)

Copyright 20 VLSI Test: Lecture 2 36

Output Drive Current

Test

1. Apply vector forcing pin to 0

2. Simultaneously force VOL voltage and

measure IOL

3. Repeat Step 2 for logic 1

IOL < 2.1 mA (fails)

IOH < -1 mA (fails)

Copyright 20 VLSI Test: Lecture 2 37

Threshold Test

1. For each I/P pin, write logic 0 followed by

propagation pattern to output. Read output.

Increase input voltage in 0.1 V steps until output

value is wrong

2. Repeat process, but stepping down from logic 1

by 0.1 V until output value fails

Wrong output when 0 input > 0.8 V (ok)

Wrong output when 0 input 0.8 V (fails)

Wrong output when 1 input < 2.0 V (ok)

Wrong output when 1 input 2.0 V (fails)

Copyright 20 VLSI Test: Lecture 2 38

AC

AC Parametric

Parametric Tests

Tests

Copyright 2001, Agr VLSI Test: Lecture 2 39

awal & Bushnell

Rise/fall Time Tests

Copyright 20 VLSI Test: Lecture 2 40

Set-up and Hold Time

Tests

Copyright 20 VLSI Test: Lecture 2 41

Propagation Delay

Tests

1. Apply standard output pin load (RC or RL)

2. Apply input pulse with specific rise/fall

3. Measure propagation delay from input to output

Delay between 5 ns and 40 ns (ok)

Delay outside range (fails)

Copyright 20 VLSI Test: Lecture 2 42

Summary

Parametric tests determine whether pin electronics

system meets digital logic voltage, current, and delay

time specs

Functional tests determine whether internal

logic/analog sub-systems behave correctly

ATE Cost Problems

Pin inductance (expensive probing)

Multi-GHz frequencies

High pin count (1024)

ATE Cost Reduction

Multi-Site Testing

DFT methods like Built-In Self-Test

Copyright 20 VLSI Test: Lecture 2 43

Potrebbero piacerti anche

- Sam Wall Chart Epa 07 and Epa 2010Documento2 pagineSam Wall Chart Epa 07 and Epa 2010Jose Luis Calla Huanca94% (17)

- AHU ChecklistDocumento11 pagineAHU Checklistaneesh50% (2)

- DFT For Advanced UserDocumento151 pagineDFT For Advanced UserAnonymous UeI6DVNessuna valutazione finora

- Spoken Hindi BookDocumento36 pagineSpoken Hindi Booksuresh70% (30)

- Ej800clfph - W800 Cafe 2019-20 PDFDocumento89 pagineEj800clfph - W800 Cafe 2019-20 PDFAlbert DepanoNessuna valutazione finora

- HPDocumento4 pagineHPHKVMVPVPV021511Nessuna valutazione finora

- Automated Hardware Testing Using PythonDocumento31 pagineAutomated Hardware Testing Using PythonYuvaraja67% (3)

- Digital Circuit Testing: A Guide to DFT and Other TechniquesDa EverandDigital Circuit Testing: A Guide to DFT and Other TechniquesNessuna valutazione finora

- Ford Mustang 1988-2006Documento16 pagineFord Mustang 1988-2006meng798651100% (1)

- Cameron Conventional WellheadDocumento25 pagineCameron Conventional WellheadQaiser Hafeez100% (4)

- Line Following Robot ReviewDocumento9 pagineLine Following Robot ReviewSree Krishna Nimmagadda ChowdaryNessuna valutazione finora

- VLSI Test Process and EquipmentDocumento43 pagineVLSI Test Process and EquipmentLakshmi PrasadNessuna valutazione finora

- VLSI Test Process and Equipment LectureDocumento49 pagineVLSI Test Process and Equipment LecturereneeshczNessuna valutazione finora

- Test Process and AteDocumento43 pagineTest Process and Ateapi-78343547Nessuna valutazione finora

- The VLSI Testing ProcessDocumento12 pagineThe VLSI Testing ProcessVishnu 3333Nessuna valutazione finora

- ECE 617 - Fault Testable Design Dr. Janusz Starzyk: School of EECS Ohio University Athens, OH, 45701Documento79 pagineECE 617 - Fault Testable Design Dr. Janusz Starzyk: School of EECS Ohio University Athens, OH, 45701sivapothiNessuna valutazione finora

- VLSI Test Process and EquipmentDocumento43 pagineVLSI Test Process and Equipmentanup_sky88Nessuna valutazione finora

- Electronic Syatem Design PPT - Design For TestabilityDocumento9 pagineElectronic Syatem Design PPT - Design For TestabilityAnoop Mathew0% (1)

- Keysight i3070 ICT System Getting Started GuideDocumento8 pagineKeysight i3070 ICT System Getting Started GuideSergio BustillosNessuna valutazione finora

- VLSI Testing Techniques for Maximizing YieldDocumento23 pagineVLSI Testing Techniques for Maximizing YieldJagan RajendiranNessuna valutazione finora

- An experimental chip to evaluate multiple testing techniquesDocumento10 pagineAn experimental chip to evaluate multiple testing techniquesVinod KheraNessuna valutazione finora

- ALL ABOUT DIGITAL PRODUCTSDocumento43 pagineALL ABOUT DIGITAL PRODUCTSecehemnathNessuna valutazione finora

- VLSI Testing and Testability FundamentalsDocumento28 pagineVLSI Testing and Testability Fundamentalsmaxxtorr723Nessuna valutazione finora

- Vlsi TestingDocumento23 pagineVlsi TestingDilip MathuriaNessuna valutazione finora

- Design For Testability and Automatic Test Pattern GenerationDocumento33 pagineDesign For Testability and Automatic Test Pattern GenerationDilip Mathuria0% (1)

- Introduction to System-on-Chip Functional Verification ChallengesDocumento63 pagineIntroduction to System-on-Chip Functional Verification ChallengesRupam Ranjan BiswalNessuna valutazione finora

- Cmos TestingDocumento82 pagineCmos TestingbinduscribdNessuna valutazione finora

- Lecture 2Documento27 pagineLecture 2Anurag DubeyNessuna valutazione finora

- A Briefing On IEEE 1149.1 - 1990 Standard Test Access Port and Boundary-Scan Architecture (AKA JTAG)Documento12 pagineA Briefing On IEEE 1149.1 - 1990 Standard Test Access Port and Boundary-Scan Architecture (AKA JTAG)Raghul SambathkumarNessuna valutazione finora

- Chap1 Lect01 OverviewDocumento12 pagineChap1 Lect01 OverviewGlen ChenNessuna valutazione finora

- Vlsi Test Process & EcconomicsDocumento16 pagineVlsi Test Process & EcconomicsreneeshczNessuna valutazione finora

- PCB Diagnostic & Functional Test SystemDocumento6 paginePCB Diagnostic & Functional Test SystemEslam SalahNessuna valutazione finora

- DFT Basics and TypesDocumento17 pagineDFT Basics and TypessenthilkumarNessuna valutazione finora

- Vasu DFTDocumento28 pagineVasu DFTsenthilkumarNessuna valutazione finora

- Types of Testing: VLSI Testing Can Be Classified Into Four Types Depending Upon The Specific Purpose It AccomplishesDocumento15 pagineTypes of Testing: VLSI Testing Can Be Classified Into Four Types Depending Upon The Specific Purpose It AccomplishesRaph GalagNessuna valutazione finora

- WLR BrochureDocumento12 pagineWLR Brochuresrinath rajaramNessuna valutazione finora

- ds030 Fadec 011323Documento2 pagineds030 Fadec 011323hamid mirNessuna valutazione finora

- Testing Unit V VLSIDocumento23 pagineTesting Unit V VLSIkalavathi deviNessuna valutazione finora

- Getting Started - STM MCU - ExamplesDocumento69 pagineGetting Started - STM MCU - ExamplesXiaofang JiangNessuna valutazione finora

- 1.1 Testability and Design For Test (DFT)Documento29 pagine1.1 Testability and Design For Test (DFT)spaulsNessuna valutazione finora

- Automated Hardware Testing Using PythonDocumento31 pagineAutomated Hardware Testing Using PythonYuvaraja100% (1)

- DFT Basics: Detection Strategies and TypesDocumento5 pagineDFT Basics: Detection Strategies and TypessenthilkumarNessuna valutazione finora

- Electronic Test Equipment Is Used To Create Signals and CaptureDocumento7 pagineElectronic Test Equipment Is Used To Create Signals and Captureuntung cahyadiNessuna valutazione finora

- Electronic Test EquipmentDocumento7 pagineElectronic Test Equipmentjak jaganNessuna valutazione finora

- NPTEL DFTDocumento74 pagineNPTEL DFTPushkar AroraNessuna valutazione finora

- Chap1 Lect01 Overview.fmDocumento12 pagineChap1 Lect01 Overview.fmkartusnormanNessuna valutazione finora

- Boundary ScanDocumento26 pagineBoundary Scansreeramya021Nessuna valutazione finora

- Automatic Test Equipment: Keithley Instruments Series 4200 CVUDocumento8 pagineAutomatic Test Equipment: Keithley Instruments Series 4200 CVUMadhusudanan AshokNessuna valutazione finora

- TDfTAMS Part1Documento97 pagineTDfTAMS Part1AdiseshuMiddeNessuna valutazione finora

- DFT-the Easier Way To Test Analog ICsDocumento9 pagineDFT-the Easier Way To Test Analog ICsnishantsoni90Nessuna valutazione finora

- Verilog AMS TutorialDocumento29 pagineVerilog AMS TutorialSiva KrishnaNessuna valutazione finora

- PHY Validation of Thunderbolt & DisplayPortDocumento43 paginePHY Validation of Thunderbolt & DisplayPortvelusnNessuna valutazione finora

- Ee 587 Soc Design & TestDocumento30 pagineEe 587 Soc Design & TestjjnNessuna valutazione finora

- Abi Product Brochure SaeligDocumento24 pagineAbi Product Brochure Saeligitalo FerraraNessuna valutazione finora

- Development of JTAG Verification IP in UVM MethodologyDocumento3 pagineDevelopment of JTAG Verification IP in UVM MethodologyKesavaram ChallapalliNessuna valutazione finora

- Paddle Switch CombinedDocumento10 paginePaddle Switch CombinedPriyanshu GuptaNessuna valutazione finora

- IC TestDocumento46 pagineIC Testaltugpolat9456Nessuna valutazione finora

- Variable parameter IC testing improves CMOS defect detectionDocumento3 pagineVariable parameter IC testing improves CMOS defect detectionmdlogicsolutionsNessuna valutazione finora

- VlsiDocumento13 pagineVlsiRajaganapathi RajappanNessuna valutazione finora

- Technical Specification of Automatic Relay Test KitDocumento13 pagineTechnical Specification of Automatic Relay Test KitEBENessuna valutazione finora

- Design For TestDocumento4 pagineDesign For TestDivya PatelNessuna valutazione finora

- Experiment 1 - DDCADocumento9 pagineExperiment 1 - DDCArevelid899Nessuna valutazione finora

- Design For Testing (DFT) : M.Venugopal Reddy, Iiisem - Me (Cim)Documento26 pagineDesign For Testing (DFT) : M.Venugopal Reddy, Iiisem - Me (Cim)nithink100Nessuna valutazione finora

- FPGA Implementation of Self-Testing Logic Gates AdDocumento7 pagineFPGA Implementation of Self-Testing Logic Gates AdTakashi SuohNessuna valutazione finora

- Automatic Test EquipmentDocumento9 pagineAutomatic Test EquipmentSilpa SuseelanNessuna valutazione finora

- DT Key MaretrialDocumento12 pagineDT Key MaretrialSudheer RajaNessuna valutazione finora

- Data clustering and classification using K-means and LDADocumento1 paginaData clustering and classification using K-means and LDAjagruthimsNessuna valutazione finora

- Linux Kernel Explained: Components, Modes and FeaturesDocumento3 pagineLinux Kernel Explained: Components, Modes and FeaturesjagruthimsNessuna valutazione finora

- A Server Operating SystemDocumento1 paginaA Server Operating SystemjagruthimsNessuna valutazione finora

- Leon GuideDocumento31 pagineLeon GuidejagruthimsNessuna valutazione finora

- Sta 9 1Documento125 pagineSta 9 1Jayaprakash Polimetla100% (1)

- 04u 5Documento15 pagine04u 5jagruthimsNessuna valutazione finora

- IBReg FormDocumento1 paginaIBReg FormAbhishek KoliNessuna valutazione finora

- Organic Chemistry PDFDocumento13 pagineOrganic Chemistry PDFjagruthimsNessuna valutazione finora

- Lesson2 PDFDocumento6 pagineLesson2 PDFJessica Nov-nov DodsNessuna valutazione finora

- Standard Delay Format Overview and File FormatDocumento57 pagineStandard Delay Format Overview and File FormattatarasanurazvanNessuna valutazione finora

- Chatura Mar2014 PDFDocumento156 pagineChatura Mar2014 PDFSuryaprakash JosyulaNessuna valutazione finora

- DunhamTrimmer Biological Control Market Jefferies May 10 2015Documento13 pagineDunhamTrimmer Biological Control Market Jefferies May 10 2015jagruthimsNessuna valutazione finora

- 6-Delay-Fault Testing TutorialDocumento36 pagine6-Delay-Fault Testing TutorialjagruthimsNessuna valutazione finora

- 6 Delay Fault Testing TutorialDocumento35 pagine6 Delay Fault Testing TutorialjagruthimsNessuna valutazione finora

- 6 Delay Fault Testing TutorialDocumento35 pagine6 Delay Fault Testing TutorialjagruthimsNessuna valutazione finora

- 10 Chapter 5Documento22 pagine10 Chapter 5jagruthimsNessuna valutazione finora

- 6 Delay Fault Testing TutorialDocumento35 pagine6 Delay Fault Testing TutorialjagruthimsNessuna valutazione finora

- GGDocumento1 paginaGGjagruthimsNessuna valutazione finora

- Biological Pest Control Market DriversDocumento14 pagineBiological Pest Control Market DriversjagruthimsNessuna valutazione finora

- Standard Delay Format Overview and File FormatDocumento57 pagineStandard Delay Format Overview and File FormattatarasanurazvanNessuna valutazione finora

- EdtDocumento10 pagineEdtjagruthimsNessuna valutazione finora

- Bit OperationsDocumento11 pagineBit OperationsSony Neyyan VargheseNessuna valutazione finora

- Murata Trimmer PotentiometersDocumento55 pagineMurata Trimmer Potentiometerskn65238859Nessuna valutazione finora

- Jtag Boundary Scan Design For Testability Foresighted Board Level Design For Optimal Testability PDFDocumento32 pagineJtag Boundary Scan Design For Testability Foresighted Board Level Design For Optimal Testability PDFjagruthimsNessuna valutazione finora

- CummingsSNUG2008Boston CDCDocumento56 pagineCummingsSNUG2008Boston CDCKiran RaoNessuna valutazione finora

- 6-Delay-Fault Testing TutorialDocumento36 pagine6-Delay-Fault Testing TutorialjagruthimsNessuna valutazione finora

- Clock FlopDocumento16 pagineClock FlopVikram MehtaNessuna valutazione finora

- Rec5 v1Documento7 pagineRec5 v1jagruthimsNessuna valutazione finora

- Smartscan - Hierarchical Test Compression For Pin-Limited Low Power DesignsDocumento43 pagineSmartscan - Hierarchical Test Compression For Pin-Limited Low Power DesignsjagruthimsNessuna valutazione finora

- Busduct 8Documento56 pagineBusduct 8JeyakumarNessuna valutazione finora

- Micro 830 & 850 User ManualDocumento360 pagineMicro 830 & 850 User Manualryanmalsem50% (2)

- S&S Cycle (E&G) Carb Twincam88Engines 51 1013Documento4 pagineS&S Cycle (E&G) Carb Twincam88Engines 51 1013Jonathan BanksNessuna valutazione finora

- FlyBack Transformer CalculationsDocumento7 pagineFlyBack Transformer CalculationsdllabarreNessuna valutazione finora

- Manpower Allocation 17Documento609 pagineManpower Allocation 17Mark BagyendaNessuna valutazione finora

- WEEK 1 5 CybercrimeDocumento13 pagineWEEK 1 5 CybercrimeMariaNessuna valutazione finora

- Hydraulic System 6015B Hydraulic Mining Shovel: Machine - Right Side ViewDocumento4 pagineHydraulic System 6015B Hydraulic Mining Shovel: Machine - Right Side ViewJuan Carlos Inga Vasquez100% (1)

- GTU Bachelor of Engineering Industrial Electrical SystemsDocumento2 pagineGTU Bachelor of Engineering Industrial Electrical SystemsDarshit KotadiyaNessuna valutazione finora

- DasDocumento189 pagineDasFelix SamudioNessuna valutazione finora

- Passport P250 ManualDocumento15 paginePassport P250 ManualJoe BauerNessuna valutazione finora

- Intelligent Optical Smoke Detector: Product DatasheetDocumento2 pagineIntelligent Optical Smoke Detector: Product DatasheetVladimir BukaricaNessuna valutazione finora

- Grundfosliterature 5616244 PDFDocumento18 pagineGrundfosliterature 5616244 PDFMohammad ZeeshanNessuna valutazione finora

- Electrolux 2004 Room Air Conditioner Ms2 Compact2Documento23 pagineElectrolux 2004 Room Air Conditioner Ms2 Compact2rdc02271Nessuna valutazione finora

- Mccu 216 Manual T04Documento18 pagineMccu 216 Manual T04AlberthNessuna valutazione finora

- M7-2B Manual For TMCDocumento44 pagineM7-2B Manual For TMCAnonymous uTO1WI100% (2)

- PTC Starting Device, Disconnected by An Integrated Electromechanical Relay For Energy Saving Motor Compressor U.S. PATENT 6,356,047Documento3 paginePTC Starting Device, Disconnected by An Integrated Electromechanical Relay For Energy Saving Motor Compressor U.S. PATENT 6,356,047juan perezNessuna valutazione finora

- AE Lift Manual v1.3Documento56 pagineAE Lift Manual v1.3UmerNessuna valutazione finora

- 1.8-V Rated Load Switch with Level-ShiftDocumento6 pagine1.8-V Rated Load Switch with Level-ShiftTroy LarimerNessuna valutazione finora

- Vigneto Tractor Specs and ConfigurationsDocumento4 pagineVigneto Tractor Specs and ConfigurationsB de JongNessuna valutazione finora

- E6855 - Add Rev01Documento8 pagineE6855 - Add Rev01chris110Nessuna valutazione finora

- UK 1000 Quick Ref GuideDocumento44 pagineUK 1000 Quick Ref GuiderichardNessuna valutazione finora

- TCEW: Guide to Electrical Wiring Types and Termination MethodsDocumento17 pagineTCEW: Guide to Electrical Wiring Types and Termination MethodsnpfhNessuna valutazione finora

- Display TechnologyDocumento63 pagineDisplay Technologyanalog changeNessuna valutazione finora

- Electro Válvula Del CompresorDocumento4 pagineElectro Válvula Del CompresorneumaticoNessuna valutazione finora