Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Basics of Stick Diagrams and Layouts

Caricato da

SUSHANTH K J0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

38 visualizzazioni21 pagineIntroduction to Stick Diagrams and layouts. Rules to follow to write stick diagram using N and P transistors.

Titolo originale

Basics of Stick Diagrams and layouts

Copyright

© © All Rights Reserved

Formati disponibili

PPTX, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoIntroduction to Stick Diagrams and layouts. Rules to follow to write stick diagram using N and P transistors.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PPTX, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

38 visualizzazioni21 pagineBasics of Stick Diagrams and Layouts

Caricato da

SUSHANTH K JIntroduction to Stick Diagrams and layouts. Rules to follow to write stick diagram using N and P transistors.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PPTX, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 21

INTRODUCTION TO STICK

DIAGRAMS AND

LAYOUTS

Presented by

Sushanth kj

Asst.prof. detp. Of ece

Bearys institute of

technology

mangalore

STICK DIAGRAMS

Objectives:

To know what is meant by stick diagram.

To understand the capabilities and limitations of stick

diagram.

To learn how to draw stick diagrams for a given MOS

circuit.

Outcome:

At the end of this module the students will be able draw

the stick diagram for simple MOS circuits.

Definition

Stick diagramsconvey layer information

through colour codes (or monochrome

encoding). Acts as an interface between

symbolic circuit and the actual layout.

N+

When n-diffusion(green)

creates nMOS

crosses

N+

with

poly(red)

When p-diffusion crosses with poly creates

pMOS

Stick diagram of an CMOS Inverter

Circuit

diagram

Stick

VDD

VDD

X

X

X

X

Gnd

Gnd

Stick diagram

Blue = Metal1

Orange = p- diffusion

Green =n-diffusion

Red= polysilicon

Stick Diagrams Notations

Stick Diagrams Some rules to follow

Note: If a contact is shown then it is not a creation of

transistor.

2-input NAND gate

Two inputs nMOS NAND Gate

Three inputs nMOS NOR Gate

pMOS EX-OR logic gate

Transmission Gate(TG)

Introduction

Before the cell can be constructed from a transistor

schematic it is necessary to develop a strategy for

the cell's basic layout. Stick Diagrams are a means

for the design engineer to visualize the cell routing

and transistor placement.

Method:Stick diagrams are constructed in two

steps.

1)The first step is to construct a logic graph of the

schematic

(Figure1).

A)Identify each transistor by a unique name of its

gate signal (A, B, C, D, E in the example of

Figure1).

B)Identify each connection to the transistor by a

unique name (1,2,3,4 in the example of Figure 1).

Fig 1: Schematic and Graph

2)The second step is to construct one Euler path

for both the Pull up and Pull down network (Figure

2).

A)Euler paths are defined by a path the traverses

each node in the path, such that each edge is

visited only once.

B)The path is defined by the order of each

transistor name.

i)If the path traverses transistor A then B

then C. Then the path name is {A, B, C}

C)The Euler path of the Pull up network must be

the same as the path of the Pull down network.

D)Euler paths are not necessarily unique.

F)It may be necessary to redefine the function to

find a Euler path.

i)F = E + (CD) + (AB) = (AB) +E + (CD)

Fig 2: Euler Path

Connection label layout

A)Trace two green lines horizontally to represent the

NMOS and PMOS devices.

B)Trace the number of inputs (5 in this example)

vertically across each green strip. These represent the

gate contacts to the devices that are made of Poly.

C)Surround the NMOS device in a yellow box to

represent the surrounding Pwell material.

D)Surround the PMOS device in a green box to

represent the surrounding Nwell material.

E)Trace a blue line horizontally, above and below the

PMOS and NMOS lines to represent the Metal 1 of VDD

and VSS.

F)Label each Poly line with the Euler path label, in order

from left to right.

G)Place the connection labels upon the NMOS and

PMOS devices.

Connection label layout

Interconnection of the Device

A)Notice that Poly and Metal 1 can overlap.

B)Avoid routing signals that are side by side for

long lengths. This adds capacitance to the device.

C)Avoid all interconnect overlap if possible. This

adds capacitance to the device.

D)Strive for simplicity. This will later provide the

smallest and fastest devices.

E)You can use Poly, Metal 2, and even Active to

interconnect your device.

i)Poly and especially Active adds resistance to you

device.

ii)Avoid using Metal 2 if possible. Metal 2 is another

layer to your device that you will probably need in

the next heiarchy up.

Stick Diagram, Interconnected

Potrebbero piacerti anche

- MOS Integrated Circuit DesignDa EverandMOS Integrated Circuit DesignE. WolfendaleNessuna valutazione finora

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyDa EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNessuna valutazione finora

- Lect4 Stick DiagramDocumento23 pagineLect4 Stick Diagrammanicks369601Nessuna valutazione finora

- Stick Diagram Design in Complementary Static CMOSDocumento6 pagineStick Diagram Design in Complementary Static CMOSDivy Kumar GuptaNessuna valutazione finora

- Euler Path DiagramDocumento5 pagineEuler Path DiagramDebalina PandaNessuna valutazione finora

- Chapter 5Documento61 pagineChapter 5Faiz MohdNessuna valutazione finora

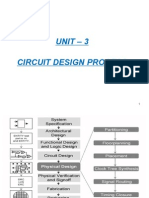

- Unit - 3 Circuit Design ProcessDocumento30 pagineUnit - 3 Circuit Design ProcessNagarjun RajputNessuna valutazione finora

- Stick DiagramDocumento16 pagineStick DiagramamitgayaNessuna valutazione finora

- Cad Asic Extra QuestionDocumento18 pagineCad Asic Extra QuestionDin_skyDNessuna valutazione finora

- (NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationDocumento13 pagine(NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationLakshmi JagupillaNessuna valutazione finora

- CHP 2 - Mos Design and LayoutDocumento104 pagineCHP 2 - Mos Design and Layoutkkece41Nessuna valutazione finora

- Stick Diagrams 1Documento19 pagineStick Diagrams 1ElakkiyaSelvarajNessuna valutazione finora

- 4-SNBhat - StickdiagraFile Setms - IUCEEEDocumento38 pagine4-SNBhat - StickdiagraFile Setms - IUCEEEranjithece1Nessuna valutazione finora

- MOS and BiCMOS Circuit Design ProcessDocumento17 pagineMOS and BiCMOS Circuit Design ProcessNarasimha Murthy YayavaramNessuna valutazione finora

- Stick Diagrams and LayoutsDocumento17 pagineStick Diagrams and LayoutsPraneetha InumarthiNessuna valutazione finora

- Unit Iii Vlsi Circuit Design Processes: MOS Circuits Are Formed On Four Basic LayersDocumento21 pagineUnit Iii Vlsi Circuit Design Processes: MOS Circuits Are Formed On Four Basic Layers121910401008 PRATIK ADHIKARYNessuna valutazione finora

- 5 Chapter 6 Network ModelDocumento30 pagine5 Chapter 6 Network ModelMir Md Mofachel HossainNessuna valutazione finora

- WB Set ElectronicsDocumento11 pagineWB Set ElectronicsNaveen BhatNessuna valutazione finora

- Ec3552-Vlsi and Chip Design-1251555713-Vlsi QB r2021Documento40 pagineEc3552-Vlsi and Chip Design-1251555713-Vlsi QB r2021jasmine reenaNessuna valutazione finora

- 6th Microelectronic Olympiad in Armenia (2011) - TestsDocumento12 pagine6th Microelectronic Olympiad in Armenia (2011) - TestsMohammadAmin-DNessuna valutazione finora

- Emtl Unit-VDocumento26 pagineEmtl Unit-VBck SreedharNessuna valutazione finora

- Peter H ChenDocumento10 paginePeter H ChenYunping HuangNessuna valutazione finora

- Stick DiagramDocumento21 pagineStick DiagramVani Bindal AgarwalNessuna valutazione finora

- 2008 Final Exam PaperDocumento9 pagine2008 Final Exam PaperKurisu KrisNessuna valutazione finora

- 26-Scope and Definition of Network Models, Minimum Spanning Tree Algorithm-04-02-2023Documento12 pagine26-Scope and Definition of Network Models, Minimum Spanning Tree Algorithm-04-02-2023pegan22525Nessuna valutazione finora

- Vlsi Design Unit IDocumento39 pagineVlsi Design Unit ISaurabh KatiyarNessuna valutazione finora

- Transmission Lines CH 2Documento12 pagineTransmission Lines CH 2Richard JoserNessuna valutazione finora

- Basic Physical Design AN: Unit 3Documento17 pagineBasic Physical Design AN: Unit 3Shrey MalikNessuna valutazione finora

- Stick DiagramsDocumento34 pagineStick DiagramsNagaraju NeelaNessuna valutazione finora

- Network ModelsDocumento32 pagineNetwork ModelsWesal RefatNessuna valutazione finora

- Explain Small Signal AC Characteristics of MOSFET With Its Design EquationsDocumento11 pagineExplain Small Signal AC Characteristics of MOSFET With Its Design EquationsradhikasontakayNessuna valutazione finora

- Microelectronic CircuitDocumento696 pagineMicroelectronic CircuitImtiaz AhmedNessuna valutazione finora

- RF AND MICROWAVE ENGINEERING - Nov/Dec 2011 Anna University Previous Year Model Question PaperDocumento3 pagineRF AND MICROWAVE ENGINEERING - Nov/Dec 2011 Anna University Previous Year Model Question PapereldhosejmNessuna valutazione finora

- Midterm 07Documento10 pagineMidterm 07ubertomeNessuna valutazione finora

- Progress in Electromagnetics Research C, Vol. 9, 171-182, 2009Documento12 pagineProgress in Electromagnetics Research C, Vol. 9, 171-182, 2009thuantndtvt2883Nessuna valutazione finora

- 2020-Dec ECD-412 50Documento2 pagine2020-Dec ECD-412 50Sahil ChoudharyNessuna valutazione finora

- UNIT-1 Objective QuestionsDocumento15 pagineUNIT-1 Objective Questionshyndavi0% (1)

- Layout ExamplesDocumento13 pagineLayout Examplesnazibhd786Nessuna valutazione finora

- Physical Design of CMOS Chips in Six Easy StepsDocumento14 paginePhysical Design of CMOS Chips in Six Easy StepskjvivekNessuna valutazione finora

- Assignment: Advance Routing and Protocol Topics: 1) Dijkstra'S Algorithm 2) Spanning Tree 3) Shortest PathDocumento7 pagineAssignment: Advance Routing and Protocol Topics: 1) Dijkstra'S Algorithm 2) Spanning Tree 3) Shortest Pathmirubaig6781Nessuna valutazione finora

- Assignment 5Documento1 paginaAssignment 5Vineesh VsNessuna valutazione finora

- Mcqs All ComputerDocumento88 pagineMcqs All ComputerQamar NangrajNessuna valutazione finora

- 17EC63Documento23 pagine17EC63LittiNessuna valutazione finora

- Exam 1 ECE 410 Fall 2002Documento5 pagineExam 1 ECE 410 Fall 2002Bereket LemmaNessuna valutazione finora

- CMOS Layout: Mask LayersDocumento5 pagineCMOS Layout: Mask LayerschittajitsarkarsterNessuna valutazione finora

- Exam 2012 Eng20121211Documento21 pagineExam 2012 Eng20121211enekoNessuna valutazione finora

- 2012 HW 1 PDFDocumento1 pagina2012 HW 1 PDFEmre şirinNessuna valutazione finora

- Microwave - Experiment 5 - Coupler DesignDocumento27 pagineMicrowave - Experiment 5 - Coupler DesignbangntsuNessuna valutazione finora

- Layout Design: 18-322 Fall 2003Documento40 pagineLayout Design: 18-322 Fall 2003Sai SadiqNessuna valutazione finora

- Discrete and Microstrip Coupler Design: ObjectiveDocumento10 pagineDiscrete and Microstrip Coupler Design: Objectivep.mallikarjunaNessuna valutazione finora

- Mob Net 2012 Exam SolutionDocumento16 pagineMob Net 2012 Exam SolutionMohammad IrsheadNessuna valutazione finora

- 264 Objective Questions On SonetsdhDocumento28 pagine264 Objective Questions On SonetsdhEmily AlphonseNessuna valutazione finora

- Vlsi Design: Time: 3 Hours Total Marks: 100Documento4 pagineVlsi Design: Time: 3 Hours Total Marks: 100Shivani VarshneyNessuna valutazione finora

- Unit 1 Basic MOS Technology: Figure 1. Moore's LawDocumento18 pagineUnit 1 Basic MOS Technology: Figure 1. Moore's LawSushruth SastryNessuna valutazione finora

- Introduction To Networks: 15.053 March 22, 2007Documento60 pagineIntroduction To Networks: 15.053 March 22, 2007Ehsan SpencerNessuna valutazione finora

- Clock Design Guide 6 PCB Layout ConsiderationsDocumento21 pagineClock Design Guide 6 PCB Layout ConsiderationsjtcostNessuna valutazione finora

- 10 Stickdiagrams PDFDocumento55 pagine10 Stickdiagrams PDFrdanwaraNessuna valutazione finora

- ITN524 Midterm PDFDocumento4 pagineITN524 Midterm PDF_Vezir_Nessuna valutazione finora

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionDa EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNessuna valutazione finora

- Error-Correction on Non-Standard Communication ChannelsDa EverandError-Correction on Non-Standard Communication ChannelsNessuna valutazione finora

- VTU ECE 7th Sem Embedded System Design Assignment Questions & Answers PDFDocumento60 pagineVTU ECE 7th Sem Embedded System Design Assignment Questions & Answers PDFSUSHANTH K J88% (8)

- Unit 4 Memory ManagementDocumento43 pagineUnit 4 Memory ManagementSUSHANTH K J100% (1)

- VTU 1st Year Basic Electronics Transducer Notes PDFDocumento20 pagineVTU 1st Year Basic Electronics Transducer Notes PDFSUSHANTH K J50% (2)

- Implementation of INVERTER and BUFFER Operations by Single MOSFETDocumento6 pagineImplementation of INVERTER and BUFFER Operations by Single MOSFETSUSHANTH K JNessuna valutazione finora

- Unit-1.1 INTRODUCTION AND OVERVIEW OF OPERATING SYSTEMSDocumento19 pagineUnit-1.1 INTRODUCTION AND OVERVIEW OF OPERATING SYSTEMSSUSHANTH K JNessuna valutazione finora

- Vlsi Basic Viva Questions and Answers PDFDocumento12 pagineVlsi Basic Viva Questions and Answers PDFAnonymous BVp7iZNessuna valutazione finora

- Fundamentals of CMOS VLSI Assignment Questions With Answers (VTU Syllabus)Documento71 pagineFundamentals of CMOS VLSI Assignment Questions With Answers (VTU Syllabus)SUSHANTH K J100% (1)

- Vlsi Lab Manual (10ecl77) : Bearys Institute of TechnologyDocumento96 pagineVlsi Lab Manual (10ecl77) : Bearys Institute of TechnologySUSHANTH K JNessuna valutazione finora

- Unit-1 Multimedia Communications: Multimedia Is Used To Indicate That The Information/data BeingDocumento140 pagineUnit-1 Multimedia Communications: Multimedia Is Used To Indicate That The Information/data BeingSUSHANTH K JNessuna valutazione finora

- 09-03-2023 Ramadhan - Small PDFDocumento13 pagine09-03-2023 Ramadhan - Small PDFAmmarah RamnarainNessuna valutazione finora

- 6 Elements of A Healthy ChurchDocumento2 pagine6 Elements of A Healthy ChurchJayhia Malaga JarlegaNessuna valutazione finora

- Ranbaxy Acquisition by DaiichiDocumento9 pagineRanbaxy Acquisition by Daiichirupe59Nessuna valutazione finora

- PepsiCo Strategic Plan Design PDFDocumento71 paginePepsiCo Strategic Plan Design PDFdemereNessuna valutazione finora

- ZPPF ChallanDocumento1 paginaZPPF ChallanGunasekhar ReddyNessuna valutazione finora

- Pricelist Jan 2023Documento7 paginePricelist Jan 2023Rahmat FadilNessuna valutazione finora

- Production of BiodieselDocumento49 pagineProduction of Biodieselteja100% (1)

- Food Safety and StandardsDocumento8 pagineFood Safety and StandardsArifSheriffNessuna valutazione finora

- Project On Brand Awareness of ICICI Prudential by SajadDocumento99 pagineProject On Brand Awareness of ICICI Prudential by SajadSajadul Ashraf71% (7)

- ADM3346A Midterm Fall 2010 SolutionDocumento10 pagineADM3346A Midterm Fall 2010 SolutionJohn BecksNessuna valutazione finora

- Vbulletin 5 Connect: Quick Start Guide (Ver 1.0)Documento21 pagineVbulletin 5 Connect: Quick Start Guide (Ver 1.0)dantevasquezNessuna valutazione finora

- FBL ManualDocumento12 pagineFBL Manualaurumstar2000Nessuna valutazione finora

- Ped Med HandbookDocumento27 paginePed Med HandbookSoad Shedeed0% (1)

- 8051 Development Board Circuit DiagramDocumento1 pagina8051 Development Board Circuit DiagramRohan DharmadhikariNessuna valutazione finora

- Save Energy Save EarthDocumento2 pagineSave Energy Save EarthMega Ayu100% (2)

- Crime Report Management SystemDocumento49 pagineCrime Report Management SystemAbimbolaÀdésíréAdegbiteNessuna valutazione finora

- 2 Days Meat Processing Training Program (Kalayaan Laguna)Documento2 pagine2 Days Meat Processing Training Program (Kalayaan Laguna)Jals SaripadaNessuna valutazione finora

- FIN323 Project 2021-2022Documento6 pagineFIN323 Project 2021-2022saleem razaNessuna valutazione finora

- I-Lt-Cyclomax 3.7-3Documento10 pagineI-Lt-Cyclomax 3.7-3Luis Fernando OrtigozaNessuna valutazione finora

- SQA Plan TemplateDocumento105 pagineSQA Plan Templatestudent1291Nessuna valutazione finora

- Management of HondaDocumento8 pagineManagement of HondafarhansufiyanNessuna valutazione finora

- Part 04 - Plumbing, Mechanical & Firefighting SpecificationsDocumento210 paginePart 04 - Plumbing, Mechanical & Firefighting Specificationsvtalex100% (1)

- 2.1 Article On Reasonable Compensation Job Aid 4-15-2015Documento3 pagine2.1 Article On Reasonable Compensation Job Aid 4-15-2015Michael GregoryNessuna valutazione finora

- Introduction To Investment AppraisalDocumento43 pagineIntroduction To Investment AppraisalNURAIN HANIS BINTI ARIFFNessuna valutazione finora

- Vandex CrystallineDocumento12 pagineVandex CrystallineJoseph ChenNessuna valutazione finora

- API Design GiudeDocumento9 pagineAPI Design GiudeTamilarasi DhanakodiNessuna valutazione finora

- Minimalist CV ResumeDocumento1 paginaMinimalist CV ResumeSijith MathewNessuna valutazione finora

- Basic Principles of Immunology: Seminar OnDocumento43 pagineBasic Principles of Immunology: Seminar OnDr. Shiny KajalNessuna valutazione finora

- Cronbach's AlphaDocumento4 pagineCronbach's AlphaHeide Orevillo Apa-apNessuna valutazione finora