Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

l01 Intro

Caricato da

Tamzidul Hoque TonmoyDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

l01 Intro

Caricato da

Tamzidul Hoque TonmoyCopyright:

Formati disponibili

CPE 626

Advanced VLSI Design

Aleksandar Milenkovic

http://www.ece.uah.edu/~milenka

http://www.ece.uah.edu/~milenka/cpe626-04F/

milenka@ece.uah.edu

Assistant Professor

Electrical and Computer Engineering Dept.

University of Alabama in Huntsville

Advanced VLSI Design

Computer Engineering Methodology

Market

Implementation

Complexity

Evaluate Existing

Systems for

Bottlenecks

Technology

Trends

Implement Next

Generation System

Applications

Benchmarks

Simulate New

Designs and

Organizations

Workloads

Advanced VLSI Design

Technology Directions:

SIA Roadmap

Year

1999 2002 2005

Feature size (nm)

Logic trans/cm2

Cost/trans (mc)

#pads/chip

Clock (MHz)

Chip size (mm2)

Wiring levels

Power supply (V)

High-perf pow (W)

180

130

6.2M 18M

1.735 .580

1867 2553

1250 2100

340

430

6-7

7

1.8

1.5

90

130

100

39M

.255

3492

3500

520

7-8

1.2

160

2008 2011 2014

70

50

35

84M 180M 390M

.110 .049 .022

4776 6532 8935

6000 10000 16900

620

750

900

8-9

9

10

0.9

0.6

0.5

170

175

183

Advanced VLSI Design

Intel: First 30+ Years

3 x 4 mm

Intel 4004

November 15, 1971

4-bit ALU, 108 KHz, 2,300

transistors,

10-micron technology

Intel Pentium 4

August 27, 2001

32-bit architecture, 1.4 GHz

(now 3.08), 42M transistors

(now 55+M), 0.18-micron

technology (now 0.09)

146 mm sq

Advanced VLSI Design

Future Applications

Desktop: 90% of cycles

will be spent on media applications

video encode/decode, polygon & image-based graphics

audio processing, compression, music,

speech recognition/synthesis

modulation/demodulation at audio and video rates

Scientific desktops:

high-performance FPs and graphics

Commercial servers: support for databases and

transaction processing, enhancement for reliability, support for

scalability

Embedded computing:

special support for graphics or video,

power limitations

Advanced VLSI Design

Gajski and Kuhns Y Chart

Architectural

Behavioral

Structural

Algorithmic

Systems

Functional Block

Processor

Hardware Modules

Algorithms

Logic

ALUs, Registers

Register Transfer

Circuit Gates, FFs

Logic

Transistors

Transfer Functions

Rectangles

Cell, Module Plans

Floor Plans

Domains

Clusters

Functional operations performed by the system

Physical Partitions

Structural how the system is composed

Geometry how the system is laid out in physical space

Physical/Geometry

LaCASA IP Library

Advanced VLSI Design

The Need for IP Cores

Benefits

of HDL-based design

Portability

Technology independence

Design cycle reduction

Automatic synthesis and

Logic optimization

But, the gap between

available chip complexity

and design productivity

continues to increase

Chip Complexity

58% / year

Design productivity

21% / year

Use IP cores

LaCASA IP Library

Advanced VLSI Design

New Generation of Designers

Emphasis on hierarchical IP core design

Design systems, not components!

Understand hardware/software co-design

Understand and explore design tradeoffs between

complexity, performance, and power consumption

Design a soft processor/micro-controller core

LaCASA IP Library

Advanced VLSI Design

UAH Library of Soft Cores

Microchips PIC18 micro-controller

Microchips PIC16 micro-controller

Intels 8051

ARM Integer CPU core

FP10 Floating-point Unit (ARM)

Advanced Encryption Standard (AES)

Video Processing System on a Chip

LaCASA IP Library

Advanced VLSI Design

Design Flow for CPU Cores

Reference

Manual

Instruction

Set Analysis

Dpth&Cntr

Design

VHDL Model

Verification

Synthesis&

Implementation

ASM Test

Programs

C

Programs

MPLAB IDE

C Compiler

iHex2Rom

LaCASA IP Library

Advanced VLSI Design

Soft IP Engineering Cycle

Encompasses all

relevant steps

Design

Improvements

Measurements

(Compl.&Perf.&Power)

FPGA

Implementation

Specification

Design

Modeling

Simulation &

Verification

Put together knowledge

in digital design, HDLs,

computer architecture,

programming

languages

State-of-the-art devices

Work in teams

LaCASA IP Library

Advanced VLSI Design

PIC18 Greetings

http://www.ece.uah.edu/~milenka/pic18/pic.html

Advanced VLSI Design

Designing a simple CPU in 60 minutes

LaCASA step-by-step tutorial

http://www.ece.uah.edu/~lacasa/tutorials/mu0/mu0tutorial.html

Design, verify, implement, and prototype

a rudimentary processor MU0

Modeling using VHDL

Simulation using ModelSim

Implement using Xilinx ISE and

a SpartanII device

Advanced VLSI Design

MU0 A Simple Processor

4 bits

opcode

Instruction format

Instruction set

Instruction

Opcode

Effect

LDA S

0000

ACC := mem16[S]

STO S

0001

mem16[S] := ACC

ADD S

0010

ACC := ACC + mem16[S]

SUB S

0011

ACC := ACC - mem16[S]

JMP S

0100

PC := S

JGE S

0101

if ACC >= 0 PC := S

JNE S

0110

if ACC !=0 PC := S

STP

0111

stop

12 bits

S

Advanced VLSI Design

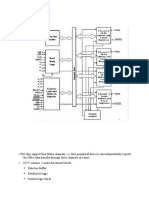

MU0 Datapath Example

Program Counter PC

Accumulator - ACC

Arithmetic-Logic Unit ALU

Instruction Register

Instruction Decode and

Control Logic

address bus

Follow the principle that the

memory will be limiting

factor in design: each

instruction takes exactly the

number of clock cycles

defined by the number of

memory accesses it must

take.

PC

control

IR

memory

ALU

ACC

data bus

Advanced VLSI Design

MU0 Datapath Design

Assume that each instruction

starts when it has arrived in

the IR

Step 1: EX (execute)

LDA S: ACC <- Mem[S]

STO S: Mem[S] <- ACC

ADD S: ACC <- ACC +

Mem[S]

SUB S: ACC <- ACC Mem[S]

JMP S: PC <- S

JGE S: if (ACC >= 0) PC <- S

JNE S: if (ACC != 0) PC <- S

Step 2: IF (fetch the next

instruction)

Either PC or the address in

the IR is issued to fetch the

next instruction

address is incremented in

the ALU and value saved

into the PC

Initialization

Reset input to start

executing instructions from

a known address; here it is

000hex

provide zero at the ALU

output and then load it into

the PC register

Advanced VLSI Design

MU0 RTL Organization

memory

Control Logic

Asel

Bsel

ACCce (ACC change

enable)

PCce (PC change enable)

IRce (IR change enable)

ACCoe (ACC output enable)

ALUfs (ALU function select)

MEMrq (memory request)

RnW (read/write)

Ex/ft (execute/fetch)

MEMrq

RnW

IRce

MU0

IR

opcode

PC

ACCoe

PCce

Asel

ALUf s

ALU

ACCce

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

MU0 control

logic

In p ut s

Op c o de Ex / f t ACC1 5

In s t ruc t i o n

Re s e t ACCz

Reset

xxxx

1

x

x

x

LDA S

0000

0

0

x

x

0000

0

1

x

x

STO S

0001

0

0

x

x

0001

0

1

x

x

ADD S

0010

0

0

x

x

0010

0

1

x

x

SUB S

0011

0

0

x

x

0011

0

1

x

x

JMP S

0100

0

x

x

x

JGE S

0101

0

x

x

0

0101

0

x

x

1

JNE S

0110

0

x

0

x

0110

0

x

1

x

STOP

0111

0

x

x

x

Out p ut s

Bs el

PCc e ACCo e

MEMrq Ex / f t

As e l ACCc e IRc e

ALUf s

Rn W

0

0

1

1

1

0

=0

1

1

0

1

1

1

0

0

0

=B

1

1

1

0

0

0

1

1

0

B+1

1

1

0

1

x

0

0

0

1

x

1

0

1

0

0

0

1

1

0

B+1

1

1

0

1

1

1

0

0

0

A+B

1

1

1

0

0

0

1

1

0

B+1

1

1

0

1

1

1

0

0

0

A-B

1

1

1

0

0

0

1

1

0

B+1

1

1

0

1

0

0

1

1

0

B+1

1

1

0

1

0

0

1

1

0

B+1

1

1

0

0

0

0

1

1

0

B+1

1

1

0

1

0

0

1

1

0

B+1

1

1

0

0

0

0

1

1

0

B+1

1

1

0

1

x

0

0

0

0

x

0

1

0

Advanced VLSI Design

LDA S (0000)

Ex/ft = 0

Ex/ft = 1

memory

memory

MEMrq

RnW

IRce

MU0

MEMrq

RnW

IRce

IR

IR

opcode

opcode

PC

PC

ACCoe

PCce

Asel

ACCoe

PCce

Asel

B+1

ALUf s

ALU

ALUf s

Bsel

ACC

mux

ALU

ACCce

ACCce

ACC[15]

ACCz

MU0

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

STO S (0001)

Ex/ft = 0

Ex/ft = 1

memory

MEMrq

RnW

memory

IRce

MU0

MEMrq

IR

RnW

IRce

IR

opcode

opcode

PC

PC

ACCoe

PCce

Asel

ALUf s

ACCoe

PCce

Asel

x ALU

B+1ALU

ALUf s

ACCce

ACC[15]

ACCz

Bsel

mux

ACCce

ACC

MU0

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

ADD S (0010)

Ex/ft = 0

Ex/ft = 1

memory

MEMrq

RnW

memory

IRce

MU0

MEMrq

IR

RnW

IRce

IR

opcode

opcode

PC

PC

ACCoe

PCce

Asel

ALUf s

ACCoe

PCce

Asel

A+B

ALU

ALUf s

ACCce

ACC[15]

ACCz

Bsel

mux

B+1

ALU

ACCce

ACC

MU0

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

SUB S (0011)

Ex/ft = 0

Ex/ft = 1

memory

MEMrq

RnW

memory

IRce

MU0

MEMrq

IR

RnW

IRce

IR

opcode

opcode

PC

PC

ACCoe

PCce

Asel

ALUf s

ACCoe

PCce

Asel

A-B

ALU

ALUf s

ACCce

ACC[15]

ACCz

Bsel

mux

B+1

ALU

ACCce

ACC

MU0

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

JMP S (0100)

Ex/ft = 0

memory

MEMrq

RnW

IRce

MU0

IR

opcode

PC

ACCoe

PCce

Asel

ALUf s

B+1

ALU

ACCce

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

JGE S (0101)

Ex/ft = 0,

ACC15 = 0

Ex/ft = 0,

ACC15 = 1

memory

memory

MEMrq

RnW

IRce

MU0

MEMrq

RnW

IRce

IR

IR

opcode

opcode

PC

PC

ACCoe

PCce

Asel

ALUf s

B+1

ALU

ACCoe

PCce

Asel

ALUf s

Bsel

ACC

mux

B+1

ALU

ACCce

ACCce

ACC[15]

ACCz

MU0

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

JNE S (0110)

Ex/ft = 0,

ACCz = 0

Ex/ft = 0,

ACCz = 1

memory

memory

MEMrq

RnW

IRce

MU0

MEMrq

RnW

IRce

IR

IR

opcode

opcode

PC

PC

ACCoe

PCce

Asel

ALUf s

B+1

ALU

ACCoe

PCce

Asel

ALUf s

Bsel

ACC

mux

B+1

ALU

ACCce

ACCce

ACC[15]

ACCz

MU0

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

STP (001)

Ex/ft = 0

memory

MEMrq

RnW

IRce

MU0

IR

opcode

PC

ACCoe

PCce

Asel

ALUf s

xALU

ACCce

ACC[15]

ACCz

Bsel

ACC

mux

Advanced VLSI Design

Reset

Ex/ft = 0

memory

MEMrq

IRce

RnW

MU0

IR

opcode

PC

PCce

Asel

ALUf s

ACCoe

0

ALU

ACCce

ACC[15]

ACCz

Bsel

ACC

mux

Potrebbero piacerti anche

- VLSI HomeworkDocumento23 pagineVLSI HomeworkTamzidul Hoque TonmoyNessuna valutazione finora

- Ieee Tables and FiguresDocumento1 paginaIeee Tables and FiguresBrianHoNessuna valutazione finora

- Interconnect Intro FPGADocumento50 pagineInterconnect Intro FPGATamzidul Hoque TonmoyNessuna valutazione finora

- Interconnect Intro FPGADocumento50 pagineInterconnect Intro FPGATamzidul Hoque TonmoyNessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (120)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- ISO 27001 ControlsDocumento20 pagineISO 27001 ControlsNarasimha Rao AkundiNessuna valutazione finora

- ABB FOX Firewall AFF650 PDFDocumento2 pagineABB FOX Firewall AFF650 PDFOscar Mercado GarcíaNessuna valutazione finora

- Chapter 3: Introduction To C/Al Programming: Training ObjectivesDocumento8 pagineChapter 3: Introduction To C/Al Programming: Training ObjectivescapodelcapoNessuna valutazione finora

- CS303 System Software Syllabus-Semesters - 5Documento5 pagineCS303 System Software Syllabus-Semesters - 5Tv VarunNessuna valutazione finora

- Blade AutomationDocumento3 pagineBlade AutomationcadcamnxNessuna valutazione finora

- Big Data Analytics For Dynamic Energy Management in Smart GridsDocumento9 pagineBig Data Analytics For Dynamic Energy Management in Smart Gridsakshansh chandravanshiNessuna valutazione finora

- Cisc Vs RiscDocumento15 pagineCisc Vs RiscGấm Gà100% (1)

- CMISEDocumento21 pagineCMISEPranay Rao100% (1)

- SteganographyDocumento32 pagineSteganographysubashreeNessuna valutazione finora

- SWC FullManualDocumento313 pagineSWC FullManualmikebeil1Nessuna valutazione finora

- Cse Agent Oriented ProgrammingDocumento13 pagineCse Agent Oriented ProgrammingBhanusree100% (1)

- iSU ABAP Level 1 Internal TablesDocumento40 pagineiSU ABAP Level 1 Internal Tablesandreea_liviana100% (1)

- Unit 4 AIX Software Installation and MaintenanceDocumento21 pagineUnit 4 AIX Software Installation and MaintenanceRichie BallyearsNessuna valutazione finora

- Eminar On Omputer Etwork SecurityDocumento17 pagineEminar On Omputer Etwork SecuritySubhasmita PatelNessuna valutazione finora

- User Manual For Patient Management SystemDocumento39 pagineUser Manual For Patient Management SystemShivani VermaNessuna valutazione finora

- Red BootDocumento2 pagineRed BootErwin Balajadia Dela CruzNessuna valutazione finora

- Multi-Core ArchitecturesDocumento43 pagineMulti-Core Architecturesvinotd1100% (1)

- Lec 1-Intro To ComputerDocumento18 pagineLec 1-Intro To ComputerJoshua BrownNessuna valutazione finora

- RV ToolsDocumento94 pagineRV ToolsVakul BhattNessuna valutazione finora

- 8257 DmaDocumento6 pagine8257 DmaAdarsh AmzeNessuna valutazione finora

- Lab 19 - Network AnalysisDocumento36 pagineLab 19 - Network AnalysisUno de MadridNessuna valutazione finora

- Robust Correlation of Encrypted Attack TrafficDocumento8 pagineRobust Correlation of Encrypted Attack TrafficVinaya Kumar SNessuna valutazione finora

- DS Lab 7 - Linked List Implementation As Stack and QueueDocumento12 pagineDS Lab 7 - Linked List Implementation As Stack and QueueASIM ZUBAIR 111Nessuna valutazione finora

- An A-Z Index of The Windows CMD Command LineDocumento4 pagineAn A-Z Index of The Windows CMD Command LineLeo. D'Alençon R.Nessuna valutazione finora

- Odoo DevelopmentDocumento127 pagineOdoo Developmentkikwete100% (1)

- 01 ChF01 IntroductionDocumento13 pagine01 ChF01 IntroductionSalam BaderNessuna valutazione finora

- Assignment 7 Voting System Java ProgramDocumento9 pagineAssignment 7 Voting System Java Programchitranshpandey100% (1)

- Mid PDFDocumento99 pagineMid PDFKIt ChanNessuna valutazione finora

- 8086 MicroprocessorDocumento114 pagine8086 MicroprocessorsaiNessuna valutazione finora

- Development and Test Methodology Boeing Jeppesen JDMDocumento7 pagineDevelopment and Test Methodology Boeing Jeppesen JDMtechgeekvnNessuna valutazione finora