Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

FF Basics: SR, D, JK, T Types & Conversions in <40 Chars

Caricato da

rdb003Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

FF Basics: SR, D, JK, T Types & Conversions in <40 Chars

Caricato da

rdb003Copyright:

Formati disponibili

FLIP FLOPS

1.Definition

2.Basic Flip Flop Types(SR,D,JK,T)

3.Conversion of 1 FF to Other

By: Sourabh Bhardwaj

Definition:

In electronics a flip-flop or latch is a circuit that

has two stable states and can be used to store

state information. The circuit can be made to

change state by signals applied to one or more

control inputs and will have one or two outputs.

It is the basic storage element in sequential logic.

Flip-flops and latches are a fundamental building block

of digital electronics systems used in computers,

communications, and many other types of systems.

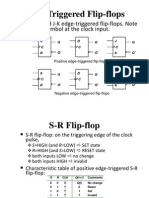

Types Of Traditional Flip-Flops

SR

D

T

JK

The SET/RESET FLIP FLOP

Schematic Symbol

RS Flip-Flop

A RS-flip flop is the simplest possible memory element.

It is constructed by feeding the outputs of two NOR gates back to the other NOR gates input.

The inputs R and S are referred to as the Reset and Set inputs, respectively.

To understand the operation of the RS-flipflop (or RS-latch) consider the following scenarios:

S=1 and R=0: The output of the bottom NOR gate is equal to zero, Q'=0.

Hence both inputs to the top NOR gate are equal to one, thus, Q=1.

Hence, the input combination S=1 and R=0 leads to the flipflop being set to Q=1.

S=0 and R=1: Similar to the arguments above, the outputs become Q=0 and Q'=1.

We say that the flipflop is reset.

S=0 and R=0: Assume the flipflop is set (Q=0 and Q'=1), then the output of the top NOR

gate remains at Q=1 and the bottom NOR gate stays at Q'=0.

Similarly, when the flipflop is in a reset state (Q=1 and Q'=0), it will remain there with

this input combination.

Therefore, with inputs S=0 and R=0, the flipflop remains in its state.

S=1 and R=1: This input combination must be avoided.

R S Q Q' Comment

0 0 Q Q' Hold state

0 1 1 0 Set

1 0 0 1 Reset

1 1 ? ? Avoid

We can summarize the operation of the RS-flipflop by the following truth

table.

Note, the output Q' is simply the inverse of Q.

An RS flipflop can also be constructed from NAND gates.

Truth Table of S-R Flip-Flop

Clk S R Qn Qn+1

0 0 0 0 No Change

0 0 0 1 No Change

1 0 0 0 0

1 0 0 1 1

1 0 1 0 0

1 0 1 1 0

1 1 0 0 1

1 1 0 1 1

1 1 1 0

Dont do

1 1 1 1

Characteristics Table Of SR Flip-Flop

S R Qn Qn+1 Operation

0 0 0 0 No-operation

0 0 1 1

0 1 0 0 RESET -

operation

0 1 1 0

1 0 0 1 SET operation

1 0 1 1

1 1 0 Dont do

1 1 1

Qn = before rising edge of CLOCK

Qn+1 = after rising edge of CLOCK

Excitation Table For The Clocked SR

Flip-Flop

Qn Qn+1 S R

0 0 0 Dont care

RESET but no

SET

0 1 1 0 Definite SET &

no RESET

1 0 0 1 Definite RESET

& no SET

1 1 0 Dont care SET

but no RESET

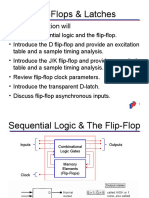

D Flip-Flop

Schematic Symbol of Clocked D Flip Flop

D-FLIP FLOP

An RS-flipflop is rarely used in actual sequential logic.

However, it is the fundamental building block for the very useful D-flipflop.

The D-flipflop has only a single data input.

That data input is connected to the S input of an RS-flip flop, while the inverse of D

is connected to the R input.

This prevents that the input combination ever occurs.

To allow the flipflop to be in a holding state, a D-flip flop has a second input called

``Enable.''

The Enable-input is AND-ed with the D-input, such that when Enable=0, the R and

S inputs of the RS-flipflop are 0 and the state is held.

When the Enable-input is 1, the S input of the RS flipflop equals the D input and R

is the inverse of D.

Hence, the value of D determines the value of the output Q when Enable is 1.

When Enable returns to 0, the most recent input D is ``remembered.''

Truth Table of Clocked D-Flip-Flop

Clk D Qn Qn+1

0 0 0 No Change

0 1 1 No Change

1 0 0 0

1 0 1 0

1 1 0 1

1 1 1 1

Characteristics Table as well as TT

of D FF

D Qn Qn+1 Operation

0 0 0 RESET-operation

0 1 0

1 0 1 SET -operation

1 1 1

Qn = before rising edge of CLOCK

Qn+1 = after rising edge of CLOCK

Excitation Table For The Clocked D

Flip-Flop

Qn Qn+1 D

0 0 0

0 1 1

1 0 0

1 1 1

The T Flip-Flop

Truth Table of T Flip-Flop

Clk T Qn Qn+1

0 0 0 No Change

0 1 1 No Change

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 0

Characteristics Table of T FF

T Qn Qn+1 Operation

0 0 0 RESET-operation

0 1 1 SET -operation

1 0 1 SET -operation

1 1 0 RESET-operation

Qn = before rising edge of CLOCK

Qn+1 = after rising edge of CLOCK

Excitation Table For The Clocked T

Flip-Flop

Qn Qn+1 T

0 0 0

0 1 1

1 0 1

1 1 0

The Clocked JK FLIP-FLOP

Truth Table of JK Flip-Flop

Clk J K Qn Qn+1

0 0 0 0 No Change

0 0 0 1 No Change

1 0 0 0 0

1 0 0 1 1

1 0 1 0 0

1 0 1 1 0

1 1 0 0 1

1 1 0 1 1

1 1 1 0

1

1 1 1 1 0

Characteristics Table Of JK Flip-Flop

J K Qn Qn+1 Operation

0 0 0 0 Reset

0 0 1 1 Set

0 1 0 0 RESET

0 1 1 0 RESET

1 0 0 1 SET

1 0 1 1 SET

1 1 0 1 SET

1 1 1 0 RESET

Qn = before rising edge of CLOCK

Qn+1 = after rising edge of CLOCK

Excitation Table For The Clocked JK

Flip-Flop

Qn Qn+1 J K

0 0 0 Dont care K

but no J

0 1 1 Definite J &

Dont K

1 0 1 Definite K &

Dont care for J

1 1 0 Definite K= 0 &

Dont care for J

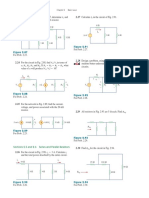

Design of Clocked Flip-Flop

Steps To Flip-Flop Design

STEP 1 : Given a Characteristic Table

prescribing some desired operation examine

each entry of this table (both inputs & output

desired), & answer the following question for

each row of the table:-

1) Does the cell need to be SET for this

condition, or would a SET cause the wrong

transition (SET or SET)?

Step to Flip-Flop Design

2) Does the cell need to be RESET for this

condition, or would a RESET cause the wrong

transition (RESET or RESET)?

3) Does the cell need to be left alone?

STEP2: Based on the answer to the questions

above & the resultant Truth-Table, plot a SET

MAP & RESET MAP & derive the

combinational logic for the SET/RESET

DECODER.

Designing of Clocked SR FF

CLK S R Qn Qn+1 SET RESET

0 0 0 0 0 0 No SET, RESET

0 0 0 1 1 0 SET, NO RESET

0 0 1 0 0 0

0 0 1 1 1 0

0 1 0 0 0 0 Input Can happen with no CLK

therefore optional

0 1 0 1 1 0

0 1 1 0 0 0

0 1 1 1 1 0

1 0 0 0 0 0

1 0 0 1 1 0

1 0 1 0 0 0

1 0 1 1 0 0 1 No SET, YES RESET

1 1 0 0 1 1 0 YES SET, NO RESET

1 1 0 1 1 0 SET, No RESET

1 1 1 0 Input conditions must not happen

1 1 1 1

Characteristic Table Truth Table For S & R

Decoder

Designing of Clocked SR Flip -Flop

From above table we will draw K-Map For SET

& RESET DECODER to get required Boolean

Expressions.

Potrebbero piacerti anche

- Elevator FSMDocumento10 pagineElevator FSMNguyễn Đức Tuấn0% (1)

- Counter DesignDocumento18 pagineCounter Designapi-3756871100% (1)

- MD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5Documento17 pagineMD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5shyburrahaman120Nessuna valutazione finora

- UNIT1Documento37 pagineUNIT1Azliana Mohd Taib0% (1)

- Introduction to Electronics Sequential Circuit DesignDocumento27 pagineIntroduction to Electronics Sequential Circuit Design11kumarvishal4Nessuna valutazione finora

- SEQUENTIAL CIRCUITS: LATCHES, FLIP-FLOPS, AND THEIR APPLICATIONSDocumento32 pagineSEQUENTIAL CIRCUITS: LATCHES, FLIP-FLOPS, AND THEIR APPLICATIONSN Sandeep KumarNessuna valutazione finora

- DigitalLogic - FlipFlop CircuitDocumento30 pagineDigitalLogic - FlipFlop CircuitNasa McAikenNessuna valutazione finora

- Sequential CircuitDocumento7 pagineSequential CircuitmadhavNessuna valutazione finora

- Characteristics of flip-flops (SR, D, JK, TDocumento4 pagineCharacteristics of flip-flops (SR, D, JK, TShekhar ShuklaNessuna valutazione finora

- Flip Flops: Name - Marada Shamita Experiment No. - 9 Roll No. - 2101116 Date - 10Documento9 pagineFlip Flops: Name - Marada Shamita Experiment No. - 9 Roll No. - 2101116 Date - 10MOHIT MISHRANessuna valutazione finora

- DCLD Unit 3Documento57 pagineDCLD Unit 3sanskritijha.csNessuna valutazione finora

- L9,10 Flip FlopsDocumento24 pagineL9,10 Flip Flopsdomainname9Nessuna valutazione finora

- Name:-Bharat Arora Section: - A Rollno: - 18 University Rollno: - 191500212Documento6 pagineName:-Bharat Arora Section: - A Rollno: - 18 University Rollno: - 191500212Deepam AsnaniNessuna valutazione finora

- Sequential Circuits: Presented By: Group 3Documento30 pagineSequential Circuits: Presented By: Group 3Jalaj SrivastavaNessuna valutazione finora

- Flip FlopsDocumento18 pagineFlip FlopsveNessuna valutazione finora

- Flip Flop and LatchDocumento7 pagineFlip Flop and LatchAnn RazonNessuna valutazione finora

- Flip Flop CircuitsDocumento8 pagineFlip Flop CircuitsFadi NajjarNessuna valutazione finora

- Lab # 6: Study of Various Flip-Flop CircuitsDocumento8 pagineLab # 6: Study of Various Flip-Flop CircuitsmovabNessuna valutazione finora

- SEQUENTIAL LOGIC CIRCUITSDocumento34 pagineSEQUENTIAL LOGIC CIRCUITSibraheembello31Nessuna valutazione finora

- DLLec8b NotesDocumento9 pagineDLLec8b NotesChintan MandalNessuna valutazione finora

- Understanding Flip-FlopsDocumento11 pagineUnderstanding Flip-Flopsamiethurgat100% (2)

- Edge-Triggered Flip-Flops and Their TypesDocumento27 pagineEdge-Triggered Flip-Flops and Their TypesUsama NaveedNessuna valutazione finora

- Sequential Logic - Flip-Flops: 6.1 SR LatchDocumento5 pagineSequential Logic - Flip-Flops: 6.1 SR Latchanon020202Nessuna valutazione finora

- Day 9 GCDocumento11 pagineDay 9 GCEffecure HealthcareNessuna valutazione finora

- Sequential Circuits: Latches and Flip-FlopsDocumento32 pagineSequential Circuits: Latches and Flip-FlopsRohan BorgalliNessuna valutazione finora

- EE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Documento19 pagineEE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Shehab RamadanNessuna valutazione finora

- CS1104 – Computer Organization Lectures: Sequential Logic Latches & Flip-flopsDocumento30 pagineCS1104 – Computer Organization Lectures: Sequential Logic Latches & Flip-flopsTaye ToluNessuna valutazione finora

- Sequential Logic Circuits ExplainedDocumento56 pagineSequential Logic Circuits ExplainedBonsa100% (1)

- Unit 5 Sequential CircuitDocumento21 pagineUnit 5 Sequential CircuitAnurag GoelNessuna valutazione finora

- Multiplexer, Decoder and FlipflopDocumento10 pagineMultiplexer, Decoder and FlipflopShachi P GowdaNessuna valutazione finora

- Combinational vs Sequential Circuits Flip-FlopsDocumento21 pagineCombinational vs Sequential Circuits Flip-FlopsRafinNessuna valutazione finora

- Types of Flip-Flops: Electronics Computing Digital Circuit Bit Memory Input Clock Output ComplementDocumento4 pagineTypes of Flip-Flops: Electronics Computing Digital Circuit Bit Memory Input Clock Output ComplementVikas KumarNessuna valutazione finora

- Topic 5 - Flip Flops Sequential CircuitsDocumento16 pagineTopic 5 - Flip Flops Sequential CircuitsShivneet KumarNessuna valutazione finora

- CS1104 Lecture 11: Sequential Logic Latches & Flip-flopsDocumento30 pagineCS1104 Lecture 11: Sequential Logic Latches & Flip-flopssansureNessuna valutazione finora

- Latches and Flipflops: Presented By: Pankaj Pratim Hazarika Etc 5 SemesterDocumento11 pagineLatches and Flipflops: Presented By: Pankaj Pratim Hazarika Etc 5 SemesterPankaj Pratim HazarikaNessuna valutazione finora

- Digital Design FundamentalsDocumento25 pagineDigital Design FundamentalsnileshchaurasiaNessuna valutazione finora

- Flip-Flop Experiment AnalysisDocumento8 pagineFlip-Flop Experiment Analysisgerand salazarNessuna valutazione finora

- Sequential CircuitsDocumento8 pagineSequential Circuits망토Nessuna valutazione finora

- Logic Circuits: Fundamentals of Instrumentation and ControlDocumento26 pagineLogic Circuits: Fundamentals of Instrumentation and ControlRana MohsinNessuna valutazione finora

- Flip FlopsDocumento40 pagineFlip Flopszohaiba338Nessuna valutazione finora

- Flip FlopsDocumento24 pagineFlip FlopsSovon BasuNessuna valutazione finora

- Chapter 2.2Documento15 pagineChapter 2.2OzzyNessuna valutazione finora

- DS - Expt 10Documento6 pagineDS - Expt 10Aditya SalunkheNessuna valutazione finora

- Flipflops: Technical Seminar ReportDocumento16 pagineFlipflops: Technical Seminar ReportrachitNessuna valutazione finora

- Flip FlopsDocumento53 pagineFlip FlopsmoretejhonadrianNessuna valutazione finora

- Digital Electronics: Flip-Flops - D, T, J-K Types & Waveforms ExplainedDocumento17 pagineDigital Electronics: Flip-Flops - D, T, J-K Types & Waveforms ExplainedRongeet SodhiNessuna valutazione finora

- JK Flip FlopDocumento11 pagineJK Flip FlopprakashpacetNessuna valutazione finora

- COA Mod2Documento29 pagineCOA Mod2Ananya P.SNessuna valutazione finora

- Basic Flip Flops in Digital ElectronicsDocumento10 pagineBasic Flip Flops in Digital ElectronicsDharneeshkarDandyNessuna valutazione finora

- L2 FlipflopsDocumento39 pagineL2 FlipflopsKogul ShiyamNessuna valutazione finora

- Latches&FFsDocumento9 pagineLatches&FFssanjeevani rawatNessuna valutazione finora

- FlipFlops Chapter 5Documento27 pagineFlipFlops Chapter 5jenny khanNessuna valutazione finora

- Understanding Flip-FlopsDocumento35 pagineUnderstanding Flip-FlopsKaustav MitraNessuna valutazione finora

- DE Module 03Documento20 pagineDE Module 03Rishabh TiwariNessuna valutazione finora

- Practical 11: AIM: To Study JK Flip Flop Circuit. TheoryDocumento2 paginePractical 11: AIM: To Study JK Flip Flop Circuit. Theoryyagnesh100% (1)

- Basic Flip Flop Circuits ExplainedDocumento7 pagineBasic Flip Flop Circuits ExplainedFord StephenNessuna valutazione finora

- 4. Sequential LogicDocumento22 pagine4. Sequential Logictemesgenbekele371Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- PNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGDa EverandPNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGNessuna valutazione finora

- TCP/IP Introduction Explains Protocols Like IP, TCP and UDPDocumento26 pagineTCP/IP Introduction Explains Protocols Like IP, TCP and UDPrdb003Nessuna valutazione finora

- Overview of TCP-IP1Documento56 pagineOverview of TCP-IP1maruthi631Nessuna valutazione finora

- IipDocumento28 pagineIiprdb003Nessuna valutazione finora

- Mat KholnaDocumento45 pagineMat Kholnardb003Nessuna valutazione finora

- IipDocumento28 pagineIiprdb003Nessuna valutazione finora

- Higher Algebra - Hall & KnightDocumento593 pagineHigher Algebra - Hall & KnightRam Gollamudi100% (2)

- Con Formal MappingDocumento29 pagineCon Formal Mappingrdb003Nessuna valutazione finora

- CAT 910 Basic CircuiteDocumento6 pagineCAT 910 Basic CircuiteYober Emilio Nato AcostaNessuna valutazione finora

- N-Channel Logic Level Enhancement Mode Field Effect TransistorDocumento5 pagineN-Channel Logic Level Enhancement Mode Field Effect TransistorheruNessuna valutazione finora

- Dual Trace Phase Measurement Method Lissajous Pattern ExperimentDocumento10 pagineDual Trace Phase Measurement Method Lissajous Pattern ExperimentFallou GayeNessuna valutazione finora

- Renesas M51995AFP#CF0J DatasheetDocumento41 pagineRenesas M51995AFP#CF0J DatasheetheribertosfaNessuna valutazione finora

- Flying Saucer PDFDocumento2 pagineFlying Saucer PDFShrivlsi RamNessuna valutazione finora

- Icom ICV8Documento31 pagineIcom ICV8john solasNessuna valutazione finora

- Oscillator ManualDocumento22 pagineOscillator ManualckooipgNessuna valutazione finora

- Logic Gates Questions and AnswersDocumento3 pagineLogic Gates Questions and AnswersInstrumentation ToolsNessuna valutazione finora

- 11timing Concepts and Physical DesignDocumento42 pagine11timing Concepts and Physical DesignTeja Reddy100% (2)

- ENG 571 - Lecture - Notes - Week - 7 - Part - 1Documento8 pagineENG 571 - Lecture - Notes - Week - 7 - Part - 1Vinod KumarNessuna valutazione finora

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDocumento5 pagineDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezNessuna valutazione finora

- Second Order FilterDocumento18 pagineSecond Order Filteryoubora2903Nessuna valutazione finora

- Differential Amplifier Using BJTDocumento11 pagineDifferential Amplifier Using BJTAssini HussainNessuna valutazione finora

- MAX44267 +15V Single-Supply, Dual Op Amp With 10V Output RangeDocumento19 pagineMAX44267 +15V Single-Supply, Dual Op Amp With 10V Output RangegirimooliNessuna valutazione finora

- Waveform Generators and Nonlinear Circuits: 3.1 Zero-Crossing DetectorsDocumento15 pagineWaveform Generators and Nonlinear Circuits: 3.1 Zero-Crossing DetectorsAndrewNessuna valutazione finora

- Manual IC F4013 PDFDocumento32 pagineManual IC F4013 PDFFabián Peña AlvearNessuna valutazione finora

- Digital VLSI Design Standard Cell Libraries: Semester A, 2016-17 Lecturer: Dr. Adam TemanDocumento32 pagineDigital VLSI Design Standard Cell Libraries: Semester A, 2016-17 Lecturer: Dr. Adam TemanThi NguyenNessuna valutazione finora

- 12v Ac DC Mc34063 Led Buck DriverDocumento7 pagine12v Ac DC Mc34063 Led Buck DriverDaxiana FrigottoNessuna valutazione finora

- Boss SD-1 Replica Instructions: Based On The ITS8 PCBDocumento3 pagineBoss SD-1 Replica Instructions: Based On The ITS8 PCBНиколай ПрокопенкоNessuna valutazione finora

- Multiple Array Matrix High-Density Eplds: Cy7C340 Epld FamilyDocumento7 pagineMultiple Array Matrix High-Density Eplds: Cy7C340 Epld FamilyArizal ThamalaNessuna valutazione finora

- Assignment 1Documento4 pagineAssignment 1azimNessuna valutazione finora

- PIC16F87XA: 12.0 Comparator ModuleDocumento7 paginePIC16F87XA: 12.0 Comparator ModuleJoe FernandezNessuna valutazione finora

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocumento3 pagineSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationJavier Mendoza CastroNessuna valutazione finora

- 78S40Documento0 pagine78S40Pravin MevadaNessuna valutazione finora

- Vlsi Faq PDF FreeDocumento311 pagineVlsi Faq PDF FreeWelly Nagh Seven Fold0% (1)

- Integrado de Plancha RemingtonDocumento99 pagineIntegrado de Plancha RemingtonAndrey serrano hidalgoNessuna valutazione finora

- Amazing All-Band ReceiverDocumento8 pagineAmazing All-Band ReceiverjhonkayNessuna valutazione finora

- Transistor As A Switch: Electronics and Communication Circuits Lab. Experiment #6Documento5 pagineTransistor As A Switch: Electronics and Communication Circuits Lab. Experiment #6Eng. Ahmad ELsamakNessuna valutazione finora

- Thevenin's Theorem: SolutionDocumento30 pagineThevenin's Theorem: SolutionRaghupatiNessuna valutazione finora