Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Ee314 5

Caricato da

Keerthi Vasan STitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Ee314 5

Caricato da

Keerthi Vasan SCopyright:

Formati disponibili

Chapter 5

Interrupt processing

Objectives:

The difference between hardware and software interrupts

The difference between maskable and nonmaskable interrupts

Interrupt processing procedures

The vector address table

Multiple interrupts and interrupt priorities

Special function interrupts

The general requirement of all interrupt handlers

EE314

Microprocessor Systems

Based on "An Introduction to the Intel Family of Microprocessors" by James L. Antonakos

5.2 Hardware and Software Interrupts

The nonmaskable interrupt is

generated by en external device,

trough a rising edge on the NMI pin.

The maskable interrupts (0FFH)

can be generated by:

an external device, trough a high logic

level on the INTR pin (the external

device has to specify the interrupt

number).

(IF (interrupt flag) in FLAGS register

enables or disables (masks) the P to

accept maskable interrupts.)

microprocessor itself (i.e. when trying

to divide by 0), (the interrupt number

is hardware defined).

Software interrupts (exceptions) using the INT instruction

(followed by the interrupt number (type)).

Hardware

interrupts

Generates a Type 2 interrupt (address

0008H in the Interrupt vector table)

Cannot be ignored by the microprocessor.

Interrupt priority

Divide-error Highest

INT, INTO

NMI

INTR

Single-step Lowest

5.3 The Interrupt Vector Table

(or Interrupt Pointer Table)

The memory block from address 00000 to 003FF. There are 1024 bytes, each of the 256

maskable interrupts uses four bytes to store the address where the corresponding ISR

(Interrupt Service Routine) begins. The ISR address for interrupt number xx is stored

beginning at address xx*4, in form CS:IP. From low to high address, the bytes are stored

in the order: IP low, IP high, CS low and CS high (byte swapping).

Consequences: After RESET the P cannot begin running from physical address 00000.

The first instruction is fetched at address FFFF0H.

Before using an interrupt, its corresponding ISR address has to be stored

in the interrupt vector table.

ISRs are handled as FAR routines (both CS and IP specified).

Vectors 0 to 18 are predefined, 19 to 31 are reserved by Intel, 32 to 255 are

unassigned (free to use):

Vector Description

0 Divide error

1 Debugger call (single step)

2 NMI

3 Breakpoint

4 INTO

5 BOUND range exceeded

6 Invalid opcode

7 Device not available

8 Double fault

9 Reserved

Vector Description

10 Invalid task state segment (protected mode)

11 Segment not present (protected mode)

12 Stack exception

13 General protection

14 Page fault (protected mode)

15 Reserved

16 Floating-point error

17 Alignment check

18 Machine check

19 - 31 Reserved

32 - 255 Maskable interrupts (nonreserved)

5.4 The Interrupt Processing Sequence

IF=1 Interrupt not accepted

Inform external

devices that an

interrupt acknowledge

cycle began

External devices

requesting an

interrupt transmits

trough data bus the

interrupt type

second INTA cycle

read interrupt type on

Data Bus

The interrupt

type is

predefined

The interrupt

type is the

operand

Hardware INTR

no

NMI

Software

Interrupts

Save processor information on stack:

- FLAGS register

- Return address = CS:IP

Internal

HW Int.

IF=1

Interrupt not accepted

no

yes

yes

Clear IF and TF (no further

maskable interrupts allowed)

ISR execution

Fetch the address of the ISR:

- CS:IP from Interrupt Vector Table

at address 4*(interrupt type)

first INTA cycle

(8086 - INTA pin = low)

(Pentium -

M/IO,D/C,W/R,ADS = 0)

5.5 Multiple Interrupts

NMI

The interrupt

type is

predefined

Execution of 1 instruction

ISR execution

(non NMI)

NMI

Save processor

information on stack:

- FLAGS register

- Return address = CS:IP

no

Fetch the address of the NMI ISR

Clear IF and TF (no further

maskable interrupts allowed)

yes

IRET

no

Load processor

information from stack:

- Return address = CS:IP

- FLAGS register

Return to

interrupted

program

IRET

Load processor

information from stack:

- Return address = CS:IP

- FLAGS register

NMI ISR execution

Execution of

all instructions

Interrupt request has to stay active until acknowledged:

5.6 Special Interrupts

Divide Error: type 0, hardware

generated by the P when quotient

doesnt fit in destination (division by 0)

0400:1100 B3 00 MOV BL,0

0400:1102 F6 F3 DIV BL

0400:1104 .

generates a type 0

interrupt.

return address

Single step: type 1, hardware

generated by the P (if TF=1) after

each instruction. After pushing

flags onto stack, TF is cleared (IF

also), so ISR itself is not

interrupted. Returning after ISR, the

flags are restored, another interrupt

is generated after next instruction.

A program example to set or reset the TF:

PUSHF

POP AX

OR AX,100H

PUSH AX

POPF

PUSHF

POP AX

OR AX,100H

PUSH AX

POPF

moves FLAGS to AX

updates TF

moves AX to FLAGS

NMI: type 2, hardware generated by an

external device on emergent events (i.e.

power fail). Rising edge active.

Breakpoint: type 3, software generated

by a single-byte instruction, INT 3.

0400:1100 3C 00 CMP AL,0

0400:1102 75 01 JNZ XYZ

0400:1104 EE OUT DX,AL

0040:1105 FE C0 XYZ: INC AL

Replaced by INT 3 code (CCH)

by setting a breakpoint.

Overflow: type 4, generated by INTO

instruction if OF=1.

External maskable interrups:

type 0-255 via INTR pin

P generates two pulses on INTA pin. During

the second pulse, the external device has to put

on data bus (D0D7) the interrupt type.

5.6 Special Interrupts

Interrupts may occur in unexpected

moments during main program

execution (i.e. between setting of a flag

as result of an arithmetical instruction

and the subsequent conditional jump

hanging on the flag value). After

returning from ISR, the main program

has to continue undisturbed by changes

made in Ps internal state

(environment or context): flags,

registers.

MYISR: PUSHA

POPA

IRET

The interrupt acknowledge

mechanism saves FLAGS and return

address, but no register content.

The Interrupt Service Routine (ISR)

is responsible for saving all the used

registers value on stack (PUSH), and

to recover it (POP) before returning.

Usually, all registers are saved

(PUSHA) and recovered (POPA)

An ISR can perform multiple functions

hanging on the value of an input parameter

(i.e. the value in the AH register).

Before occurrence of the interrupt (usualy

a software one) the value of the parameter

is prepared.

The corresponding ISR tests the parameter

and perform the action required by its

value.

5.6 Special Interrupts

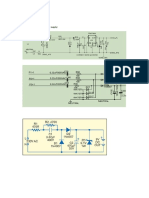

A simple circuit able to place an 8-bit interrupt number (type) onto data bus

...

INTR

AD7

.

. 8088

.

AD0

INTA

74LS

244

(octal

buffer)

G1 G2

+5V

8 x 4.7K

Interrupt

request

INTR

INTA

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

0

0

0

0

1

1

0

0

P is reading

the byte on

AD7AD0

INTR can deactivate after activation of INTA

first active pulse of INTA

second active pulse of INTA

The octal buffer outputs are three-state

Data BUS is free for carrying data

between P and other devices in system

The octal buffer controls the Data BUS.

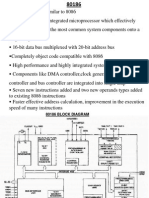

5.6 Special Interrupts

A simple prioritized interrupt circuitry

...

INTR

AD7

.

. 8088

.

AD0

INTA

P interrupt

request

1

1

0

1

0

0

0

0

P is reading

the byte on

AD7AD0

INT 0D0H

requested

INTA deactivates INTR

first active pulse of INTA

second active pulse of INTA

The octal buffer outputs are three-state

Data BUS is free for carrying data

between P and other devices in system

The octal buffer

controls the Data BUS.

+5V

4.7K

74LS

374

(octal

flip-

flop)

OE

(priority

encoder)

E1 GS

+5V

4.7K

D Q

CLR

INT0

INT2

.

.

INT7

INT2 request

INT2

INTR

INTA

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

5.7 Interrupt Service Routines

Simple example: one second time interval generator using a 60Hz signal on NMI

; ISR for NMI

NMITIME: DEC COUNT ;decrement 60ths counter, (COUNT)(COUNT)-1

;(ZF)1 if (COUT)=0

JNZ EXIT ;did we go to 0?, jump only if (ZF)=0

MOV COUNT, 60 ;yes, reload the counter, (COUNT)3Ch

CALL FAR PTR ONESEC ;call ONESEC, [SP-1],[SP-2] (CS),

;[SP-3],[SP-4]EXIT,(SP)(SP)-4

;reverse action when return from ONESEC

EXIT: IRET ;(IP)[SP],[SP+1], (CS)[SP+2],[SP+3],

;(FLAGS)[SP+4],[SP+5], (SP)(SP)+6,

;reverse action to what

;happened accepting NMI

; main program slide preparing the action of NMIs ISR

MOV COUNT, 60 ;init 60ths counter , (COUNT)3Ch

PUSH DS ;save current DS content , [SP-1],[SP-2] (DS),(SP) (SP)-2

SUB AX, AX ;set new DS content to 0000, (AX) 0

MOV DS, AX ;(DS) 0

LEA AX, NMITIME ;load address of NMITIME ISR, (AX) NMITIME

MOV [8], AX ;store IP address in IPT, replacing regular NMIs ISR address

;[8],[9] NMITIME

MOV AX, CS ;store CS address in IPT, (AX) (CS)=current code segment

MOV [0AH], AX ;[0Ah],[0Bh] (CS)

POP DS ;get old DS content back, (DS) [SP],[SP+1], (SP) (SP)+2

5.7 Interrupt Service Routines

Simple example: A Divide-Error Handler

; preparing the error message in DATA segment

.DATA

DIVMSG DB Division by zero attempted!$

;first character, D, at address DIVMSG in DATA segment

; ISR for Divide-Error

DIVERR: PUSH SI ;save current SI content , [SP-1],[SP-2] (SI),(SP) (SP)-2

MOV AX, 101h ;load result with default, (AX) 101h

SUB DX, DX ;clear DX, (DX) 0

LEA SI, DIVMSG ;init pointer to error message, (SI) DIVMSG

;(passing parameter trough register)

CALL FAR PTR DISPMSG ;output error message, [SP-1],[SP-2] (CS),

;[SP-3],[SP-4]return address,(SP)(SP)-4

;reverse action when return from DISPMSG

POP SI ;get old SI content back, (SI) [SP],[SP+1], (SP) (SP)+2

IRET ;(IP)[SP],[SP+1], (CS)[SP+2],[SP+3] =return address =

;(the address of the first instruction

;after the DIV generating the error)

;(FLAGS)[SP+4],[SP+5], (SP)(SP)+6,

;reverse action to what happened accepting INT 0

If a divide error occurs, the ISR will load AX wit 101h, and DX with 0. A error message will

be displayed. The error message is in DATA segment beginning at address DIVMSG and

ends wit a $ character. The DISPMSG procedure (subroutine) (not shown) displays the

character string found in DATA segment until the first $ character. ISR address has to be

loaded (not shown) at address 0000 in the IPT (INT 0).

5.7 Interrupt Service Routines

Simple example: An ISR with Multiple Functions

; ISR for INT 20H

ISR20H: CMP AH, 4 ;AH must be 0-3 only

;(?)(AH)-4, (ZF)1 if (?)=0, (CF)1 if (?)<0 (unsigned)

;(OF)1 if (?)<-128 or (?)>127,

;(PF)1 if (?) contains an even number of 1s,

;(AF) if a transport from bit 3 to bit 4 occurred,

;(SF) if (?)<0 (signed)

JNC EXIT ;AH >3, ISR returns without any effect

CMP AH, 0 ;AH = 0 ?, (?)(AH)-0, (ZF)1 if (?)=0, ...

JZ ADDAB ;AH = 0, jump to add function

CMP AH, 1 ;AH = 1 ?, (?)(AH)-1, (ZF)1 if (?)=0, ...

JZ SUBAB ;AH = 1, jump to subtract function

CMP AH, 2 ;AH = 2 ?, (?)(AH)-4, (ZF)1 if (?)=0, ...

JZ MULAB ;AH = 2, jump to multiply function

DIVAB: DIV BL ;AH = 3, use divide function

IRET

ADDAB: ADD AL, BL ;add function

IRET

SUBAB: SUB AL, BL ;subtraction function

IRET

MULAB: MUL BL ;multiply function

IRET

; main program has to store the address of INT 20s ISR at address 80h in IPT.

Potrebbero piacerti anche

- Lec 7 NotesDocumento7 pagineLec 7 NotesJafar HussainNessuna valutazione finora

- Interrupts Part 1Documento14 pagineInterrupts Part 1leemong335Nessuna valutazione finora

- Advanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. PDocumento46 pagineAdvanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. Pvishu212167% (3)

- InterruptDocumento25 pagineInterruptPallvi BhardwajNessuna valutazione finora

- Interrupts in 8086Documento4 pagineInterrupts in 8086Radhakrishna100% (1)

- 3 Mod3Documento19 pagine3 Mod3Sagar ChaulagaiNessuna valutazione finora

- DSPDocumento63 pagineDSPNishita ParuchuriNessuna valutazione finora

- Module III - Stack and InterruptsDocumento27 pagineModule III - Stack and InterruptsSNEHA MARIYA TOMNessuna valutazione finora

- Mic Module IVDocumento11 pagineMic Module IVroshnibijuNessuna valutazione finora

- Software and Hardware Interrupt ApplicationsDocumento10 pagineSoftware and Hardware Interrupt Applicationssatyanarayana12Nessuna valutazione finora

- Experiment - 5 InterruptsDocumento4 pagineExperiment - 5 InterruptsEC100 Diya SoniNessuna valutazione finora

- Iii Unit Mpi Part ADocumento5 pagineIii Unit Mpi Part AN.RAMAKUMARNessuna valutazione finora

- Real Time Control - InterruptsDocumento39 pagineReal Time Control - InterruptsmkrishnadNessuna valutazione finora

- 8086 Interrupts: InterruptDocumento5 pagine8086 Interrupts: InterruptN.RAMAKUMARNessuna valutazione finora

- Assignment ON Microprocessor AND Microcontroller: Joyal Jose AugustineDocumento63 pagineAssignment ON Microprocessor AND Microcontroller: Joyal Jose Augustineajas777BNessuna valutazione finora

- Iii Unit Mpi Part ADocumento16 pagineIii Unit Mpi Part ADarshan BysaniNessuna valutazione finora

- 3002 Microprocessor - S4 - InterruptDocumento13 pagine3002 Microprocessor - S4 - InterruptLim Yee FattNessuna valutazione finora

- MPC555Documento27 pagineMPC555Mohammad Gulam AhamadNessuna valutazione finora

- In The Real Mode, Each of These Instructions Fetches A Vector From The Vector Table, and Then Calls The Procedure Stored at The Location Addressed by The VectorDocumento5 pagineIn The Real Mode, Each of These Instructions Fetches A Vector From The Vector Table, and Then Calls The Procedure Stored at The Location Addressed by The Vectorsaqib idreesNessuna valutazione finora

- Interrupts & Related Instructions Types of Data TransferDocumento4 pagineInterrupts & Related Instructions Types of Data TransferKirthi RkNessuna valutazione finora

- Interrupts in Personal Computers: Experiment #6Documento10 pagineInterrupts in Personal Computers: Experiment #6Asaad HalayqaNessuna valutazione finora

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocumento8 pagineCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- Interrupts & PollingDocumento10 pagineInterrupts & Pollingwazazzu3349Nessuna valutazione finora

- Description Alternate FunctionDocumento8 pagineDescription Alternate FunctionnareshhhhhNessuna valutazione finora

- 8 8086 InterruptsDocumento26 pagine8 8086 InterruptsAnshuman MitraNessuna valutazione finora

- Delhi Technological University Assignment Embedded SystemsDocumento9 pagineDelhi Technological University Assignment Embedded Systemssatinder singhNessuna valutazione finora

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocumento8 pagineCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- 8086 InterruptsDocumento24 pagine8086 InterruptsAshwini ManojNessuna valutazione finora

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocumento8 pagineCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- Hardware Interrupts: Thorne: 21.1, 21.3 Thorne: 21.1, 21.3 (Irvine Edition IV: Section 16.4)Documento79 pagineHardware Interrupts: Thorne: 21.1, 21.3 Thorne: 21.1, 21.3 (Irvine Edition IV: Section 16.4)babanpNessuna valutazione finora

- QuestionsDocumento4 pagineQuestionsGökdenizNessuna valutazione finora

- 8086 Processor InterruptsDocumento5 pagine8086 Processor InterruptsSheikh Noor MohammadNessuna valutazione finora

- Sdsafgdshgfvnbvnvnvnb: Description Alternate FunctionDocumento8 pagineSdsafgdshgfvnbvnvnvnb: Description Alternate FunctionnareshhhhhNessuna valutazione finora

- Microprpcessor 8086Documento29 pagineMicroprpcessor 8086amanNessuna valutazione finora

- Description Alternate Function: SFDFDGFBGFDocumento8 pagineDescription Alternate Function: SFDFDGFBGFnareshhhhhNessuna valutazione finora

- Interrupt 8086Documento24 pagineInterrupt 8086Aarti KushwahaNessuna valutazione finora

- MODULE 3 MPDocumento20 pagineMODULE 3 MPrinsha. febnNessuna valutazione finora

- 8086 InterruptDocumento10 pagine8086 Interruptavireddy1Nessuna valutazione finora

- XC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBDocumento8 pagineXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBnareshhhhhNessuna valutazione finora

- Assembly Mid AnswerDocumento5 pagineAssembly Mid AnswerskpheroNessuna valutazione finora

- VCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBDocumento8 pagineVCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBnareshhhhhNessuna valutazione finora

- An Over View of 8085Documento12 pagineAn Over View of 8085nskprasad89Nessuna valutazione finora

- Xddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgfvnbvnvnvn B: Descriptio N Alternate FunctionDocumento8 pagineXddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgfvnbvnvnvn B: Descriptio N Alternate FunctionnareshhhhhNessuna valutazione finora

- Part 3Documento27 paginePart 3Ogunranti RasaqNessuna valutazione finora

- PIC18Documento112 paginePIC18Keshav Reddy100% (1)

- Chap5 InterruptsDocumento22 pagineChap5 InterruptscriNessuna valutazione finora

- CH 8Documento13 pagineCH 8Gcross NGNessuna valutazione finora

- Pin No. Pin Name Description Alternate FunctionDocumento7 paginePin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- InterruptsDocumento34 pagineInterruptsJaney24100% (1)

- AVR313: Interfacing The PC AT Keyboard: 8-Bit Microcontroller Application NoteDocumento13 pagineAVR313: Interfacing The PC AT Keyboard: 8-Bit Microcontroller Application Notejagesh chaturvediNessuna valutazione finora

- 8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Documento30 pagine8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Arif Febrian MuhammadNessuna valutazione finora

- CH 5 AdditionalDocumento34 pagineCH 5 AdditionalKriti GautamNessuna valutazione finora

- 02 NuMicro Architecture CMSISDocumento42 pagine02 NuMicro Architecture CMSISRagowo Tri WicaksonoNessuna valutazione finora

- Interrupts in 8086 MicroprocessorDocumento8 pagineInterrupts in 8086 MicroprocessorGemechis GurmesaNessuna valutazione finora

- Asm ch13Documento96 pagineAsm ch13Angelica May BangayanNessuna valutazione finora

- Unit 1Documento27 pagineUnit 1meetsanthoshNessuna valutazione finora

- InterruptsDocumento34 pagineInterruptssharathchandraNessuna valutazione finora

- The 8086 Interrupt Mechanism: The 8259A PICDocumento14 pagineThe 8086 Interrupt Mechanism: The 8259A PICSatishNessuna valutazione finora

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- 1.4 SelectionDocumento51 pagine1.4 SelectionKeerthi Vasan SNessuna valutazione finora

- Candle Sticks: Support Level HammerDocumento8 pagineCandle Sticks: Support Level HammerKeerthi Vasan SNessuna valutazione finora

- 1.6 FunctionDocumento49 pagine1.6 FunctionKeerthi Vasan SNessuna valutazione finora

- 1.1 Introduction To CDocumento57 pagine1.1 Introduction To CKeerthi Vasan SNessuna valutazione finora

- 3.5B Enumeration: Department of CSEDocumento9 pagine3.5B Enumeration: Department of CSEKeerthi Vasan SNessuna valutazione finora

- Using If ElseDocumento5 pagineUsing If ElseKeerthi Vasan SNessuna valutazione finora

- Algorithms 3: CTPS 2018Documento16 pagineAlgorithms 3: CTPS 2018Keerthi Vasan SNessuna valutazione finora

- Three-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaDocumento7 pagineThree-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaKeerthi Vasan SNessuna valutazione finora

- Three-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaDocumento12 pagineThree-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaKeerthi Vasan SNessuna valutazione finora

- 3.2 String FunctionsDocumento20 pagine3.2 String FunctionsKeerthi Vasan SNessuna valutazione finora

- RM17TE00 DATASHEET NG en-GBDocumento6 pagineRM17TE00 DATASHEET NG en-GBKeerthi Vasan SNessuna valutazione finora

- 3.3 StructuresDocumento24 pagine3.3 StructuresKeerthi Vasan SNessuna valutazione finora

- Market Radar: Traders' CornerDocumento5 pagineMarket Radar: Traders' CornerKeerthi Vasan SNessuna valutazione finora

- AC Current Measurements Using Hall-Effect Sensors - Engineer Experiences PDFDocumento10 pagineAC Current Measurements Using Hall-Effect Sensors - Engineer Experiences PDFKeerthi Vasan SNessuna valutazione finora

- 3.7 Command-Line ArgumentsDocumento18 pagine3.7 Command-Line ArgumentsKeerthi Vasan SNessuna valutazione finora

- 1.7 RecursionDocumento23 pagine1.7 RecursionKeerthi Vasan SNessuna valutazione finora

- Bitwise Operations in Embedded Programming - Detail ExplanationDocumento6 pagineBitwise Operations in Embedded Programming - Detail ExplanationKeerthi Vasan SNessuna valutazione finora

- Economical Test of Internal Adc in Embedded Systems: Josef Vedral, Jakub Svatoš, Pavel FexaDocumento4 pagineEconomical Test of Internal Adc in Embedded Systems: Josef Vedral, Jakub Svatoš, Pavel FexaKeerthi Vasan SNessuna valutazione finora

- Transformerless R-C Power SupplyDocumento4 pagineTransformerless R-C Power SupplyKeerthi Vasan SNessuna valutazione finora

- V-Guard Industries Limited Code of Conduct For Directors and Senior ManagementDocumento4 pagineV-Guard Industries Limited Code of Conduct For Directors and Senior ManagementKeerthi Vasan SNessuna valutazione finora

- Interfacing Stepper Motor With 8051 Using Keil C - AT89C51Documento10 pagineInterfacing Stepper Motor With 8051 Using Keil C - AT89C51Keerthi Vasan SNessuna valutazione finora

- 1-32-Bit Microprocessor - Intel 80386Documento37 pagine1-32-Bit Microprocessor - Intel 80386afzal_a67% (3)

- x86 Instruction ListingsDocumento53 paginex86 Instruction ListingsHardav RavalNessuna valutazione finora

- S11 InterruptsDocumento69 pagineS11 InterruptsThesisRequirementNessuna valutazione finora

- Assembly Mid AnswerDocumento5 pagineAssembly Mid AnswerskpheroNessuna valutazione finora

- CS401 Solved Subjective Final Term by JunaidDocumento25 pagineCS401 Solved Subjective Final Term by Junaidasimtoqeer458Nessuna valutazione finora

- 8086 Third Term TopicsDocumento46 pagine8086 Third Term TopicsgandharvsikriNessuna valutazione finora

- DCA1104 & Understanding PC & Troubleshooting - Siddharth PalDocumento8 pagineDCA1104 & Understanding PC & Troubleshooting - Siddharth Palsiddharthpscs6Nessuna valutazione finora

- Unit 3Documento53 pagineUnit 3FrederickNessuna valutazione finora

- Cs401 Finalterm Solved Subjective With ReferencesDocumento33 pagineCs401 Finalterm Solved Subjective With ReferencesMuhammad Faisal100% (1)

- 1.initial Boot SequenceDocumento94 pagine1.initial Boot SequenceTommaso Mauro TautonicoNessuna valutazione finora

- 121960-001 1983 iAPX 286 Operating Systems Writers Guide 1983Documento251 pagine121960-001 1983 iAPX 286 Operating Systems Writers Guide 1983kgrhoadsNessuna valutazione finora

- Windows 3.0 REPORTDocumento12 pagineWindows 3.0 REPORTjanellsalonga09Nessuna valutazione finora

- Unit 01 The CPUDocumento26 pagineUnit 01 The CPUSneaky pete100% (1)

- Advanced Power Management (APM) BIOS Interface Specification Revision 1.2 February 1996Documento80 pagineAdvanced Power Management (APM) BIOS Interface Specification Revision 1.2 February 1996ivanagui2Nessuna valutazione finora

- 80286Documento16 pagine80286Umang RajNessuna valutazione finora

- Malfunction's Winasm Tutorial For TASMDocumento7 pagineMalfunction's Winasm Tutorial For TASMAikone65Nessuna valutazione finora

- Features of 80386Documento13 pagineFeatures of 80386Aswathy CjNessuna valutazione finora

- Lec # 02Documento61 pagineLec # 02eshaNessuna valutazione finora

- The Von Neumann Computer ModelDocumento11 pagineThe Von Neumann Computer ModelJerome ScottNessuna valutazione finora

- The Holy Book of X86 v2 PDFDocumento53 pagineThe Holy Book of X86 v2 PDFMoustafa Al QasrawiNessuna valutazione finora

- Initialization of 80386DX, Debugging and Virtual 8086 Mode: Unit VDocumento43 pagineInitialization of 80386DX, Debugging and Virtual 8086 Mode: Unit Vshikhamailme84Nessuna valutazione finora

- 35080Documento19 pagine35080bogdan_cornea_ro522Nessuna valutazione finora

- Architecture of 80386Documento39 pagineArchitecture of 80386Jaimon JacobNessuna valutazione finora

- Windows Assembly Language and System Programming (2nd Edition) - Barry KaulerDocumento421 pagineWindows Assembly Language and System Programming (2nd Edition) - Barry KaulerFlash WingNessuna valutazione finora

- Study On Intel 80386 MicroprocessorDocumento3 pagineStudy On Intel 80386 MicroprocessorInternational Journal of Innovative Science and Research TechnologyNessuna valutazione finora

- Laboratory Manual Computer Engineering: Microprocessor LabDocumento41 pagineLaboratory Manual Computer Engineering: Microprocessor LabRutuparn SadvelkarNessuna valutazione finora

- 80286Documento12 pagine80286a_charaniaNessuna valutazione finora

- 128-Mbit, Low-Voltage, Serial Flash Memory With 54-Mhz Spi Bus InterfaceDocumento47 pagine128-Mbit, Low-Voltage, Serial Flash Memory With 54-Mhz Spi Bus InterfaceteomondoNessuna valutazione finora

- 25L2005Documento40 pagine25L2005FrancisReisNessuna valutazione finora

- Solved MCQs of CS401 PDFDocumento44 pagineSolved MCQs of CS401 PDFAli ShahzadNessuna valutazione finora