Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

FSM Slides

Caricato da

Sahil SharmaCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

FSM Slides

Caricato da

Sahil SharmaCopyright:

Formati disponibili

FINITE STATE MACHINES

By:-

Abhinav Vishnoi

Assistant Professor

Lovely Professional University

Finite State Machines (FSMs)

Finite-state machine (FSM) is a mathematical

model used to design computer

programs and digital logic circuits.

Any Circuit with Memory Is a Finite State

Machine

Even computers can be viewed as huge FSMs

Design of FSMs Involves

Defining states

Defining transitions between states

Optimization / minimization

Above Approach Is Practical for Small FSMs

Only

State diagram & State

assignment

A state diagram is a type of diagram to describe

the behavior of systems.

State diagrams require that the system

described is composed of a finite number

of states

State assignment is a specification have been

given to a combination of flip-flops and

combinational logic

State assignment is to the number of present

states in a particular circuit

N-number of flip flop 2^N state assignment

Types Of FSMs

There are two basic ways to design clocked

sequential circuits.

1. Mealy Machine

2. Moore Machine

Moore FSM

Output Is a Function of a Present State Only

Present State

Register

Next State

function

Output

function

Inputs

Present State

Next State

Outputs

clock

reset

Mealy FSM

Output Is a Function of a Present State and

Inputs

Next State

function

Output

function

Inputs

Present State

Next State

Outputs

Present State

Register

clock

reset

Moore Machine

state 1 /

output 1

state 2 /

output 2

transition

condition 1

transition

condition 2

Mealy Machine

state 1

state 2

transition condition 1 /

output 1

transition condition 2 /

output 2

Moore vs. Mealy FSM (1)

Moore and Mealy FSMs Can Be Functionally

Equivalent

Mealy FSM Has Richer Description and

Usually Requires Smaller Number of States

Smaller circuit area

Moore vs. Mealy FSM (2)

Mealy FSM Computes Outputs as soon as

Inputs Change

Mealy FSM responds one clock cycle sooner than

equivalent Moore FSM

Moore FSM - Example 1

Moore FSM that Recognizes Sequence 10

S0 / 0 S1 / 0 S2 / 1

0

0

0

1

1

1

reset

Meaning

of states:

S0: No

elements

of the

sequence

observed

S1: 1

observed

S2: 10

observed

Mealy FSM - Example 1

Mealy FSM that Recognizes Sequence 10

S0 S1

0 / 0

1 / 0 1 / 0

0 / 1

reset

Meaning

of states:

S0: No

elements

of the

sequence

observed

S1: 1

observed

Moore & Mealy FSMs

Example 1

clock

input

Moore

Mealy

0 1 0 0 0

S0 S1 S2 S0 S0

S0 S1 S0 S0 S0

Moore FSM Example 2: State diagram

C z 1 =

resetn

B z 0 = A z 0 = w 0 =

w 1 =

w 1 =

w 0 =

w 0 = w 1 =

Present

Next state

Output

state

w = 0 w = 1

z

A A B 0

B A C 0

C A C 1

Moore FSM Example 2: State table

A

w 0 = z 0 =

w 1 = z 1 = B

w 0 = z 0 =

resetn

w 1 = z 0 =

Mealy FSM Example 3: State diagram

Present

Next state Output z

state

w = 0 w = 1 w = 0 w = 1

A A B 0 0

B A B 0 1

Mealy FSM Example 3: State table

Sequential circuit design

18

Now lets reverse the process: In sequential circuit design, we turn

some description into a working circuit.

We first make a state table or diagram to express the

computation.

Then we can turn that table or diagram into a sequential circuit.

Sequence recognizers

19

A sequence recognizer is a special kind of sequential circuit that

looks for a special bit pattern in some input.

The recognizer circuit has only one input, X.

One bit of input is supplied on every clock cycle. For example, it

would take 20 cycles to scan a 20-bit input.

This is an easy way to permit arbitrarily long input sequences.

There is one output, Z, which is 1 when the desired pattern is found.

Our example will detect the bit pattern 1001:

Inputs: 1 1 1 0 0 1 1 0 1 0 0 1 0 0 1 1 0

Outputs: 0 0 0 0 0 1 0 0 0 0 0 1 0 0 1 0 0

Here, one input and one output bit appear every clock cycle.

This requires a sequential circuit because the circuit has to

remember the inputs from previous clock cycles, in order to

determine whether or not a match was found.

A basic state diagram

20

What state do we need for the sequence recognizer?

We have to remember inputs from previous clock cycles.

For example, if the previous three inputs were 100 and the current input is

1, then the output should be 1.

In general, we will have to remember occurrences of parts of the desired

patternin this case, 1, 10, and 100.

Well start with a basic state diagram:

A B C D

1/0 0/0 0/0

State Meaning

A None of the desired pattern (1001) has been input yet.

B Weve already seen the first bit (1) of the desired pattern.

C Weve already seen the first two bits (10) of the desired pattern.

D Weve already seen the first three bits (100) of the desired pattern.

Step 1: Making a state table

21

The first thing you have to figure out is precisely how the use of

state will help you solve the given problem.

Make a state table based on the problem statement. The table

should show the present states, inputs, next states and outputs.

Sometimes it is easier to first find a state diagram and then

convert that to a table.

This is usually the most difficult step. Once you have the state table,

the rest of the design procedure is the same for all sequential

circuits.

Sequence recognizers are especially hard! Theyre the hardest

example well see in this class, so if you understand this youre in

good shape.

A basic state diagram

22

What state do we need for the sequence recognizer?

We have to remember inputs from previous clock cycles.

For example, if the previous three inputs were 100 and the

current input is 1, then the output should be 1.

In general, we will have to remember occurrences of parts of the

desired patternin this case, 1, 10, and 100.

Well start with a basic state diagram:

A B C D

1/0 0/0 0/0

State Meaning

A None of the desired pattern (1001) has been input yet.

B Weve already seen the first bit (1) of the desired pattern.

C Weve already seen the first two bits (10) of the desired pattern.

D Weve already seen the first three bits (100) of the desired pattern.

Overlapping occurrences of the

pattern

23

What happens if were in state D (the last three inputs were 100), and the

current input is 1?

The output should be a 1, because weve found the desired pattern.

But this last 1 could also be the start of another occurrence of the

pattern! For example, 1001001 contains two occurrences of 1001.

To detect overlapping occurrences of the pattern, the next state should

be B.

A B C D

1/0 0/0 0/0

1/1

State Meaning

A None of the desired pattern (1001) has been input yet.

B Weve already seen the first bit (1) of the desired pattern.

C Weve already seen the first two bits (10) of the desired pattern.

D Weve already seen the first three bits (100) of the desired pattern.

Filling in the other arrows

24

Remember that we need two outgoing arrows for each node, to account for

the possibilities of X=0 and X=1.

The remaining arrows we need are shown in blue. They also allow for the

correct detection of overlapping occurrences of 1001.

A B C D

1/0 0/0 0/0

1/1

0/0

0/0

1/0

1/0

State Meaning

A None of the desired pattern (1001) has been input yet.

B Weve already seen the first bit (1) of the desired pattern.

C Weve already seen the first two bits (10) of the desired pattern.

D Weve already seen the first three bits (100) of the desired pattern.

Finally, making the state table

25

A B C D

1/0 0/0 0/0

1/1

0/0

0/0

1/0

1/0

Present

State Input

Next

State Output

A 0 A 0

A 1 B 0

B 0 C 0

B 1 B 0

C 0 D 0

C 1 B 0

D 0 A 0

D 1 B 1

input/output

presen

t

state

next

state

Remember how the state diagram

arrows correspond to rows of the

state table:

Sequential circuit design

procedure

26

Step 1:

Make a state table based on the problem statement. The table should show the

present states, inputs, next states and outputs. (It may be easier to find a state

diagram first, and then convert that to a table.)

Step 2:

Assign binary codes to the states in the state table, if you havent already. If

you have n states, your binary codes will have at least

log

2

n digits, and your circuit will have at least log

2

n flip-flops.

Step 3:

For each flip-flop and each row of your state table, find the flip-flop input values

that are needed to generate the next state from the present state. You can use

flip-flop excitation tables here.

Step 4:

Find simplified equations for the flip-flop inputs and the outputs.

Step 5:

Build the circuit!

Step 2: Assigning binary codes to

states

27

We have four states ABCD, so we need at least two flip-flops Q

1

Q

0

.

The easiest thing to do is represent state A with Q

1

Q

0

= 00, B with 01, C

with 10, and D with 11.

The state assignment can have a big impact on circuit complexity, but we

wont worry about that too much in this class.

Present

State Input

Next

State Output

A 0 A 0

A 1 B 0

B 0 C 0

B 1 B 0

C 0 D 0

C 1 B 0

D 0 A 0

D 1 B 1

Present

State Input

Next

State Output

Q

1

Q

0

X Q

1

Q

0

Z

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 1 0 0

0 1 1 0 1 0

1 0 0 1 1 0

1 0 1 0 1 0

1 1 0 0 0 0

1 1 1 0 1 1

Step 3: Finding flip-flop input

values

28

Next we have to figure out how to actually make the flip-flops change from

their present state into the desired next state.

This depends on what kind of flip-flops you use!

Well use two JKs. For each flip-flip Q

i

, look at its present and next states,

and determine what the inputs J

i

and K

i

should be in order to make that

state change.

Present

State Input

Next

State Flip flop inputs Output

Q

1

Q

0

X Q

1

Q

0

J

1

K

1

J

0

K

0

Z

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 1 0 0

0 1 1 0 1 0

1 0 0 1 1 0

1 0 1 0 1 0

1 1 0 0 0 0

1 1 1 0 1 1

Finding JK flip-flop input values

29

For JK flip-flops, this is a little tricky. Recall the characteristic table:

If the present state of a JK flip-flop is 0 and we want the next state to be 1, then

we have two choices for the JK inputs:

We can use JK=10, to explicitly set the flip-flops next state to 1.

We can also use JK=11, to complement the current state 0.

So to change from 0 to 1, we must set J=1, but K could be either 0 or 1.

Similarly, the other possible state transitions can all be done in two different

ways as well.

J K Q(t+1) Operation

0 0 Q(t) No change

0 1 0 Reset

1 0 1 Set

1 1 Q(t) Complement

JK excitation table

30

An excitation table shows what flip-flop inputs are required in order to

make a desired state change.

This is the same information thats given in the characteristic table, but

presented backwards.

J K Q(t+1) Operation

0 0 Q(t) No change

0 1 0 Reset

1 0 1 Set

1 1 Q(t) Complement

Q(t) Q(t+1) J K Operation

0 0 0 x No change/reset

0 1 1 x Set/complement

1 0 x 1 Reset/complement

1 1 x 0 No change/set

Excitation tables for all flip-flops

31

Q(t) Q(t+1) J K Operation

0 0 0 x No change/reset

0 1 1 x Set/complement

1 0 x 1 Reset/complement

1 1 x 0 No change/set

Q(t) Q(t+1) D Operation

0 0 0 Reset

0 1 1 Set

1 0 0 Reset

1 1 1 Set

Q(t) Q(t+1) T Operation

0 0 0 No change

0 1 1 Complement

1 0 1 Complement

1 1 0 No change

Back to the example

32

We can now use the JK excitation

table on the right to find the correct

values for each flip-flops inputs,

based on its present and next states.

Present

State Input

Next

State Flip flop inputs Output

Q

1

Q

0

X Q

1

Q

0

J

1

K

1

J

0

K

0

Z

0 0 0 0 0 0 x 0 x 0

0 0 1 0 1 0 x 1 x 0

0 1 0 1 0 1 x x 1 0

0 1 1 0 1 0 x x 0 0

1 0 0 1 1 x 0 1 x 0

1 0 1 0 1 x 1 1 x 0

1 1 0 0 0 x 1 x 1 0

1 1 1 0 1 x 1 x 0 1

Q(t) Q(t+1) J K

0 0 0 x

0 1 1 x

1 0 x 1

1 1 x 0

Step 4: Find equations for the FF

inputs and output

33

Now you can make K-maps and find equations for each

of the four flip-flop inputs, as well as for the output Z.

These equations are in terms of the present state and the

inputs.

The advantage of using JK flip-flops is that there are

many dont care conditions, which can result in simpler

MSP equations.

J

1

= X Q

0

K

1

= X + Q

0

J

0

= X + Q

1

K

0

= X

Z = Q

1

Q

0

X

Present

State Input

Next

State Flip flop inputs Output

Q

1

Q

0

X Q

1

Q

0

J

1

K

1

J

0

K

0

Z

0 0 0 0 0 0 x 0 x 0

0 0 1 0 1 0 x 1 x 0

0 1 0 1 0 1 x x 1 0

0 1 1 0 1 0 x x 0 0

1 0 0 1 1 x 0 1 x 0

1 0 1 0 1 x 1 1 x 0

1 1 0 0 0 x 1 x 1 0

1 1 1 0 1 x 1 x 0 1

Step 5: Build the circuit

34

Lastly, we use these simplified equations to build the

completed circuit.

J

1

= X Q

0

K

1

= X + Q

0

J

0

= X + Q

1

K

0

= X

Z = Q

1

Q

0

X

State minimization/reduction

It is a technique to avoids the introduction

of redundant state. It reduces the no. of

flip-flop and cost.

Two state said to be redundant if every

possible set of input generate exactly

same output and next state.

When two state are equivalent one of

them can be removed without altering the

input-output relationship.

Present state c & e

having same next state

and same output

State c and e are

equivalent

State e can be

removed and replaced by

c

Example

BCD to Ex-3 code converter

Potrebbero piacerti anche

- FSM DesignDocumento24 pagineFSM DesignNazim Ali100% (1)

- Tutorial 5Documento31 pagineTutorial 5Sathish KumarNessuna valutazione finora

- Introduction to Finite AutomataDocumento18 pagineIntroduction to Finite AutomataSuseela ReddyNessuna valutazione finora

- Atcd Unit 1Documento58 pagineAtcd Unit 1Sudhir Kumar SinghNessuna valutazione finora

- Unit IV Toc QB AnsDocumento38 pagineUnit IV Toc QB AnsHyper AbiNessuna valutazione finora

- Bist-Built in Self TestDocumento12 pagineBist-Built in Self TestSiddharthSharmaNessuna valutazione finora

- MIT6 01SCS11 Chap04Documento53 pagineMIT6 01SCS11 Chap04creeshaNessuna valutazione finora

- CT-4212 Theory of Automata and ComputationsDocumento39 pagineCT-4212 Theory of Automata and ComputationsAhmed NUR HUSIENNessuna valutazione finora

- ECE 301 - Digital Electronics: Sequential Logic Circuits: FSM DesignDocumento27 pagineECE 301 - Digital Electronics: Sequential Logic Circuits: FSM DesignSuman BhardwajNessuna valutazione finora

- Lecture 4. Sequential Logic 2: Prof. Taeweon Suh Computer Science Education Korea UniversityDocumento35 pagineLecture 4. Sequential Logic 2: Prof. Taeweon Suh Computer Science Education Korea UniversitySAMIT KARMAKARNessuna valutazione finora

- Unit 6 - FinalDocumento24 pagineUnit 6 - Finalsuniljain007Nessuna valutazione finora

- Automata Theory Solved McqsDocumento18 pagineAutomata Theory Solved McqsRida BaigNessuna valutazione finora

- Chapter 67Documento10 pagineChapter 67Sourav DasNessuna valutazione finora

- VLSI Design Verification and Testing: Fault SimulationDocumento5 pagineVLSI Design Verification and Testing: Fault Simulationnishantsoni90Nessuna valutazione finora

- Theory of Computation-2014 MCAM - Sc-III Sem 15.09.143 PDFDocumento74 pagineTheory of Computation-2014 MCAM - Sc-III Sem 15.09.143 PDFAkash Kashyap0% (1)

- Formal Language & Automata TheoryDocumento19 pagineFormal Language & Automata TheoryMandeep SinghNessuna valutazione finora

- Atcd-Unit-5 (1) - 2Documento32 pagineAtcd-Unit-5 (1) - 2Duggineni VarunNessuna valutazione finora

- Unit-1 Regular Languages and Finite AutomataDocumento5 pagineUnit-1 Regular Languages and Finite AutomatasukhdevsinghNessuna valutazione finora

- Adder (Electronics)Documento4 pagineAdder (Electronics)TurbosMixerNessuna valutazione finora

- Toc Unit VDocumento13 pagineToc Unit Vanilosta100% (1)

- Mealy & Moore Machine: Rao Wakeel AhmadDocumento26 pagineMealy & Moore Machine: Rao Wakeel AhmadAyesha BibiNessuna valutazione finora

- Problem Set 04Documento2 pagineProblem Set 04satishjenaNessuna valutazione finora

- Turing Machines and Computable FunctionsDocumento15 pagineTuring Machines and Computable FunctionsMatteo GiorgiNessuna valutazione finora

- Order of Complexity AnalysisDocumento9 pagineOrder of Complexity AnalysisMusic LifeNessuna valutazione finora

- Implementation of PODEM Algorithm: OutlineDocumento2 pagineImplementation of PODEM Algorithm: OutlineNivin PaulNessuna valutazione finora

- Theory of Automata - Lecture - 1Documento36 pagineTheory of Automata - Lecture - 1Julfikar RahmanNessuna valutazione finora

- L06 FAwih OutputDocumento28 pagineL06 FAwih OutputGautam KhannaNessuna valutazione finora

- Ex3 05 SolnDocumento4 pagineEx3 05 SolnethicsadimoolamNessuna valutazione finora

- CS1303 Theory of Computation-ANSWERSDocumento23 pagineCS1303 Theory of Computation-ANSWERSsridharanchandran80% (5)

- Automata Theory Chapter-Finite AutomataDocumento28 pagineAutomata Theory Chapter-Finite Automatatejshahi1Nessuna valutazione finora

- Chapter 06. Other Automata ModelsDocumento25 pagineChapter 06. Other Automata Modelskims3515354178Nessuna valutazione finora

- 2 22Documento5 pagine2 22Athur Shiraz SiddiquiNessuna valutazione finora

- CS340: Theory of Computation - Nondeterministic Finite AutomatonDocumento7 pagineCS340: Theory of Computation - Nondeterministic Finite AutomatonPreyanshMitharwalNessuna valutazione finora

- Ramkumar PDFDocumento5 pagineRamkumar PDFKiruthika MNessuna valutazione finora

- Decidability and Undecidability: Decidable Problems From Language TheoryDocumento10 pagineDecidability and Undecidability: Decidable Problems From Language TheorySatish KumarNessuna valutazione finora

- Atfl Tutorial Work Book 2022Documento12 pagineAtfl Tutorial Work Book 2022Masti n ChillNessuna valutazione finora

- Maths Turing MachinesDocumento5 pagineMaths Turing MachinesBhasinee ManageNessuna valutazione finora

- Finite Automata and Regular ExpressionsDocumento9 pagineFinite Automata and Regular ExpressionsJegathambal GaneshanNessuna valutazione finora

- Automata - Chap2+finiteautomataDocumento47 pagineAutomata - Chap2+finiteautomatascodrashNessuna valutazione finora

- Stuck at FaultDocumento6 pagineStuck at Faultamy2chang_1Nessuna valutazione finora

- Test Compression PDFDocumento2 pagineTest Compression PDFAman TyagiNessuna valutazione finora

- Automata DFA ExercisesDocumento5 pagineAutomata DFA ExercisesTheMainstreamTechNessuna valutazione finora

- Theory of Automata Assignment – Part 01Documento6 pagineTheory of Automata Assignment – Part 01Aqib RazaNessuna valutazione finora

- Formal Languages CHAPTER-IDocumento11 pagineFormal Languages CHAPTER-IDafuq MaloneNessuna valutazione finora

- Structural Faults in DFTDocumento14 pagineStructural Faults in DFTemail2pr2639Nessuna valutazione finora

- FSMs, NFAs, Regular Expressions, CFGs ExplainedDocumento6 pagineFSMs, NFAs, Regular Expressions, CFGs ExplainedVinit TribhuvanNessuna valutazione finora

- TOC Sns PDFDocumento12 pagineTOC Sns PDFjoNessuna valutazione finora

- Acd Notes - 2Documento32 pagineAcd Notes - 2Anji M ReddyNessuna valutazione finora

- At-Speed Test Methods for LSSD and Mux Flip-Flop DesignsDocumento5 pagineAt-Speed Test Methods for LSSD and Mux Flip-Flop DesignsAman TyagiNessuna valutazione finora

- DFT Scan Insertion: VLSI Testing and Design For TestabilityDocumento19 pagineDFT Scan Insertion: VLSI Testing and Design For TestabilityHuzur AhmedNessuna valutazione finora

- Finite State Automata: Kashiram Pokharel HcoeDocumento61 pagineFinite State Automata: Kashiram Pokharel HcoeSubash DhakalNessuna valutazione finora

- Chapter 5 Algorithmic ComplexityDocumento4 pagineChapter 5 Algorithmic ComplexityKhalifaNessuna valutazione finora

- Vcs /vcsi™ User Guide: Version F-2011.12-Sp1 May 2012Documento1.322 pagineVcs /vcsi™ User Guide: Version F-2011.12-Sp1 May 2012paras_gangwal9757Nessuna valutazione finora

- Question Bank: Short Answer Type QuestionsDocumento29 pagineQuestion Bank: Short Answer Type QuestionsArun UpadhyayNessuna valutazione finora

- STIL - File (Autosaved) (Copy)Documento17 pagineSTIL - File (Autosaved) (Copy)Praveen SakrappanavarNessuna valutazione finora

- Final SolutionsDocumento11 pagineFinal SolutionsFelix MainaNessuna valutazione finora

- At-Speed Transition Fault Testing With Low Speed Scan EnableDocumento6 pagineAt-Speed Transition Fault Testing With Low Speed Scan EnableSiva SreeramdasNessuna valutazione finora

- Sequential Circuit Design Sequence RecognizerDocumento4 pagineSequential Circuit Design Sequence RecognizerKhurram SamiNessuna valutazione finora

- Sequential Circuit DesignDocumento28 pagineSequential Circuit DesignNiranda PereraNessuna valutazione finora

- Sequential & Combinational Timing AnalysisDocumento8 pagineSequential & Combinational Timing AnalysisSahil SharmaNessuna valutazione finora

- Meta StabilityDocumento16 pagineMeta StabilitySahil SharmaNessuna valutazione finora

- Lect5 Behavioral LoopsDocumento12 pagineLect5 Behavioral LoopsSahil SharmaNessuna valutazione finora

- Lect 1 Intro To HDLDocumento10 pagineLect 1 Intro To HDLSahil SharmaNessuna valutazione finora

- Lect-2 Lexical ConventionsDocumento20 pagineLect-2 Lexical ConventionsSahil SharmaNessuna valutazione finora

- Lect 1 VerilogDocumento16 pagineLect 1 VerilogSahil SharmaNessuna valutazione finora

- Dataflow OperatorDocumento14 pagineDataflow OperatorSahil SharmaNessuna valutazione finora

- Compiler DirectivesDocumento11 pagineCompiler DirectivesSahil SharmaNessuna valutazione finora

- Resturant Finance Management System Term PaperDocumento4 pagineResturant Finance Management System Term PaperSahil SharmaNessuna valutazione finora

- Behavioral Delay & BlocksDocumento28 pagineBehavioral Delay & BlocksSahil SharmaNessuna valutazione finora

- Ganpat University Hash Table C ProgramDocumento5 pagineGanpat University Hash Table C ProgramDaksh MaradiyaNessuna valutazione finora

- Debate Redes Sociales InglesDocumento5 pagineDebate Redes Sociales InglesYuritzi Gpe. Ramayo VarguezNessuna valutazione finora

- Super Human Chess EngineDocumento28 pagineSuper Human Chess EngineRich DTNessuna valutazione finora

- Quickspecs: HP Elitedisplay E221 21.5-Inch Led Backlit MonitorDocumento9 pagineQuickspecs: HP Elitedisplay E221 21.5-Inch Led Backlit Monitorpatrick chegeNessuna valutazione finora

- Tcxsky Tech SpecsDocumento2 pagineTcxsky Tech SpecsEdg SanNessuna valutazione finora

- LINUX Basic CommandsDocumento5 pagineLINUX Basic CommandssureshNessuna valutazione finora

- How To Set Up Tx3 MiniDocumento5 pagineHow To Set Up Tx3 MinijuanNessuna valutazione finora

- Open Labs Production Station ManualDocumento126 pagineOpen Labs Production Station ManualEduardo Soares GuiaNessuna valutazione finora

- Chapter 2 Page Development PDFDocumento9 pagineChapter 2 Page Development PDFYiau Kai WooNessuna valutazione finora

- PJ2500M-C / PJ2000M-C: User ManualDocumento40 paginePJ2500M-C / PJ2000M-C: User ManualQuive CarlosNessuna valutazione finora

- 3G - RNO OptimizationDocumento58 pagine3G - RNO OptimizationCristopher TimarioNessuna valutazione finora

- Private Member Functions and Catching Class Types MCQsDocumento5 paginePrivate Member Functions and Catching Class Types MCQsBrendan DominicNessuna valutazione finora

- Delta Loan Tracking Software ReviewDocumento2 pagineDelta Loan Tracking Software ReviewVivek R KoushikNessuna valutazione finora

- The SIMATIC PCS 7 Process Control System - Siemens Automation and Engineering - PDF Catalogs - Technical Documentation - BrochureDocumento10 pagineThe SIMATIC PCS 7 Process Control System - Siemens Automation and Engineering - PDF Catalogs - Technical Documentation - BrochureJemeraldNessuna valutazione finora

- Dav Public School Kusunda, Dhanbad: ACADEMIC YEAR: 2020-21 Project Report On Fee Management SystemDocumento31 pagineDav Public School Kusunda, Dhanbad: ACADEMIC YEAR: 2020-21 Project Report On Fee Management SystemSachin KumarNessuna valutazione finora

- Include The Autocad Mode Feature Level.: Stormcad Stand-Alone InterfaceDocumento20 pagineInclude The Autocad Mode Feature Level.: Stormcad Stand-Alone Interfacejoseluis789Nessuna valutazione finora

- Twinmotion Shortcuts enDocumento1 paginaTwinmotion Shortcuts envizuw agata100% (1)

- Air Ticket ReservationDocumento24 pagineAir Ticket ReservationDevkarn100% (1)

- Lecture 2Documento22 pagineLecture 2Zulqarnain KhanNessuna valutazione finora

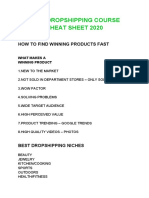

- Free Dropshipping Course Cheat SheetDocumento42 pagineFree Dropshipping Course Cheat Sheetcoffee232100% (1)

- C Programming and Data Structures: Introduction to C LanguageDocumento23 pagineC Programming and Data Structures: Introduction to C Languagekrupa522Nessuna valutazione finora

- JuliadatascienceDocumento214 pagineJuliadatascienceFulvio JoséNessuna valutazione finora

- Test Guide TapnationDocumento12 pagineTest Guide TapnationZied SioudNessuna valutazione finora

- Lesson 4Documento20 pagineLesson 4Dustine Clark CanalitaNessuna valutazione finora

- Divergence of The Sum of The Reciprocals of The PrimesDocumento8 pagineDivergence of The Sum of The Reciprocals of The PrimesstfNessuna valutazione finora

- Signature Analysis and Computer ForensicsDocumento11 pagineSignature Analysis and Computer ForensicsAnindya Nandi100% (1)

- Grocery Shop Management ProjectDocumento21 pagineGrocery Shop Management ProjectSaksham Raj71% (21)

- UD09611B Baseline User Manual of Network PTZ Camera V5.5.7 20180328Documento117 pagineUD09611B Baseline User Manual of Network PTZ Camera V5.5.7 20180328anusprasadNessuna valutazione finora

- Parker Ash Probe User ManualDocumento30 pagineParker Ash Probe User ManualDaniel Alberto Reyes RamirezNessuna valutazione finora

- Cybersecurity Career Practical Starter PackDocumento29 pagineCybersecurity Career Practical Starter PackHarsh ParikhNessuna valutazione finora