Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Sequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos Tatas

Caricato da

vikramkolanu100%(2)Il 100% ha trovato utile questo documento (2 voti)

79 visualizzazioni22 pagineSequential digital circuits are digital circuits whose outputs depend not only on current inputs but also previous state. There are two types of sequential elements: latches which are level-sensitive and flip-flops which are edge-triggered. Latches include SR, JK, D latches. Flip-flops include JK, D and T flip-flops. Edge-triggered versions are obtained by adding an edge detector to the enable input of latches. Examples of sequential circuits using D flip-flops, multiplexers and other elements are also presented.

Descrizione originale:

design

Titolo originale

FlipFlops

Copyright

© © All Rights Reserved

Formati disponibili

PPT, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoSequential digital circuits are digital circuits whose outputs depend not only on current inputs but also previous state. There are two types of sequential elements: latches which are level-sensitive and flip-flops which are edge-triggered. Latches include SR, JK, D latches. Flip-flops include JK, D and T flip-flops. Edge-triggered versions are obtained by adding an edge detector to the enable input of latches. Examples of sequential circuits using D flip-flops, multiplexers and other elements are also presented.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PPT, PDF, TXT o leggi online su Scribd

100%(2)Il 100% ha trovato utile questo documento (2 voti)

79 visualizzazioni22 pagineSequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos Tatas

Caricato da

vikramkolanuSequential digital circuits are digital circuits whose outputs depend not only on current inputs but also previous state. There are two types of sequential elements: latches which are level-sensitive and flip-flops which are edge-triggered. Latches include SR, JK, D latches. Flip-flops include JK, D and T flip-flops. Edge-triggered versions are obtained by adding an edge detector to the enable input of latches. Examples of sequential circuits using D flip-flops, multiplexers and other elements are also presented.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PPT, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 22

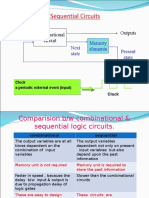

Sequential Digital Circuits

Dr. Costas Kyriacou and Dr. Konstantinos Tatas

ACOE161 - Digital Logic for Computers

- Frederick University

2

Sequential Digital Circuits

Sequential circuits are digital circuits in which the outputs

depend not only on the current inputs, but also on the previous

state of the output.

They basic sequential circuit elements can be divided in two

categories:

Level-sensitive (Latches)

High-level sensitive

Low-level sensitive

Edge-triggered (Flip-flops)

Rising (positive) edge triggered

Falling (negative) edge triggered

Dual-edge triggered

ACOE161 - Digital Logic for Computers

- Frederick University

3

The Set/Reset (SR) Latch

The Set/Reset latch is the most basic unit of sequential digital circuits. It has two

inputs (S and R) and two outputs outputs Q and Q. The two outputs must always be

complementary, i.e if Q is 0 then Q must be 1, and vice-versa. The S input sets the

Q output to a logic 1. The R input resets the Q output to a logic 0.

S

R

Q

Q

R

S

Q

Q

S R Q+

0 0

0 1

1 0

1 1

Function

S Q

R Q

Logic Symbol

Truth Table Circuit Diagram

Q

0

1

0

Q+

Q Latch

Reset

Set

1

0

0

Illegal

ACOE161 - Digital Logic for Computers

- Frederick University

4

The Gated Set/Reset (SR) Latch

To be able to control when the S and R inputs of the SR latch can be applied to the

latch and thus change the outputs, an extra input is used. This input is called the

Enable. If the Enable is 0 then the S and R inputs have no effect on the outputs of the

SR latch. If the Enable is 1 then the Gated SR latch behaves as a normal SR latch.

Logic Symbol

Truth Table

S

R

Q

Circuit Diagram

S Q

R Q Q

EN

S R EN Q+

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Truth Table

S Q

R Q

EN

S R EN Q+

0 X X

1 0 0

1 0 1

1 1 0

1 1 1

Function

Q

Q

Q

Q

Q

0

1

U

ACOE161 - Digital Logic for Computers

- Frederick University

5

SR Latch :- Example

Complete the timing diagrams for :

(a) Simple SR Latch

(b) SR Latch with Enable input.

Assume that for both cases the Q output is initially at logic zero.

Set

Reset

Q

Set

Reset

Q

Enable

(b) (a)

ACOE161 - Digital Logic for Computers

- Frederick University

6

The Data (D) Latch

A problem with the SR latch is that the S and R inputs can not be at logic 1 at the

same time. To ensure that this can not happen, the S and R inputs can by connected

through an inverter. In this case the Q output is always the same as the input, and the

latch is called the Data or D latch. The D latch is used in Registers and memory

devices.

Logic Symbol

Truth Table

D Q EN Q+

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Truth Table

D EN Q+

0 0

1 0

1 0

1 1

Function

D

Q

Circuit Diagram

Q

EN

S Q

R Q

D Q

Q

EN

Q

Q

Q

Q

0

0

1

1

ACOE161 - Digital Logic for Computers

- Frederick University

7

The JK Latch

Another way to ensure that the S and R inputs can not be at logic 1 simultaneously, is

to cross connect the Q and Q outputs with the S and R inputs through AND gates.

The latch obtained is called the JK latch. In the J and K inputs are both 1 then the Q

output will change state (Toggle) for as long as the Enable 1, thus the output will be

unstable. This problem is avoided by ensuring that the Enable is at logic 1 only for a

very short time, using edge detection circuits.

Logic Symbol

Truth Table

J K EN Q+

0 X X

1 0 0

1 0 0

1 0 1

1 0 1

1 1 0

1 1 0

1 1 1

1

X

0

1

0

1

0

1

0

1 1 1

Q

Truth Table

J EN Q+

0 X

0 1

1 0

1 1

Function

1 1

K

X

0

1

0

1

J Q

Circuit Diagram

Q

EN

S Q

R Q

J Q

Q

EN

K

K

Q

0

1

0

0

1

1

1

0

ACOE161 - Digital Logic for Computers

- Frederick University

8

Latches and Flip-Flops

Latches are also called transparent or level triggered flip flops,

because the change on the outputs will follow the changes of the

inputs as long as the Enable input is set.

Edge triggered flip flops are the flip flops that change there outputs

only at the transition of the Enable input. The enable is called the

Clock input.

ACOE161 - Digital Logic for Computers

- Frederick University

9

Edge Detection Circuits

Edge detection circuits are used to detect the transition of the Enable from logic 0 to

logic 1 (positive edge) or from logic 1 to logic 0 (negative edge). The operation of the

edge detection circuits shown below is based on the fact that there is a time delay

between the change of the input of a gate and the change at the output. This delay is

in the order of a few nanoseconds. The Enable in this case is called the Clock (CLK)

EN

EN'

EN

EN

EN'

EN

EN

EN'

EN

EN

EN'

EN

EN

Positive Edge Detection Negative Edge Detection

EN

ACOE161 - Digital Logic for Computers

- Frederick University

10

The JK Edge Triggered Flip Flop

The JK edge triggered flip flop can be obtained by inserting an edge detection circuit

at the Enable (CLK) input of a JK latch. This ensures that the outputs of the flip flop

will change only when the CLK changes (0 to 1 for +ve edge or 1 to 0 for ve edge)

Logic Symbol

Positive Edge JK Flip Flop

J CLK QN+1

X

0

0

1

Function

1

K

X

0

1

0

1

J

Q

Q

CLK

S Q

R Q

J Q

Q K

K

CLK

Logic Symbol

Negative Edge JK Flip Flop

J CLK QN+1

X

0

0

1

Function

1

K

X

0

1

0

1

J

Q

Q

CLK

S Q

R Q

J Q

Q K

K

CLK

Q

0

1

Q

Q

ACOE161 - Digital Logic for Computers

- Frederick University

11

The D Edge Triggered Flip Flop

The D edge triggered flip flop can be obtained by connecting the J with the K inputs

of a JK flip through an inverter as shown below. The D edge trigger can also be

obtained by connecting the S with the R inputs of a SR edge triggered flip flop

through an inverter.

Logic Symbol

Positive Edge D Flip Flop

CLK QN+1 Function D

X

0

1

D Q

Q

CLK

CLK

D Q

Q

J Q

Q K

Logic Symbol

Negative Edge D Flip Flop

CLK QN+1 Function D

X

0

1

D Q

Q

CLK

CLK

D Q

Q

J Q

Q K

0

1

Q

0

1

Q

ACOE161 - Digital Logic for Computers

- Frederick University

12

The Toggle (T) Edge Triggered Flip Flop

The T edge triggered flip flop can be obtained by connecting the J with the K inputs

of a JK flip directly. When T is zero then both J and K are zero and the Q output does

not change. When T is one then both J and K are one and the Q output will change to

the opposite state, or toggle.

Logic Symbol

Positive Edge T Flip Flop

T Q

Q

CLK

CLK

T Q

Q

J Q

Q K

Logic Symbol

Negative Edge T Flip Flop

T Q

Q

CLK

CLK

T Q

Q

J Q

Q K

CLK QN+1 Function T

X

0

1

CLK QN+1 Function T

X

0

1

Q

Q

Q

Q

Q

Q

ACOE161 - Digital Logic for Computers

- Frederick University

13

Flip Flops with asynchronous inputs (Preset and Clear)

Two extra inputs are often found on flip flops, that either clear or preset the output.

These inputs are effective at any time, thus are called asynchronous. If the Clear is at

logic 0 then the output is forced to 0, irrespective of the other normal inputs. If the

Preset is at logic 0 then the output is forced to 1, irrespective of the other normal

inputs. The preset and the clear inputs can not be 0 simultaneously. In the Preset and

Clear are both 1 then the flip flop behaves according to its normal truth table.

Positive Edge JK Flip Flop with Preset and Clear

PRESET

J Q

Q K

CLR

PR

CLEAR

CLK QN+1 Function K

X

X

X

0

1

1

J

X

X

0

0

1

X

CLR

1

0

1

1

1

0

PR

0

1

1

1

1

0

1 0

1 1

1

Q

0

1

Q

0

ACOE161 - Digital Logic for Computers

- Frederick University

14

Data (D) Latch :- Example

Complete the timing diagrams for :

(a) D Latch

(b) JK Latch

Assume that for both cases the Q output is initially at logic zero.

Enable

Data (D)

Q

J

K

Q

Enable

(b) (a)

ACOE161 - Digital Logic for Computers

- Frederick University

15

JK Edge Triggered Flip Flop :- Example

Complete the timing diagrams for :

(a) Positive Edge Triggered JK Flip Flop

(b) Negative Edge Triggered JK Flip Flop

Assume that for both cases the Q output is initially at logic zero.

J

K

Q

CLK

(b) (a)

J

K

Q

CLK

ACOE161 - Digital Logic for Computers

- Frederick University

16

D and T Edge Triggered Flip Flops :- Example

Complete the timing diagrams for :

(a) Positive Edge Triggered D Flip Flop

(b) Positive Edge Triggered T Flip Flop

(c) Negative Edge Triggered T Flip Flop

(d) Negative Edge Triggered D Flip Flop

(b) (a)

D

Q

CLK

D

Q

CLK

(d) (c)

T

Q

CLK

T

Q

CLK

ACOE161 - Digital Logic for Computers

- Frederick University

17

JK Flip Flop With Preset and Clear:- Example

Complete the timing diagrams for :

(a) Positive Edge Triggered JK Flip Flop

(b) Negative Edge Triggered JK Flip Flop.

Assume that for both cases the Q output is initially at logic zero.

(b) (a)

J

K

Q

CLK

CLR

PR

J

K

Q

CLK

CLR

PR

ACOE161 - Digital Logic for Computers

- Frederick University

18

Level Triggered Master Slave JK Flip Flop

A Master Slave flip flop is obtained by connecting two SR latches as shown below. This flip

flop reads the inputs when the clock is 1 and changes the output when the clock is at logic

zero.

Logic Symbol

J

K

Master

S Q

R Q

CLK

Truth Table

J K CLK Q

0 0

0 1

1 0

1 1

Function

Q

Q

S Q

R Q

Slave

J

K

CLK

Q

Q

J

K

Q

CLK

(a) Positive Master Slave JK Flip Flop

J

K

Q

CLK

(b) Negative Master Slave JK Flip Flop

ACOE161 - Digital Logic for Computers

- Frederick University

19

Edge Triggered Master Slave JK Flip Flop

A Master Slave flip flop is obtained by connecting two SR latches as shown below. This flip

flop reads the inputs when the clock is 1 and changes the output when the clock is at logic

zero.

J

K

Q

CLK

(a) Positive Master Slave JK Flip Flop

J

K

Q

CLK

(b) Negative Master Slave JK Flip Flop

Logic Symbol

J

K

Master

S Q

R Q

CLK

Truth Table

J K CLK Q

0 0

0 1

1 0

1 1

Function

Q

Q

S Q

R Q

Slave

J

K

Q

Q

ACOE161 - Digital Logic for Computers

- Frederick University

20

Sequential circuit example 1

Q

Q

SET

CLR

D

2-to-1

MUX

A0

A1

S

Clock

1 2 3 4 5 6 7 8 9 10

Clock

A0

A1

S

D

Q

ACOE161 - Digital Logic for Computers

- Frederick University

21

Sequential circuit example 2

Q

Q

SET

CLR

D

Clock

1 2 3 4 5 6 7 8 9 10

Clock

Q

Q

D

ACOE161 - Digital Logic for Computers

- Frederick University

22

Sequential circuit example 3

Q

Q

SET

CLR

D

CP

FULL ADDER

X

Y

Z

C

S

/T

CP

X

Y

Z

S

C

Potrebbero piacerti anche

- Introduction to Digital Communication SystemsDa EverandIntroduction to Digital Communication SystemsNessuna valutazione finora

- Fpga Programming Using Verilog HDL LanguageDocumento89 pagineFpga Programming Using Verilog HDL LanguageSidhartha Sankar Rout0% (1)

- Fpga Based System DesignDocumento30 pagineFpga Based System DesignKrishna Kumar100% (1)

- Logisim LabsDocumento157 pagineLogisim LabsJosealberto HernandezNessuna valutazione finora

- Lec20 RTL DesignDocumento40 pagineLec20 RTL DesignVrushali patilNessuna valutazione finora

- FPGA Selection: LTC2387-18 S.No Pin - Name Pin - No. - ADC Mode PurposeDocumento6 pagineFPGA Selection: LTC2387-18 S.No Pin - Name Pin - No. - ADC Mode PurposeGurinder Pal SinghNessuna valutazione finora

- Modern Digital Electronics - R. P. JainDocumento92 pagineModern Digital Electronics - R. P. JainJames Thee33% (3)

- Design CompilerDocumento48 pagineDesign CompilerSumanth BabuNessuna valutazione finora

- Digital System Design Based On Data Path and Control UnitDocumento52 pagineDigital System Design Based On Data Path and Control UnitHemant Tulsani33% (3)

- Design of Analog FIltersDocumento7 pagineDesign of Analog FIltersparshuram kumarNessuna valutazione finora

- Architecture of FPGAs and CPLDS: A TutorialDocumento41 pagineArchitecture of FPGAs and CPLDS: A Tutorialgongster100% (5)

- Retiming and Re-SynthesisDocumento39 pagineRetiming and Re-SynthesisVeeresh TangadgiNessuna valutazione finora

- Verilog Imp...Documento105 pagineVerilog Imp...Arun JyothiNessuna valutazione finora

- Experiment Sheet - FPGA Design ALLDocumento38 pagineExperiment Sheet - FPGA Design ALLSidney O. EbotNessuna valutazione finora

- Haps-54 March2009 ManualDocumento74 pagineHaps-54 March2009 Manualjohn92691Nessuna valutazione finora

- Line Follower Robot PresentationDocumento25 pagineLine Follower Robot Presentationmirrayhan0867% (6)

- 6bk1200 0aa20 0aa0 Sicomp Imc 01s Siemens Panel ManualDocumento130 pagine6bk1200 0aa20 0aa0 Sicomp Imc 01s Siemens Panel Manualkarim100% (2)

- RTL DesignDocumento31 pagineRTL DesignBala SubramanianNessuna valutazione finora

- CharFlo-Memory Compiler Tech Rev10.3-2010JuneDocumento33 pagineCharFlo-Memory Compiler Tech Rev10.3-2010Junevikramkolanu100% (1)

- Design and Implementation of 2 Bits BCH Error Correcting Codes Using FPGADocumento7 pagineDesign and Implementation of 2 Bits BCH Error Correcting Codes Using FPGAJournal of TelecommunicationsNessuna valutazione finora

- Lecture 5Documento47 pagineLecture 5Ershad ShaikNessuna valutazione finora

- DSP Processor FundamentalsDocumento58 pagineDSP Processor FundamentalsSayee KrishnaNessuna valutazione finora

- Zynq 7020Documento4 pagineZynq 7020NGUYỄN HOÀNG LINHNessuna valutazione finora

- VHDL PDFDocumento112 pagineVHDL PDFvivek patelNessuna valutazione finora

- VHDL Bram BromDocumento9 pagineVHDL Bram BromGmit MandyaNessuna valutazione finora

- Digital Signal Processors Architectures Implementations and ApplicationsDocumento17 pagineDigital Signal Processors Architectures Implementations and ApplicationsAbirami Kannan0% (3)

- 2D NMR SpectrosDocumento12 pagine2D NMR Spectrossatheeshpharma6Nessuna valutazione finora

- Introduction To VHDLDocumento88 pagineIntroduction To VHDLpusd_90Nessuna valutazione finora

- ADPLL Design and Implementation On FPGADocumento6 pagineADPLL Design and Implementation On FPGANavathej BangariNessuna valutazione finora

- Lecture17 RoutingDocumento51 pagineLecture17 Routingapi-3834272Nessuna valutazione finora

- Introduction To TMS320C6713 DSP Starter Kit DSK)Documento18 pagineIntroduction To TMS320C6713 DSP Starter Kit DSK)Anup DharanguttiNessuna valutazione finora

- Filter DesignDocumento9 pagineFilter DesignTaylor MaddixNessuna valutazione finora

- Lecture5 PartitionspectralDocumento14 pagineLecture5 Partitionspectralapi-3834272Nessuna valutazione finora

- Eric Thesis SlidesDocumento43 pagineEric Thesis SlidesHumberto JuniorNessuna valutazione finora

- Gaussian Random Number Generator Using Boxmuller MethodDocumento27 pagineGaussian Random Number Generator Using Boxmuller MethodAbhijeet Singh KatiyarNessuna valutazione finora

- Systemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammDocumento26 pagineSystemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammAamir HabibNessuna valutazione finora

- Decision Feedback EqualiserDocumento9 pagineDecision Feedback EqualiserHari PrasathNessuna valutazione finora

- Lecture1 IntroDocumento35 pagineLecture1 Introapi-3834272Nessuna valutazione finora

- Clock Domain ClockingDocumento12 pagineClock Domain Clockingarunsrl100% (1)

- Lecture21 dr1Documento31 pagineLecture21 dr1api-3834272Nessuna valutazione finora

- Digital Integrated Circuits: A Design PerspectiveDocumento113 pagineDigital Integrated Circuits: A Design Perspectiveapi-127299018Nessuna valutazione finora

- Tiger SHARC ProcessorDocumento36 pagineTiger SHARC ProcessorChintan PatelNessuna valutazione finora

- Orcad PSpice DesignerDocumento47 pagineOrcad PSpice DesignerAishwarya JS100% (1)

- Product OverviewDocumento9 pagineProduct OverviewUsha KrishnaNessuna valutazione finora

- Ch04 - Multimedia Element-ImagesDocumento63 pagineCh04 - Multimedia Element-Imagessu6aNessuna valutazione finora

- VerilogDocumento18 pagineVerilogvortex2910_899547857Nessuna valutazione finora

- Lecture8 Floorplan2Documento34 pagineLecture8 Floorplan2api-3834272Nessuna valutazione finora

- Xlinx - VLSI Practical Lab ManualDocumento31 pagineXlinx - VLSI Practical Lab ManualSamarth J Parikh0% (1)

- D.S.P/MATLAB Theory & ExperimentsDocumento57 pagineD.S.P/MATLAB Theory & ExperimentsNandagopal Sivakumar50% (4)

- Keshab K Parhi VLSI Digital Signal ProcessingDocumento113 pagineKeshab K Parhi VLSI Digital Signal ProcessingPranjal Rastogi0% (1)

- Field Programmable Gate Array (FPGA)Documento11 pagineField Programmable Gate Array (FPGA)anupnaskar naskar100% (1)

- Digital Integrated Circuits: A Design PerspectiveDocumento84 pagineDigital Integrated Circuits: A Design PerspectivedurraizaliNessuna valutazione finora

- Bus StructureDocumento160 pagineBus StructureRohit SaxenaNessuna valutazione finora

- Pipelining and Parallel ProcessingDocumento16 paginePipelining and Parallel ProcessingBilgaNessuna valutazione finora

- Flip FlopsDocumento60 pagineFlip FlopsA10-14Rajat KumarNessuna valutazione finora

- UntitledDocumento8 pagineUntitledlalita chauhanNessuna valutazione finora

- L4: Sequential Building Blocks (Flip - Flops, Latches and Registers)Documento24 pagineL4: Sequential Building Blocks (Flip - Flops, Latches and Registers)ggk87Nessuna valutazione finora

- Experiment 9 (Flip Flops)Documento7 pagineExperiment 9 (Flip Flops)groupidb3100% (3)

- Flip Flop Mealy and Moore ModelDocumento25 pagineFlip Flop Mealy and Moore Modelsurajpb1989100% (1)

- D and JK FFDocumento22 pagineD and JK FFRawan AyyoubNessuna valutazione finora

- Synchronous Sequential Ckts by Lakshmi NarayanaDocumento30 pagineSynchronous Sequential Ckts by Lakshmi NarayanaMurali Krishna100% (1)

- Sequential Circuits: Presented By: Group 3Documento30 pagineSequential Circuits: Presented By: Group 3Jalaj SrivastavaNessuna valutazione finora

- RTL Vs Technology SchematicDocumento1 paginaRTL Vs Technology SchematicvikramkolanuNessuna valutazione finora

- GATE 2016 How To Prepare For Electronics and Communication Engineering (ECE)Documento14 pagineGATE 2016 How To Prepare For Electronics and Communication Engineering (ECE)vikramkolanuNessuna valutazione finora

- FlipflopsDocumento80 pagineFlipflopsvikramkolanuNessuna valutazione finora

- April 2004Documento15 pagineApril 2004vikramkolanuNessuna valutazione finora

- State: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedDocumento8 pagineState: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedvikramkolanuNessuna valutazione finora

- 21 FSM ExamplesDocumento4 pagine21 FSM ExamplesvikramkolanuNessuna valutazione finora

- Career Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailDocumento2 pagineCareer Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailvikramkolanuNessuna valutazione finora

- What Is Video RAMDocumento2 pagineWhat Is Video RAMrks12345Nessuna valutazione finora

- Ds dx2300Documento2 pagineDs dx2300Edwin ArdiansyahNessuna valutazione finora

- Setup and Hold Time": Static Timing Analysis (STA) Basic (Part 3c) - VLSI ConceptsDocumento14 pagineSetup and Hold Time": Static Timing Analysis (STA) Basic (Part 3c) - VLSI ConceptsKeerthiKalyanNessuna valutazione finora

- Final Report On Remote Sensing and ControlDocumento79 pagineFinal Report On Remote Sensing and ControlBasu Dev AryalNessuna valutazione finora

- I/O Interfacing of 8086 Using 8255Documento19 pagineI/O Interfacing of 8086 Using 8255SAURABH AGRAWALNessuna valutazione finora

- CountersDocumento19 pagineCounterslakraniNessuna valutazione finora

- Implementation of 1-Bit Full Adder Circuit Using Pass Transistor LogicDocumento11 pagineImplementation of 1-Bit Full Adder Circuit Using Pass Transistor LogicIJRASETPublicationsNessuna valutazione finora

- Questions: B. Write Notes On: FpgaDocumento2 pagineQuestions: B. Write Notes On: FpgaunnidigiNessuna valutazione finora

- OptiPlex XE3 Spec SheetDocumento4 pagineOptiPlex XE3 Spec SheetIrving ChamosaNessuna valutazione finora

- Mondal 2017Documento6 pagineMondal 2017Debesh DasNessuna valutazione finora

- Coresight Etm - M4: Technical Reference ManualDocumento55 pagineCoresight Etm - M4: Technical Reference ManualWalid AmriNessuna valutazione finora

- BLED112 DatasheetDocumento12 pagineBLED112 DatasheetAndualem TadesseNessuna valutazione finora

- Sequential Circuits and Seven Segment Display: Lab Assignment 10Documento7 pagineSequential Circuits and Seven Segment Display: Lab Assignment 10Ahmed UzairNessuna valutazione finora

- VLSI Physical Design - Physical Design (Floorplanning) Interview Question Part 4Documento3 pagineVLSI Physical Design - Physical Design (Floorplanning) Interview Question Part 4srinathNessuna valutazione finora

- Mxma S A0009736063 1 PDFDocumento123 pagineMxma S A0009736063 1 PDFRoger Chavez PachasNessuna valutazione finora

- Secondary Storage Devices (1) :: Magnetic DisksDocumento56 pagineSecondary Storage Devices (1) :: Magnetic DisksSamahir AlkleefaNessuna valutazione finora

- Core8051s EmbProc HW Tutorial UGDocumento60 pagineCore8051s EmbProc HW Tutorial UGprabhu.swain3500Nessuna valutazione finora

- Computer Organization and Architecture 10th Edition Stallings Test BankDocumento9 pagineComputer Organization and Architecture 10th Edition Stallings Test BankCarrieSchmidtabsde100% (11)

- Datasheet IR - 4427SDocumento12 pagineDatasheet IR - 4427SmazinswNessuna valutazione finora

- Altera Design Flow For Xilinx UsersDocumento78 pagineAltera Design Flow For Xilinx UsersakachyanNessuna valutazione finora

- Tutorial IITBDocumento9 pagineTutorial IITBpiyush_rawat_5Nessuna valutazione finora

- ARM ProcessorsDocumento16 pagineARM ProcessorsyayavaramNessuna valutazione finora

- Shuttle - High-Res Images - XPC - SN41G2 - SN41G2V3 (VerDocumento2 pagineShuttle - High-Res Images - XPC - SN41G2 - SN41G2V3 (Vercharly069Nessuna valutazione finora

- MPMC Unit 1Documento75 pagineMPMC Unit 1Bhure VedikaNessuna valutazione finora

- Manualnew 536785461 PDFDocumento72 pagineManualnew 536785461 PDFdiogratiaNessuna valutazione finora