Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Microprocesadores 1 Sesion

Caricato da

Percy Siancas BlasTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Microprocesadores 1 Sesion

Caricato da

Percy Siancas BlasCopyright:

Formati disponibili

Clase 1: Introduccin, Arquitectura, Aplicaciones,

Bienvenidos

Semestre 2008-II

Introduccin

Sistemas Basados en Microprocesadores

Celulares.

Reproductores MP3/MP4.

XBOX, PS1/2/3.

Computadores.

Cuentan con una CPU.

BUSCANDO FALLOS EN EL ESQUEMA DE

UN

MICROPROCESADOR

El Microprocesador es

un componente de alta escala

de integracin (LSI) !

4004 8008 8080 8086/8088 286 386

486

PENTIUM

PENTIUM PRO PENTIUM II PENTIUM III

PENTIUM IV

EVOLUCIN

DE LOS P

INTEL

XEN

ITALIUM

IDEAS BSICAS P

1.- Es un sistema secuencia sincrono.

2.- Existe siempre un RELOJ (CLK). Normalmente la circuitera es interna y con un cuarzo externo se define la

frecuencia de funcionamiento.

3.- Existe un PROGRAMA que gobierna el funcionamiento del sistema. Est constituido por un conjunto de

instrucciones que se ejecutan de forma secuencial y que estn almacenadas en memoria (ROM) de forma

codificada.

4.- La MEMORIA es el lugar de almacenamiento de datos y resultados parciales. Datos fijos y Programa (ROM) y

datos variables (RAM).

5.- La CPU tiene las siguientes funciones:

Recoge las instrucciones de programa que estan en memoria

Las decodifica y ejecuta

Reconoce situaciones especiales (RESET, Interrupciones, etc)

6.- Dentro de la CPU tenemos varios elementos bsicos que debemos conocer:

Los REGISTROS de uso comn y los de estado (Acumuladores, PC, SP, IX, F)

La unidad aritmtico lgica (ALU). Define las operaciones aritmtico/lgicas que podemos realizar

Asociado con ellas el JUEGO DE INSTRUCCIONES que es capaz de realizar.

7.- La unidad de E/S proporciona la interconexin con el mundo exterior:

Monitor, teclados, ratn, D/A, A/D, memora externa, discos, perifricos en general.

8.- Todos los bloques estn interconectados por los BUSES:

BUS DE DATOS

BUS DE DIRECCIONES

BUS DE CONTROL

Arquitectura Harvard

En la arquitectura Harvard, existen dos tipos de memorias, y

por lo tanto dos buses, que suelen ser de anchura diferente, es

posible acceder a ambas memorias al mismo tiempo, con lo cual la

velocidad del sistema aumenta

(P RISC Reduced Instruction Set Computer)

Arquitectura de Computadoras

Arquitectura Von Neumann Arquitectura Harvard

APLICACINES Computadora de 8 Bits (Microcontrolador PIC )

1 En un display mostrar la entrada binaria del Puerto A en BCD en el

Display. As por ejemplo si por la entrada lee "101" en el display

visualiza 5"

ZONA DE DATOS*********************************************

LIST P=16F84A

INCLUDE <P16F84A.INC>

; ZONA DE CDIGOS ************************************

ORG 0 ; El programa inicia en la direccin 0.

Inicio

bsf STATUS,RP0 ; Acceso al Banco 1.

clrf PORTB ; Las lneas del Puerto B se configuran como salida.

movlw b'00011111' ; Las 5 lneas del Puerto A se configuran como entrada.

movwf PORTA

bcf STATUS,RP0 ; Acceso al Banco 0.

Principal

movf PORTA,W ; Lee la entrada

andlw b'00000111' ; Mscara para quedarse con el valor de las 3 entradas

call Binario_a_7Segmentos ; Convierte cdigo binario a 7 segmentos del display.

movwf PORTB ; Resultado se visualiza por el puerto de salida.

goto Principal

; Subrutina "Binario_7Segmentos" -----------------------------------------------

Binario_a_7Segmentos ; Tabla para display de 7 segmentos.

addwf PCL,F

Tabla retlw 3Fh ; El cdigo 7 segmentos para el "0".

retlw 06h ; El cdigo 7 segmentos para el "1".

retlw 5Bh ; El cdigo 7 segmentos para el "2".

retlw 4Fh ; El cdigo 7 segmentos para el "3".

retlw 66h ; El cdigo 7 segmentos para el "4".

retlw 6Dh ; El cdigo 7 segmentos para el "5".

retlw 7Dh ; El cdigo 7 segmentos para el "6".

retlw 07h ; El cdigo 7 segmentos para el "7".

retlw 7Fh ; El cdigo 7 segmentos para el "8".

END ; Fin del programa.

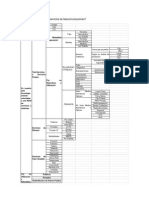

CPU

MEMORIA

ROM

(Programa)

MEMORIA

RAM

(Datos)

Entrada /

Salida

ALIMENTACIN

RELOJ

DIRECCIONES

DATOS

CONTROL

EXTERIOR

8

16

32

64

16 = 64K

20 = 1M

24 = 16M

32 = 4G

ARQUITECTURA VON-NEUMANN

(P CISC Complex Instruction Set Computer)

BUSES

CLK

Interrupciones

RESET

DMA

R / W

MAPA DE

MEMORIA

MAPA E/S

Esta arquitectura se caracteriza por disponer de

una Sola memoria principal donde se almacenan datos e instrucciones

en segmentos separados . A dicha memoria se accede a travs de un

sistema de buses nico (direcciones, datos y control).

Estructura Funcional de los Ordenador

Unidad Central de Proceso

EJECUCION DE LAS INSTRUCCIONES

Bsqueda de

la Instruccin

Decodificacin de

la Instruccin

Bsqueda de

Operandos

Ejecucin de

la Instruccin

Almacenamiento

del Resultado

Prxima

Instruccin

Se extrae de la memoria la siguiente

instruccin y se la lleva al registro de

Insruccin (RI).

Se determina el tipo de instruccin y los

operandos que tiene.

Se busca el/los operandos y se los carga en

los registros internos de la CPU.

Se ejecuta la operacin.

Se almacena el resultado en el lugar apropiado.

Se pasa a la siguiente instruccin.

Potrebbero piacerti anche

- Tarea Grupal PythonDocumento8 pagineTarea Grupal PythonPercy Siancas BlasNessuna valutazione finora

- Brotes de Habas para ParkinsonDocumento3 pagineBrotes de Habas para ParkinsonPercy Siancas BlasNessuna valutazione finora

- Resumen Hacia Una Educación A DistanciaDocumento2 pagineResumen Hacia Una Educación A DistanciaPercy Siancas BlasNessuna valutazione finora

- preguntaRevisionAnalisis SiancasDocumento3 paginepreguntaRevisionAnalisis SiancasPercy Siancas BlasNessuna valutazione finora

- Riqueza y Orgullo Del PeruDocumento43 pagineRiqueza y Orgullo Del PerurobertNessuna valutazione finora

- CONIDA Presentacion Cip SantistebanDocumento38 pagineCONIDA Presentacion Cip SantistebanWerenshon Ramos GonzalesNessuna valutazione finora

- Cohetes y Satelites ArtificialesDocumento53 pagineCohetes y Satelites ArtificialesixcanetNessuna valutazione finora

- Actividad 7 Percy Orlando Siancas BlasDocumento4 pagineActividad 7 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 6 Percy Orlando Siancas BlasDocumento1 paginaActividad 6 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 6 Percy Orlando Siancas BlasDocumento1 paginaActividad 6 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 6 Percy Orlando Siancas BlasDocumento1 paginaActividad 6 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 5 Percy Orlando Siancas BlasDocumento3 pagineActividad 5 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 5 Percy Orlando Siancas BlasDocumento3 pagineActividad 5 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 7 Percy Orlando Siancas BlasDocumento4 pagineActividad 7 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 7 Percy Orlando Siancas BlasDocumento4 pagineActividad 7 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 3 Percy O Siancas BlasDocumento1 paginaActividad 3 Percy O Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Capitulo 03 - Conmutacion y Planta ExternaDocumento60 pagineCapitulo 03 - Conmutacion y Planta ExternaChechi69Nessuna valutazione finora

- Actividad 4 Percy Orlando Siancas BlasDocumento2 pagineActividad 4 Percy Orlando Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Displays y MatrizDocumento11 pagineDisplays y MatrizDayana Ramirez GilNessuna valutazione finora

- Actividad 7 Percy O Siancas BlasDocumento3 pagineActividad 7 Percy O Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 1 P. Siancas BlasDocumento3 pagineActividad 1 P. Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 2 P. Siancas BlasDocumento4 pagineActividad 2 P. Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Guia WebexDocumento11 pagineGuia WebexJohnny Albert RodriguezNessuna valutazione finora

- Actividad 2 P. Siancas BlasDocumento4 pagineActividad 2 P. Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Actividad 1 P. Siancas BlasDocumento3 pagineActividad 1 P. Siancas BlasPercy Siancas BlasNessuna valutazione finora

- Ejercicios para La Artrosis de RodillaDocumento12 pagineEjercicios para La Artrosis de RodillaJenny InesNessuna valutazione finora

- Certificado Original de Estudios o Constancia de Inscripción de Su Grado en La ANRDocumento1 paginaCertificado Original de Estudios o Constancia de Inscripción de Su Grado en La ANRPercy Siancas BlasNessuna valutazione finora

- T 7.2.2.1 Modulación PCMDocumento137 pagineT 7.2.2.1 Modulación PCMPercy Siancas BlasNessuna valutazione finora

- Evolución hardware software computaciónDocumento8 pagineEvolución hardware software computaciónImanol cabanillasNessuna valutazione finora

- Dell-1815dn User's Guide Es-MxDocumento148 pagineDell-1815dn User's Guide Es-MxJose Valero IlustNessuna valutazione finora

- Realiza La Solicitud de Reabastecimiento de Insumos yDocumento10 pagineRealiza La Solicitud de Reabastecimiento de Insumos yEduardo AntonioNessuna valutazione finora

- Linux ThreadsDocumento2 pagineLinux ThreadsIskandarinaNessuna valutazione finora

- Necesidades 2023 AtmDocumento4 pagineNecesidades 2023 Atmirwin lazoNessuna valutazione finora

- Triptico. #G4Documento2 pagineTriptico. #G4tendencia dfdfNessuna valutazione finora

- Clasificación de los microcontroladores de 8 bits: gama base, media y mejoradaDocumento6 pagineClasificación de los microcontroladores de 8 bits: gama base, media y mejoradaLuis Fernando Carrera AcostaNessuna valutazione finora

- Guia 1 - 25-07-2023 - 042039Documento7 pagineGuia 1 - 25-07-2023 - 042039Carlos Jose Reyes CoelloNessuna valutazione finora

- Herramienta de Diagnóstico Electrónico - MHDDocumento36 pagineHerramienta de Diagnóstico Electrónico - MHDAngel Dlsg100% (1)

- Manual Tecnico Ricoh 5200 - Buscar Con GoogleDocumento2 pagineManual Tecnico Ricoh 5200 - Buscar Con GoogleRicardo Lester0% (1)

- Informatica 1990Documento11 pagineInformatica 1990franco432francol2321Nessuna valutazione finora

- Estado Del Arte de Las ComputadorasDocumento7 pagineEstado Del Arte de Las ComputadorasAlberto CarcaterraNessuna valutazione finora

- Comandar Un Pic Por InternetDocumento3 pagineComandar Un Pic Por InternetdanielNessuna valutazione finora

- Uso I2C Pantalla LCD16x2Documento11 pagineUso I2C Pantalla LCD16x2Rommel LoayzaNessuna valutazione finora

- Valores Matricula Pensiones Costa 2014-2015 Esmeraldas1Documento6 pagineValores Matricula Pensiones Costa 2014-2015 Esmeraldas1Nelson Simarron GastelotNessuna valutazione finora

- Opción 2Documento4 pagineOpción 2Rodolfo de Jesus Alvarez MonteroNessuna valutazione finora

- Capitulo 1 Del Curso de Microcontroladores Avr de Atmel PDFDocumento13 pagineCapitulo 1 Del Curso de Microcontroladores Avr de Atmel PDFadrian reyesNessuna valutazione finora

- Catalogo LAPTOPSDocumento5 pagineCatalogo LAPTOPSAlex BernardoNessuna valutazione finora

- Arquitectura Interna Del MicroprocesadorDocumento24 pagineArquitectura Interna Del MicroprocesadorAlexis PeñateNessuna valutazione finora

- Arranque, imágenes y clonación de discosDocumento2 pagineArranque, imágenes y clonación de discoscrispardo851480% (5)

- Guia Curso Excel Avanzado Parte1 ConceptosBasicosDocumento33 pagineGuia Curso Excel Avanzado Parte1 ConceptosBasicosANGIE YULIETH COTAZO CRUZNessuna valutazione finora

- Ciencias de La Computación BrittanyDocumento8 pagineCiencias de La Computación BrittanynosemiclavedelotrocorreoNessuna valutazione finora

- DDF (Diagramas de Flujo)Documento8 pagineDDF (Diagramas de Flujo)mr_hscNessuna valutazione finora

- Fuente de Poder - ExposiciónDocumento1 paginaFuente de Poder - ExposiciónDanjela RoseroNessuna valutazione finora

- Informe Servicio TecnicoDocumento3 pagineInforme Servicio Tecnicoluchito_262Nessuna valutazione finora

- Plan de Entrenamiento para MADocumento16 paginePlan de Entrenamiento para MADiego FernandezNessuna valutazione finora

- IntroducciónDocumento39 pagineIntroducciónJIMY YERSON ROJAS CHAVEZNessuna valutazione finora

- Arquitectura de Computadoras 1 PDocumento5 pagineArquitectura de Computadoras 1 PMarco antonioNessuna valutazione finora

- Controlador de Logica ProgramableDocumento19 pagineControlador de Logica ProgramableSamed Maraza JaliriNessuna valutazione finora

- Partes Del PCDocumento10 paginePartes Del PCNancy BarajasNessuna valutazione finora