Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

STT-RAM Feasibility Study: Amr Amin

Caricato da

Saransh ParasharDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

STT-RAM Feasibility Study: Amr Amin

Caricato da

Saransh ParasharCopyright:

Formati disponibili

STT-RAM Feasibility Study

Amr Amin

UCLA

Jan 2010

Outline

Introduction

Memory Cell

Cell Area Calculation

Write Current Limitations

Reading Techniques and Limitations

Effect of Process Variations and Mismatch

MTJ Feasible Region

Area Minimization

Introduction

The need for a universal memory

Brief history of magnetic device memories

Description of the MTJ device

Literature survey

Summary of the paper flow

STT-RAM Cell

Schematic diagram

Anti-parallelizing / Parallelizing currents

Read disturb problem

Cell layout

Basic cell area vs. access device width

Effective Cell Area

This takes into account the overhead of:

Column MUX

Row decoder

Sense Amp

I/O circuits

Area optimization should also consider:

Optimum memory partitioning

Access transistor vs. column MUX areas

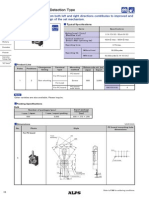

Write Current Limitations

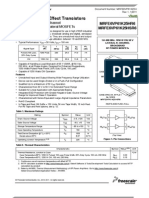

MOS drain current equation and fitting

Maximum allowed R

P

and R

AP

for certain

write current(s)

Column MUX design (justification for using

T-gates instead of P-transistors)

Effect of each of the four MUX devices on

the maximum allowed resistances

NMOS Drain Current

( )

( ) | |

( )

( )

( )

( ) ( )

4

V V

V ;

4

V V

V 1

V V 1

V V

4

L

W

C

4

V V

V 0 ; V V V V

V V 1

L

W

C

I

th GS

DS

th GS

DS

th GS

2

th GS

ox n

th GS

DS

2

DS DS th GS

th GS

ox n

D

>

(

|

|

.

|

\

|

+

+

|

.

|

\

|

s s

+

|

.

|

\

|

=

u

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

-200

0

200

400

600

800

1000

1200

1400

1600

Vds (V)

I

d

(

A

)

NMOS Simple Theoritical Model

Vgs=0.8V

Vgs=0.9V

Vgs=1.0V

Vgs=1.1V

Vgs=1.2V

Vgs=1.3V

Vgs=1.4V

Vgs=1.5V

Vgs=1.6V

Vgs=1.7V

Vgs=1.8V

Vgs=1.9V

Vgs=2.0V

PMOS Drain Current

( )

( ) | |

( )

( )

( )

( ) ( )

4

V V

V ;

4

V V

V 1

V V 1

V V

4

L

W

C

4

V V

V 0 ; V V V V

V V 1

L

W

C

I

th GS

DS

th GS

DS

th GS

2

th GS

ox p

th GS

DS

2

DS DS th GS

th GS

ox p

D

>

(

|

|

.

|

\

|

+

+

|

.

|

\

|

s s

+

|

.

|

\

|

=

u

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

-100

0

100

200

300

400

500

600

700

Vds (V)

I

d

(

A

)

PMOS Simple Theoritical Model

Vgs=0.8V

Vgs=0.9V

Vgs=1.0V

Vgs=1.1V

Vgs=1.2V

Vgs=1.3V

Vgs=1.4V

Vgs=1.5V

Vgs=1.6V

Vgs=1.7V

Vgs=1.8V

Vgs=1.9V

Vgs=2.0V

Maximum R

AP

V

G

V

G

V

G

V

DD

R

AP

X

I

P

M

N2

M

P1

M

N1

M

P2

M

a

( )

( ) ( )

1

1

1

2

,

0

1

2 2

p

p

n a

n a ox n

Par n

th G n

P n

th G

Par n

n th G

Par

AP,MAX

W

r

W W

W W

L

C

I

V V

I

V V

I

V V

I

V

R

|

|

.

|

\

|

+

|

.

|

\

|

+

q

u

q q

0 500 1000 1500 2000

0

1000

2000

3000

4000

5000

6000

7000

8000

9000

Writing Current (A)

R

A

P

,

M

A

X

(

O

)

Maximum Antiparallel Resistance (R

AP

)

Analytic

Simulation

Maximum R

P

V

G

V

G

V

DD

X

M

N1

M

P2

M

N2

M

P1

V

G

I

AP

M

a

R

P

( ) ( ) ( )

( ) | |

2

,

2

,

2

, ,

1

4 2 2

n

n

n th G n

a

ox n APar

n

APar

n th G

a

ox n

n n

APar

n th G

a

ox n

n n

APar

n th G

P,MAX

W

r

V V

L

W

C I

I

V V

L

W

C

I

V V

L

W

C

I

V V

R +

|

.

|

\

|

+

(

(

(

(

(

|

.

|

\

|

|

.

|

\

|

= u

u q

u q

0 500 1000 1500 2000

0

1000

2000

3000

4000

5000

6000

7000

8000

9000

Writing Current (A)

R

P

,

M

A

X

(

O

)

Maximum Parallel Resistance (R

P

)

Analytic

Simulation

Reading Limitations

Current sensing

Voltage sensing

( )( )

( ) ( )

2

2 1

2

1

2

1

|

|

.

|

\

|

+

|

|

.

|

\

|

+ + +

|

|

.

|

\

|

=

+ +

= A

P

on

P

on

P

R

on P on AP

P AP

R R

R

r

R

r

T T

T

R

V

r R r R

R R

V I

( )

T R I

R R I V

P R

P AP R R

2

1

2

1

=

= A

Constant Read Signal Contours

Current Sensing

P

R

R

on

R

R

P on

R

R

on

R

R

AP

R

V

I

r

V

I

R r

V

I

r

V

I

R

A

|

|

.

|

\

| A

+ +

A

=

2 2 1

2 1 2

2

Voltage Sensing

P

R

R

AP

R

I

V

R +

A

= 2

0 500 1000 1500 2000

0

200

400

600

800

1000

1200

1400

1600

1800

2000

R

P

(O)

R

A

P

(

O

)

Contours of Constant Read Current Signal

AI

R

= 0 A

AI

R

= 20 A

AI

R

= 40 A

AI

R

= 60 A

AI

R

= 80 A

AI

R

= 100 A

AI

R

= 120 A

0 500 1000 1500 2000

0

200

400

600

800

1000

1200

1400

1600

1800

2000

R

P

(O)

R

A

P

(

O

)

Contours of Constant Read Voltage Signal

AV

R

= 0 mV

AV

R

= 20 mV

AV

R

= 40 mV

AV

R

= 60 mV

AV

R

= 80 mV

AV

R

= 100 mV

AV

R

= 120 mV

Process Variations

MOS variations:

Min K and max VT

Reduce the maximum allowed R

P

and R

AP

Mismatch:

Degrades sensitivity of the SA

Higher nominal read margin is required

MTJ variations:

MgO thickness and area variations

Distort the nominal feasible region of the MTJ

Process Variations

( )

nom MgO RA nom

t t K RA RA + =

0 500 1000 1500 2000

0

1000

2000

3000

4000

5000

6000

7000

8000

9000

Writing Current (A)

R

P

,

M

A

X

(

O

)

Maximum Parallel Resistance (R

P

)

Nominal

/w 25%-K and 100mV-VT

/w 0.5A

o

MgO Variation

Nominal: Sim

0 500 1000 1500 2000

0

1000

2000

3000

4000

5000

6000

7000

8000

9000

Writing Current (A)

R

A

P

,

M

A

X

(

O

)

Maximum Antiparallel Resistance (R

AP

)

Nominal

/w 25%-K and 100mV-VT

/w 0.5A

o

MgO Variation

Nominal: Sim

( )

nom MgO TMR nom

t t K TMR TMR + =

MgO

nom

RA

P

P

t

RA

K

R

R

A =

A

MgO

nom

TMR

nom

RA

AP

AP

t

TMR

K

RA

K

R

R

A

|

|

.

|

\

|

+

+ =

A

1

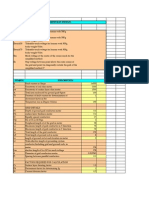

MTJ Feasible Region

What is the MTJ feasible region in the R

P

-

R

AP

plan given the following:

Desired write current

Desired basic cell area

Column MUX width

Certain technology

Certain variations (Yield)

Matching parameters (Yield)

Dec-2009 Tape-out

IBM-90nm-CMOS

V

WL

= V

DD

= 1 V

I

WR

= 500 A

W

a

=2.56 m

W

P,MUX

=16 m

W

N,MUX

=8 m

MOS K varies +/- 20%

MOS VT varies +/- 50mV

MTJ: RA = 2 .m

2

MTJ: K

RA

= 34 .m

2

/nm

MTJ: TMR = 100%

MTJ: K

TMR

= 200 %/nm

MTJ: t

MgO

= 0.2 A

o

Current Sensing: V

R

= 600 mV

Current Sensing: I

R

= 20 A

0 500 1000 1500 2000

0

200

400

600

800

1000

1200

1400

1600

1800

2000

R

P

(O)

R

A

P

(

O

)

MTJ Feasible Region

SRAM-Area Constraint

IBM-90nm-CMOS

V

WL

= V

DD

= 1 V

I

WR

= 500 A

W

a

=2.56 m

W

P,MUX

=16 m

W

N,MUX

=8 m

MOS K varies +/- 20%

MOS VT varies +/- 50mV

MTJ: RA = 2 .m

2

MTJ: K

RA

= 34 .m

2

/nm

MTJ: TMR = 100%

MTJ: K

TMR

= 200 %/nm

MTJ: t

MgO

= 0.2 A

o

Current Sensing: V

R

= 600 mV

Current Sensing: I

R

= 20 A

Flash-Area Constraint

DRAM-Area Constraint

Area Minimization Problem

Minimize: Effective cell area

Subject to:

MTJ resistances and write current value

MTJ variations

Parallelizing/Anti-parallelizing Write current equations

MOS variations and matching parameters

Speed must come into picture to constrain the

optimum memory partitioning

May be able to formulate this into a standard

optimization problem form that can be solved

efficiently

Remaining Issues

Analyzing Read/Write Speed and adding this as a

constraint in the optimization problem

The same with power

More analysis is needed for the minimum required

sensing signal (current or voltage)

CMOS mismatches and offset

Signal degradation due to MgO thickness variation

Possible signal degradation due to CMOS process variation

(dependant on the SA implementation)

Regenerating all results for different technologies

Potrebbero piacerti anche

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Da EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Valutazione: 4.5 su 5 stelle4.5/5 (3)

- P6NA60FP DatasheetDocumento5 pagineP6NA60FP DatasheetJess AJNessuna valutazione finora

- BL M15A881xxDocumento4 pagineBL M15A881xxRuben Dario RodriguezNessuna valutazione finora

- ACB - Tempower2Documento8 pagineACB - Tempower2Emma NuNessuna valutazione finora

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocumento8 pagineN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datauim0% (1)

- 0626-REF CT CALCS New Not ReviewedDocumento2 pagine0626-REF CT CALCS New Not ReviewedtceterexNessuna valutazione finora

- Mathcad - Opamp 1974Documento7 pagineMathcad - Opamp 1974Frank KarthikNessuna valutazione finora

- Led Dot Matrix: Row Cathode Column Anode Row Anode Column Cathode Typ MaxDocumento4 pagineLed Dot Matrix: Row Cathode Column Anode Row Anode Column Cathode Typ MaxarnaudmarielNessuna valutazione finora

- Processing Sequence7Documento5 pagineProcessing Sequence7Muhammad BilalNessuna valutazione finora

- Calculation Sheet - ElectDocumento73 pagineCalculation Sheet - Electsardarmkhan100% (1)

- Irfbc40A: Smps MosfetDocumento8 pagineIrfbc40A: Smps MosfetnandobnuNessuna valutazione finora

- DIC QuestionsDocumento2 pagineDIC QuestionsAshish KrNessuna valutazione finora

- STP2NA50 Stp2Na50Fi: N - Channel Enhancement Mode Power Mos TransistorDocumento6 pagineSTP2NA50 Stp2Na50Fi: N - Channel Enhancement Mode Power Mos TransistorMatei LaurentiuNessuna valutazione finora

- Power Bridge Rectifiers: FeaturesDocumento3 paginePower Bridge Rectifiers: FeaturesshamkhairnarNessuna valutazione finora

- STP6NA60 Stp6Na60Fi: N - Channel Enhancement Mode Fast Power Mos TransistorDocumento10 pagineSTP6NA60 Stp6Na60Fi: N - Channel Enhancement Mode Fast Power Mos TransistorAlejandro Borrego DominguezNessuna valutazione finora

- RF Power Field Effect Transistors: MRFE6VP61K25HR6 MRFE6VP61K25HSR6Documento13 pagineRF Power Field Effect Transistors: MRFE6VP61K25HR6 MRFE6VP61K25HSR6Zoran DjuricNessuna valutazione finora

- MRF6S18100Documento20 pagineMRF6S18100Nguyen Van CuongNessuna valutazione finora

- MR758Documento7 pagineMR758Bruno NascimentoNessuna valutazione finora

- Led Numeric Display, 1 Digit: Part No Chip VF Unit:V Typ Max Iv TYP. (MCD)Documento5 pagineLed Numeric Display, 1 Digit: Part No Chip VF Unit:V Typ Max Iv TYP. (MCD)Angel DemianNessuna valutazione finora

- P4NC60Documento9 pagineP4NC60Gabino OrtizNessuna valutazione finora

- 1.2-Current Differential Relay (RED670)Documento32 pagine1.2-Current Differential Relay (RED670)JenniferKujanpaa100% (2)

- 382096dataDocumento1 pagina382096dataPoentech CANessuna valutazione finora

- Analizador de Redes EXTECHDocumento1 paginaAnalizador de Redes EXTECHgahh24Nessuna valutazione finora

- Homework Assignment 8 SolutionDocumento8 pagineHomework Assignment 8 SolutionKL Chiang100% (1)

- P7NA60FI STMicroelectronicsDocumento10 pagineP7NA60FI STMicroelectronicsLuis Granadillo OjedaNessuna valutazione finora

- P3NA80FI DatasheetDocumento10 pagineP3NA80FI DatasheetAnonymous RCPxaonfvNessuna valutazione finora

- mbrx0540 Schottky Barrier DiodeDocumento5 paginembrx0540 Schottky Barrier DiodeMochammad SofyanNessuna valutazione finora

- RF and Microwave Transistors Avionics Applications: Description: DescriptionDocumento5 pagineRF and Microwave Transistors Avionics Applications: Description: DescriptionMuhammad Ayaz ZakirNessuna valutazione finora

- SSC Frere Rre RerDocumento4 pagineSSC Frere Rre RershyhuNessuna valutazione finora

- Table 9.1Documento1 paginaTable 9.1thanhnho1Nessuna valutazione finora

- PV Exercise Solutions PDFDocumento13 paginePV Exercise Solutions PDFW4tsonn100% (2)

- 3ph Isc at LV InstallationDocumento7 pagine3ph Isc at LV InstallationbambangNessuna valutazione finora

- VLSI Assignment 2Documento34 pagineVLSI Assignment 2Dhanvanth MuttaNessuna valutazione finora

- HT Cable Sizing Selection Criteriafor 5Documento9 pagineHT Cable Sizing Selection Criteriafor 5maheshNessuna valutazione finora

- Kew Ac/Dc Clamp Meters: Model ModelDocumento2 pagineKew Ac/Dc Clamp Meters: Model ModelDarwin Castañeda DussanNessuna valutazione finora

- Ms02302a SDocumento10 pagineMs02302a Sfamunoz2705Nessuna valutazione finora

- N - Channel 800V - 1.8 - 5A - To-220/To-220Fp Powermesh MosfetDocumento10 pagineN - Channel 800V - 1.8 - 5A - To-220/To-220Fp Powermesh MosfetHerpadianaNessuna valutazione finora

- Analog & Digital VLSI Design Analog Assignment: 1. ObjectiveDocumento37 pagineAnalog & Digital VLSI Design Analog Assignment: 1. ObjectivewrkahlcNessuna valutazione finora

- AFT05MP075NDocumento21 pagineAFT05MP075NjeremyAW2SNessuna valutazione finora

- Basics of Squirrel Cage Induction Motor DesignDocumento29 pagineBasics of Squirrel Cage Induction Motor Designरमेश सिंह100% (1)

- PARTNER - LSA 52.2 XL80 4P 50Hz 6600V - en - 1-2011Documento5 paginePARTNER - LSA 52.2 XL80 4P 50Hz 6600V - en - 1-2011Dmitrii MelnikNessuna valutazione finora

- MTW14N50EDocumento8 pagineMTW14N50EroozbehxoxNessuna valutazione finora

- VLSI Design: Lecture 3a: Nonideal TransistorsDocumento30 pagineVLSI Design: Lecture 3a: Nonideal TransistorsBhagirath BhattNessuna valutazione finora

- Traditional Design of Cage Rotor Induction MotorsDocumento35 pagineTraditional Design of Cage Rotor Induction MotorsMohammad Gulam AhamadNessuna valutazione finora

- STP5NA80 DatasheetDocumento10 pagineSTP5NA80 Datasheetdusan1962Nessuna valutazione finora

- Mart Data2001bDocumento30 pagineMart Data2001bdffdfNessuna valutazione finora

- E PDFDocumento178 pagineE PDFVasu IyerNessuna valutazione finora

- 3.earth MatDocumento9 pagine3.earth MatPrabhash Verma100% (1)

- Spvq9: Water-Proof TypeDocumento3 pagineSpvq9: Water-Proof TypeshyhuNessuna valutazione finora

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocumento15 pagineUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceNessuna valutazione finora

- Datasheet Septa 31 RuagDocumento7 pagineDatasheet Septa 31 RuagPatosanNessuna valutazione finora

- Appa-Module 6-Fault Current AnalysisDocumento65 pagineAppa-Module 6-Fault Current Analysisrasim_m11460% (1)

- Oc SC Test On SynchronousDocumento5 pagineOc SC Test On SynchronousRam NiwasNessuna valutazione finora

- Opa381 PDFDocumento19 pagineOpa381 PDFVictoria Guerrero100% (1)

- BUZ80A Datasheet - Eeworld.com - CNDocumento10 pagineBUZ80A Datasheet - Eeworld.com - CNJose ariasNessuna valutazione finora

- Stp6Nk60Z - Stp6Nk60Zfp STB6NK60Z - STB6NK60Z-1Documento13 pagineStp6Nk60Z - Stp6Nk60Zfp STB6NK60Z - STB6NK60Z-1servitecolorNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- IBPS SO Previous Years Papers - Download Now!Documento131 pagineIBPS SO Previous Years Papers - Download Now!Tushita85% (98)

- Relational DatabaseDocumento91 pagineRelational DatabaseSaransh ParasharNessuna valutazione finora

- SPINTTRAMDocumento21 pagineSPINTTRAMSaransh ParasharNessuna valutazione finora

- Presentation On STT RamDocumento20 paginePresentation On STT RamSaransh ParasharNessuna valutazione finora

- Designing and Building A Computer TableDocumento9 pagineDesigning and Building A Computer Tablemaster_codersNessuna valutazione finora

- The History of AstrologyDocumento36 pagineThe History of AstrologyDharani Dharendra DasNessuna valutazione finora

- AS and A Level: ChemistryDocumento11 pagineAS and A Level: ChemistryStingy BieNessuna valutazione finora

- Skincare Routine Order Cheat SheetDocumento10 pagineSkincare Routine Order Cheat SheetYel Salenga100% (3)

- Segmentation of Blood Vessels Using Rule-Based and Machine-Learning-Based Methods: A ReviewDocumento10 pagineSegmentation of Blood Vessels Using Rule-Based and Machine-Learning-Based Methods: A ReviewRainata PutraNessuna valutazione finora

- Tips For A Healthy PregnancyDocumento2 pagineTips For A Healthy PregnancyLizaNessuna valutazione finora

- 8-General Rules For Erection ProcedureDocumento4 pagine8-General Rules For Erection ProcedurePrijin UnnunnyNessuna valutazione finora

- DIVAR IP All-In-One 7000 3U Datasheet 51 en 66297110155Documento5 pagineDIVAR IP All-In-One 7000 3U Datasheet 51 en 66297110155Javier RochaNessuna valutazione finora

- Metal Workers BizHouse - UkDocumento3 pagineMetal Workers BizHouse - UkAlex BekeNessuna valutazione finora

- Tabla de Avances de AcesoriosDocumento3 pagineTabla de Avances de AcesoriosPedro Diaz UzcateguiNessuna valutazione finora

- G10Mapeh Exam First QuaterDocumento8 pagineG10Mapeh Exam First QuaterJonas LamcisNessuna valutazione finora

- Ap, Lrrsisal of Roentgenograph, Ic: I SsayDocumento30 pagineAp, Lrrsisal of Roentgenograph, Ic: I SsayMindaugasStacevičiusNessuna valutazione finora

- GB GW01 14 04 02Documento2 pagineGB GW01 14 04 02Muhammad LukmanNessuna valutazione finora

- The Practical Reference Guide ForDocumento4 pagineThe Practical Reference Guide Forelias667Nessuna valutazione finora

- Eco Exercise 3answer Ans 1Documento8 pagineEco Exercise 3answer Ans 1Glory PrintingNessuna valutazione finora

- Synthesis Essay Coming To Grips With GenesisDocumento11 pagineSynthesis Essay Coming To Grips With Genesisapi-259381516Nessuna valutazione finora

- Yoga SadhguruDocumento6 pagineYoga Sadhgurucosti.sorescuNessuna valutazione finora

- Presentation AcetanilideDocumento22 paginePresentation AcetanilideNovitasarii JufriNessuna valutazione finora

- V. Jovicic and M. R. Coop1997 - Stiffness, Coarse Grained Soils, Small StrainsDocumento17 pagineV. Jovicic and M. R. Coop1997 - Stiffness, Coarse Grained Soils, Small StrainsxiangyugeotechNessuna valutazione finora

- Wildlife Emergency and Critical CareDocumento14 pagineWildlife Emergency and Critical CareRayssa PereiraNessuna valutazione finora

- Clocks (New) PDFDocumento5 pagineClocks (New) PDFAbhay DabhadeNessuna valutazione finora

- Book Index The Art of Heavy TransportDocumento6 pagineBook Index The Art of Heavy TransportHermon Pakpahan50% (2)

- 988611457NK448908 Vehicle Scan ReportDocumento5 pagine988611457NK448908 Vehicle Scan ReportVictor Daniel Piñeros ZubietaNessuna valutazione finora

- Contoh CV / Daftar Riwayat HidupDocumento2 pagineContoh CV / Daftar Riwayat HiduprusmansyahNessuna valutazione finora

- BIF-V Medium With Preload: DN Value 130000Documento2 pagineBIF-V Medium With Preload: DN Value 130000Robi FirdausNessuna valutazione finora

- Science Magazine February 2020Documento133 pagineScience Magazine February 2020Elena González GonzálezNessuna valutazione finora

- 15 Benefits of CyclingDocumento8 pagine15 Benefits of CyclingJoycs PintoNessuna valutazione finora

- Coding DecodingDocumento21 pagineCoding DecodingAditya VermaNessuna valutazione finora

- Pusheen With Donut: Light Grey, Dark Grey, Brown, RoséDocumento13 paginePusheen With Donut: Light Grey, Dark Grey, Brown, RosémafaldasNessuna valutazione finora

- Aquaculture Scoop May IssueDocumento20 pagineAquaculture Scoop May IssueAquaculture ScoopNessuna valutazione finora