Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Elc601 Lecture1 Mos

Caricato da

Mohammed El-masreCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Elc601 Lecture1 Mos

Caricato da

Mohammed El-masreCopyright:

Formati disponibili

Analog Integrated Circuits

Lecture 1: Introduction and MOS

Physics

ELC 601 Fall 2013

Dr. Ahmed Nader

Dr. Mohamed M. Aboudina

anader@ieee.org

maboudina@gmail.com

Department of Electronics and Communications Engineering

Faculty of Engineering Cairo University

11/1/2013 Ahmed Nader, 2013

2

Syllabus

Text book:

Design of Analog CMOS Integrated Circuits by Behzad Razavi

Website: http://scholar.cu.edu.eg/anader/

Email: anader@ieee.org

Office hours:

Sunday 4:00 5:00 pm

Monday 4:00 5:00 pm

Week Lecture/Studio Topic Chapter

1 MOS Physics + Short Channel Effects 2 + 16

2 Single Stage Amplifiers + Frequency Response 3 + 6

3 Differential Amplifiers 4

4 Current Sources/Mirrors 5

5 Operational Amplifier Design 9

6 Operational Amplifier Design 10

7 Operational Amplifier Design 10

11/1/2013 Ahmed Nader, 2013

3

Contents

Analog Signal Processing Vs. Digital Signal Processing

IC Fabrication

Passives

MOS: Device Physics

MOS Structure and Threshold Voltage

MOS I-V Characteristics

MOS Non-idealities (Channel length modulation, Body effect)

Subthreshold Conduction

MOS Intrinsic capacitance and small-signal model

Velocity Saturation

11/1/2013 Ahmed Nader, 2013

4

Digital Signal Processing

11/1/2013 Ahmed Nader, 2013

5

Analog Signal Processing

11/1/2013 Ahmed Nader, 2013

6

Analog Signal Processing

11/1/2013 Ahmed Nader, 2013

7

Data Converters

11/1/2013 Ahmed Nader, 2013 8

11/1/2013 Ahmed Nader, 2013

9

Integrated Circuits

11/1/2013 Ahmed Nader, 2013

10

IC Fabrication

Semiconductor device fabrication is the process used to

create integrated circuits (silicon chips)

Done in a clean room (Fab facility)

Takes 6-8 weeks

11/1/2013 Ahmed Nader, 2013

11

Video

11/1/2013 Ahmed Nader, 2013

12

Semiconductor Industry

Semiconductor IC industry had revenues that reached $295

billion last year (2012).

Microcontrollers (MC), Digital Signal Processors (DSP) and

Microprocessors (MP) have been the center of the IC revolution

since the beginning.

The Personal Computer (PC) boom of the last century has

become the Smartphone, Entertainment Console, Notebook

and Tablet explosion in the new millennium.

Largest companies in that industry are: Intel with $50 billion

revenue in 2012. Samsung Electronics ranked second.

Qualcomm, Texas instruments, Toshiba rounding out the top 5.

Largest manufacturers (Fab facilities): Intel, TSMC,

STMicroelectronics, IBM

11/1/2013 Ahmed Nader, 2013

13

CMOS Cross Section

PDK=Process Development Kit

Remember Z dimensions cannot be changed and are fab dependent

14

Devices in a PDK

11/1/2013 Ahmed Nader, 2013

11/1/2013 Ahmed Nader, 2013

15

Integrated Resistors

11/1/2013 Ahmed Nader, 2013

16

Integrated Resistors

11/1/2013 Ahmed Nader, 2013

17

Diffusion Resistors

11/1/2013 Ahmed Nader, 2013

18

Integrated Capacitors: Poly-Poly

In range of pF

Accuracy +/-15%

11/1/2013 Ahmed Nader, 2013

19

Integrated Capacitors: MIM (Metal-Insulator-Metal)

11/1/2013 Ahmed Nader, 2013

20

Integrated Capacitors: MOM (Metal-Oxide-Metal)

11/1/2013 Ahmed Nader, 2013

21

Integrated Inductors

Widely Used in RF circuits (L in the range of nH)

Low quality factor

11/1/2013 Ahmed Nader, 2013

22

Integrated Inductors: Multi-Layer Spiral Inductors

23

An Example of a Commercial IBM Process

11/1/2013 Ahmed Nader, 2013

24

An Example of a Commercial IBM Process

11/1/2013 Ahmed Nader, 2013

11/1/2013 Ahmed Nader, 2013

25

Packaged Chip + Chip Micrograph

Wi-Fi Receiver

17mm

2

11/1/2013 Ahmed Nader, 2013

26

MOS Structure

A piece of polysilicon with a width of W and length of L on top of a

thin layer of oxide defines the gate area.

Source and drain areas are heavily doped.

Substrate usually tied to the most negative voltage.

Leff = L 2L

D

, where L

D

is the side diffusion of source and drain.

11/1/2013 Ahmed Nader, 2013

27

MOS characteristics Threshold Voltage

11/1/2013 Ahmed Nader, 2013

28

MOS characteristics Threshold Voltage

11/1/2013 Ahmed Nader, 2013

29

MOS characteristics Threshold Voltage

Remember PVT (Process, Voltage, Temperature Variations)

11/1/2013 Ahmed Nader, 2013

30

MOS I-V characteristics

11/1/2013 Ahmed Nader, 2013

31

MOS I-V characteristics

11/1/2013 Ahmed Nader, 2013

32

MOS I-V characteristics

11/1/2013 Ahmed Nader, 2013

33

MOS Device as a Resistor

11/1/2013 Ahmed Nader, 2013

34

MOS I-V characteristics

11/1/2013 Ahmed Nader, 2013

35

MOS I-V characteristics

11/1/2013 Ahmed Nader, 2013

36

MOS: In Saturation

11/1/2013 Ahmed Nader, 2013

37

MOS: Channel length modulation

Channel length modulation by V

DS

causes the saturation current to

vary with V

DS

.

is the channel length modulation parameter (V

-1

)

11/1/2013 Ahmed Nader, 2013

38

MOS: Channel length modulation

undesired second order effect

11/1/2013 Ahmed Nader, 2013

39

MOS: Substrate or Body Effect

11/1/2013 Ahmed Nader, 2013

40

MOS: Bulk Driven

Can be used in low-voltage applications

11/1/2013 Ahmed Nader, 2013

41

Body Effect: Non-linearity

11/1/2013 Ahmed Nader, 2013

42

Substrate: Where to connect it?

For NMOS

To the most negative available potential

To a carefully designed potential (for example source such that V

SB

=0)

in the case of twin well process or triple well (deep NWELL) process

11/1/2013 Ahmed Nader, 2013

43

Triple Well Option

11/1/2013 Ahmed Nader, 2013

44

Region of Operation: Conceptual Visualization

V

DS

< V

GS

-V

TH

MOS transistor in linear region.

In linear region, MOS transistor acts as a resistor or a switch.

NMOS PMOS

11/1/2013 Ahmed Nader, 2013

45

MOS: Subthreshold (Weak Inversion)

Subthreshold Conduction:

For V

GS

near V

TH

, I

D

has an exponential dependence on V

GS

:

Max transconductance efficiency

Used for low currents & low frequency applications

11/1/2013 Ahmed Nader, 2013

46

MOS: Intrinsic Capacitance

C1 is the gate-channel capacitance

C2 is the channel-bulk depletion capacitance

C3 & C4 is the overlap gate-source(drain) capacitance

C5 & C6 is the source/drain bulk junction capacitance (bottom-

plate and sidewall)

Note that junction capacitors are voltage-dependent (non-linear)

11/1/2013 Ahmed Nader, 2013

47

MOS: Intrinsic Capacitance

11/1/2013 Ahmed Nader, 2013

48

MOS Device as a Capacitor: Varactor

Assignment 1a:

There is a special device with n-doping in

an NWELL. Plot the characteristics of such

a device. Comment on its properties.

11/1/2013 Ahmed Nader, 2013

49

Small Signal Model

The slope of the diode characteristic at the

Q-point is called the diode conductance

and is given by:

g

d

is small but non-zero for I

D

= 0 because

slope of diode equation is nonzero at the

origin.

Diode resistance is given by:

g

d

=

ci

D

cv

D

Q point

=

I

S

V

T

exp

V

D

V

T

|

\

|

.

|

|

=

I

D

+I

S

V

T

g

d

~

I

D

V

T

~

I

D

0.025V

=40I

D

for I

D

>>I

S

r

d

=

1

g

d

11/1/2013 Ahmed Nader, 2013

50

Small Signal Operation of a Diode

i

D

=I

S

exp

v

D

V

T

|

\

|

.

|

|

1

(

(

(

(

(

I

D

+i

d

=I

S

exp

V

D

+v

d

V

T

|

\

|

.

|

|

1

(

(

(

(

(

I

D

+i

d

=I

S

exp

V

D

V

T

|

\

|

.

|

|

1

(

(

(

(

(

+I

S

exp

v

D

V

T

|

\

|

.

|

|

v

d

V

T

+

1

2

v

d

V

T

|

\

|

.

|

|

2

+

1

6

v

d

V

T

|

\

|

.

|

|

3

+...

(

(

(

(

Subtracting I

D

from both sides of the equation,

i

d

=(I

D

+I

S

)

v

d

V

T

+

1

2

v

d

V

T

|

\

|

.

|

|

2

+

1

6

v

d

V

T

|

\

|

.

|

|

3

+...

(

(

(

(

For i

d

to be a linear function of signal voltage v

d

,

This represents the requirement for small-signal operation of the diode.

mV v V v

d T d

5 or V 05 . 0 2 s = <<

i

d

=(I

D

+I

S

)

v

d

V

T

|

\

|

.

|

|

=g

d

v

d

i

D

=I

D

+g

d

v

d

11/1/2013 Ahmed Nader, 2013

51

Current Controlled Attenuator

Magnitude of ac voltage v

o

developed

across diode can be controlled by value

of dc bias current applied to diode.

From dc equivalent circuit I

D

= I,

From ac equivalent circuit,

v

o

=v

i

r

d

r

d

+R

I

|

\

|

.

|

|

=v

i

1

1+

R

I

r

d

v

o

=v

i

1

1+

(I +I

S

)R

I

V

T

For R

I

= 1 kO, I

S

= 10

-15

A,

If I = 0, v

o

= v

i

, magnitude of v

i

is

limited to only 5 mV.

If I = 100 A, input signal is

attenuated by a factor of 5, and v

i

can have a magnitude of 25 mV.

11/1/2013

52

Small-Signal Model of a MOS (Two-Port Model)

Using 2-port y-parameter network,

The port variables can represent either

time-varying part of total voltages and

currents or small changes in them away

from Q-point values.

i

g

= y

11

v

gs

+y

12

v

ds

i

d

= y

21

v

gs

+y

22

v

ds

y

11

=

i

g

v

gs

v

ds

= 0

=

ci

G

cv

GS

Q point

=0

y

12

=

i

g

v

ds

v

gs

= 0

=

ci

G

cv

DS

Q point

=0

y

21

=

i

d

v

gs

v

ds

= 0

=

ci

D

cv

GS

Q point

=

2I

D

V

GS

V

TN

y

22

=

i

d

v

ds

v

gs

= 0

=

ci

D

cv

DS

Q point

=

I

D

1

+V

DS

11/1/2013

53

Small-Signal Model of a MOS

Since gate is insulated from

channel by gate-oxide input

resistance of transistor is infinite.

Small-signal parameters are

controlled by the Q-point.

For same operating point, MOSFET

has lower transconductance and

lower output resistance that BJT.

Transconductance:

g

m

= y

21

=

2I

D

V

GS

V

TN

= 2K

n

I

D

Output resistance:

D

o

I y

r

1 1

22

~ =

MOS Transistor

Ahmed Nader, 2013

54

11/1/2013

MOS Transistor

Ahmed Nader, 2013

55

Small Signal Model: Body Effect

11/1/2013

Drain current depends on threshold voltage which in

turn depends on v

SB

. Back-gate transconductance

is:

0 < q < 1 is called back-gate tranconductance

parameter.

g

mb

=

ci

D

cv

BS

Q point

=

ci

D

cv

SB

Q point

g

mb

=

ci

D

cV

TN

|

\

|

.

|

|

cV

TN

cv

SB

|

\

|

.

|

|

Q point

=(g

m

q)=g

m

q

11/1/2013 Ahmed Nader, 2013

56

Small-Signal Model of a MOS: High Frequency Model

Voltage dependent current source (g

m

V

gs

) models dependence of

drain current on gate-source voltage

Output resistance models dependence of drain current on drain-

source voltage (channel length modulation)

Voltage dependent current source (g

mb

V

bs

) models dependence of

drain current on bulk-source voltage (body effect)

MOS Transistor

Ahmed Nader, 2013

57

Useful Model

Small Signal:

+

-

11/1/2013

MOS Transistor

Ahmed Nader, 2013

58

Special Cases

Bias point

11/1/2013

11/1/2013 Ahmed Nader, 2013

59

Deep Sub-Micron Technologies

11/1/2013 Ahmed Nader, 2013

60

Low-voltage High-

Speed trade-off

Fixed for the

technology and

fixed L

11/1/2013 Ahmed Nader, 2013

61

Deep Sub-Micron Technologies

Some small geometry effects:

1- Gate leakage

2- Threshold voltage variation

3- Output impedance variation with V

DS

(non-linearity

)

4- Mobility degradation with vertical field

5- Velocity saturation

6- Reliability Effects (GO, Hot Carrier, NBTI, ..)

7- Stress Effects (STI, Well Proximity, ..)

Assignment 1b:

Choose one of those effects and describe it in details

(physical meaning, effect on performance, etc.)

11/1/2013

62

Deep Sub-Micron Technologies

Ahmed Nader, 2013

What about scaling of V

th

?

11/1/2013 Ahmed Nader, 2013

63

Deep Sub-Micron Technologies Mobility degradation with Vertical Field

Carriers are confined to a narrower region below oxide-

silicon interface leading to more carrier scattering and hence

lower mobility

11/1/2013 Ahmed Nader, 2013

64

Deep Sub-Micron Technologies Velocity Saturation

11/1/2013 Ahmed Nader, 2013

65

Deep Sub-Micron Technologies Velocity Saturation

11/1/2013 Ahmed Nader, 2013

66

MOS Device Models

Level 3 Model

BSIM (Berkeley Short-Channel IGFET Model)

Potrebbero piacerti anche

- Book of Lost Spells (Necromancer Games)Documento137 pagineBook of Lost Spells (Necromancer Games)Rodrigo Hky91% (22)

- Complimentary JournalDocumento58 pagineComplimentary JournalMcKey ZoeNessuna valutazione finora

- How 50 Million People Are Changing the WorldDocumento5 pagineHow 50 Million People Are Changing the WorldCTRCTR0% (1)

- 2019 IL and Federal Pharmacy Law Review PDFDocumento176 pagine2019 IL and Federal Pharmacy Law Review PDFAnonymous 3YNJfYNQ100% (5)

- The Transformation of Metaphysical ScienceDocumento7 pagineThe Transformation of Metaphysical ScienceblavskaNessuna valutazione finora

- Writing Simple Sentences to Describe ScenariosDocumento5 pagineWriting Simple Sentences to Describe Scenariosepol67% (3)

- MOS Integrated Circuit DesignDa EverandMOS Integrated Circuit DesignE. WolfendaleNessuna valutazione finora

- EC6601-VLSI Design 2 Mark QuestionsDocumento21 pagineEC6601-VLSI Design 2 Mark QuestionsArun ChezianNessuna valutazione finora

- EMC of ICs Masters STU 2009Documento105 pagineEMC of ICs Masters STU 2009Lily BabouNessuna valutazione finora

- Hall-Effect Sensors: Theory and ApplicationDa EverandHall-Effect Sensors: Theory and ApplicationValutazione: 5 su 5 stelle5/5 (1)

- 2 Mark Questions & AnswersDocumento6 pagine2 Mark Questions & AnswersMuthu KumarNessuna valutazione finora

- PE and Health 12 - Module 7Documento19 paginePE and Health 12 - Module 7Stephen Lorenzo A. DoriaNessuna valutazione finora

- Tutorial Backpropagation Neural NetworkDocumento10 pagineTutorial Backpropagation Neural NetworkHeru PraNessuna valutazione finora

- Ch. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocumento43 pagineCh. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- Scaling Factors and Scaling ParametersDocumento22 pagineScaling Factors and Scaling Parametersvirajitha159467% (3)

- Department of Education Doña Asuncion Lee Integrated School: Division of Mabalacat CityDocumento2 pagineDepartment of Education Doña Asuncion Lee Integrated School: Division of Mabalacat CityRica Tano50% (2)

- Project Report On Discontinuous Puf Panels Using Cyclopentane As A Blowing AgentDocumento6 pagineProject Report On Discontinuous Puf Panels Using Cyclopentane As A Blowing AgentEIRI Board of Consultants and PublishersNessuna valutazione finora

- Italian Painters 02 MoreDocumento450 pagineItalian Painters 02 Moregkavvadias2010Nessuna valutazione finora

- Digital Integrated Circuits: A Design PerspectiveDocumento66 pagineDigital Integrated Circuits: A Design Perspectiveapi-127299018Nessuna valutazione finora

- Electronics & Communication Engineering Sagar Institute of Technology & ManagementDocumento22 pagineElectronics & Communication Engineering Sagar Institute of Technology & ManagementShashank DubeyNessuna valutazione finora

- Ec3552-Vlsi and Chip Design-1251555713-Vlsi QB r2021Documento40 pagineEc3552-Vlsi and Chip Design-1251555713-Vlsi QB r2021jasmine reenaNessuna valutazione finora

- Electronics & Communication Engineering Sagar Institute of Technology & ManagementDocumento23 pagineElectronics & Communication Engineering Sagar Institute of Technology & ManagementShashank DubeyNessuna valutazione finora

- Lab 7Documento3 pagineLab 7Muhammad IbrahimNessuna valutazione finora

- Peter H ChenDocumento10 paginePeter H ChenYunping HuangNessuna valutazione finora

- Flash ADC Design Challenges and MethodologyDocumento15 pagineFlash ADC Design Challenges and MethodologyJagadeep KumarNessuna valutazione finora

- KCB Technical Academy Indore (M.P.) : "Dark Detector With 555 Timer"Documento27 pagineKCB Technical Academy Indore (M.P.) : "Dark Detector With 555 Timer"Ankit SharmaNessuna valutazione finora

- 555 Timer Final ReportDocumento36 pagine555 Timer Final ReportRavi Dubey100% (1)

- Bwire Ans AssgDocumento5 pagineBwire Ans AssgEria NalwasaNessuna valutazione finora

- Vlsi 2 Marks QSDocumento16 pagineVlsi 2 Marks QSJay SubbareddyNessuna valutazione finora

- Chp1-2 Print BookDocumento40 pagineChp1-2 Print Bookbalaji_gawalwad9857Nessuna valutazione finora

- Monolithic IC-Component FabricationDocumento6 pagineMonolithic IC-Component FabricationThamaraikannan Loganathan100% (2)

- Chapter3 Rabaey MOS Capacitances OnlyDocumento19 pagineChapter3 Rabaey MOS Capacitances OnlyRaheetha AhmedNessuna valutazione finora

- Design of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFDocumento6 pagineDesign of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFAyush MalhotraNessuna valutazione finora

- Unit 1-VlsiDocumento34 pagineUnit 1-Vlsikingzyper19Nessuna valutazione finora

- Scaling & EconomicsDocumento29 pagineScaling & EconomicsRoshdy AbdelRassoulNessuna valutazione finora

- Mos Capacitances: EEE C443 Analog and Digital VLSI DesignDocumento63 pagineMos Capacitances: EEE C443 Analog and Digital VLSI DesignAnurag LaddhaNessuna valutazione finora

- Digital Integrated CircuitsDocumento66 pagineDigital Integrated CircuitsRegina MerlinNessuna valutazione finora

- BEC Micro Project (Report)Documento14 pagineBEC Micro Project (Report)roshni60% (5)

- VLSI Circuit Simulation and Spice ModelingDocumento34 pagineVLSI Circuit Simulation and Spice ModelingKiran SankarNessuna valutazione finora

- Underground Cable Fault Detection and Location Finding: XXXXXXX 1XxxxxxDocumento38 pagineUnderground Cable Fault Detection and Location Finding: XXXXXXX 1Xxxxxxshaik shaNessuna valutazione finora

- Eee 4154Documento16 pagineEee 4154Mehedi HasanNessuna valutazione finora

- Vlsi Question BankDocumento14 pagineVlsi Question BankGokila Vani50% (2)

- Design and Development of Y-Shape Power Divider Using Improved DgsDocumento4 pagineDesign and Development of Y-Shape Power Divider Using Improved DgsInternational Journal of Application or Innovation in Engineering & ManagementNessuna valutazione finora

- Irjet V8i5487Documento3 pagineIrjet V8i5487Sado HusseinYusufNessuna valutazione finora

- Digital Integrated Circuits: A Design PerspectiveDocumento55 pagineDigital Integrated Circuits: A Design Perspectiveapi-127299018Nessuna valutazione finora

- Lecture - MOS & MOSFET-1Documento21 pagineLecture - MOS & MOSFET-1Kartika MunirNessuna valutazione finora

- TelegramDocumento20 pagineTelegramVani telluriNessuna valutazione finora

- Design of High-Speed Comparator For LVDS ReceiverDocumento3 pagineDesign of High-Speed Comparator For LVDS ReceiverHassan FarssiNessuna valutazione finora

- Car Parking SensorDocumento39 pagineCar Parking SensorSubarna Poddar100% (10)

- Saes T 883Documento13 pagineSaes T 883luke luckyNessuna valutazione finora

- ECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2011Documento28 pagineECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2011api-127299018Nessuna valutazione finora

- Stick DiagramDocumento72 pagineStick DiagramBhanu Bond0% (1)

- Analysis of Fault Detection and Location in Medium Voltage Radial Networks With Distributed GenerationDocumento6 pagineAnalysis of Fault Detection and Location in Medium Voltage Radial Networks With Distributed Generationarman0154Nessuna valutazione finora

- GTU VLSI Question Bank Covers Design, Fabrication & CircuitsDocumento4 pagineGTU VLSI Question Bank Covers Design, Fabrication & CircuitsAmish TankariyaNessuna valutazione finora

- New CMOS Voltage Divider Based Current Mirror, Compared With The Basic and Cascode Current MirrorsDocumento6 pagineNew CMOS Voltage Divider Based Current Mirror, Compared With The Basic and Cascode Current MirrorsvlsijpNessuna valutazione finora

- Iiiyr Visem Vlsi DesignDocumento20 pagineIiiyr Visem Vlsi DesignlokeshwarrvrjcNessuna valutazione finora

- Rbs Engineering Technical Campus Bichpuri, AgraDocumento20 pagineRbs Engineering Technical Campus Bichpuri, AgraVipin KushwaNessuna valutazione finora

- CMOS Question FN-3Documento3 pagineCMOS Question FN-3alokjadhavNessuna valutazione finora

- Underground Wire Fault Detector ProjectDocumento4 pagineUnderground Wire Fault Detector Projectsrakhisharma41Nessuna valutazione finora

- Underground Cable Fault Finding Robot Using GSM Technology and AT MEGA 16 InterfacingDocumento3 pagineUnderground Cable Fault Finding Robot Using GSM Technology and AT MEGA 16 InterfacingInfogain publicationNessuna valutazione finora

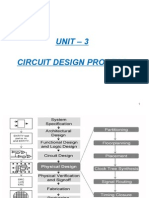

- Unit - 3 Circuit Design ProcessDocumento30 pagineUnit - 3 Circuit Design ProcessNagarjun RajputNessuna valutazione finora

- 598464.design of Planar Inductor Jkundrata AbaricDocumento7 pagine598464.design of Planar Inductor Jkundrata AbaricbiznizNessuna valutazione finora

- NTNU Exam in Integrated Circuit DesignDocumento21 pagineNTNU Exam in Integrated Circuit DesignenekoNessuna valutazione finora

- Thermal Overload ProtectorDocumento69 pagineThermal Overload ProtectorSai Printers100% (1)

- DC Motor CTRL Using Single SwitchDocumento44 pagineDC Motor CTRL Using Single SwitchAbhijeet NayakNessuna valutazione finora

- EECE 412/612: Digital Integrated Circuits: Dept. of Electrical and Compute Engineering American University of BeirutDocumento36 pagineEECE 412/612: Digital Integrated Circuits: Dept. of Electrical and Compute Engineering American University of BeirutYoussef HobballahNessuna valutazione finora

- Fibre Optic Connectors PenetratorsDocumento17 pagineFibre Optic Connectors PenetratorsquanNessuna valutazione finora

- ED REPORT (GRP 3)Documento9 pagineED REPORT (GRP 3)Shreyas MarudwarNessuna valutazione finora

- High-Performance D/A-Converters: Application to Digital TransceiversDa EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNessuna valutazione finora

- YSUUSYs NiCd Battery RepairDocumento6 pagineYSUUSYs NiCd Battery Repairrwesseldyk50% (2)

- Anatomy 090819Documento30 pagineAnatomy 090819Vaishnavi GourabathiniNessuna valutazione finora

- Grade 4 DLL Quarter 2 Week 2 Sir Bien CruzDocumento47 pagineGrade 4 DLL Quarter 2 Week 2 Sir Bien CruzRonel Fillomena0% (1)

- Teaching TrigonometryDocumento20 pagineTeaching Trigonometryapi-21940065Nessuna valutazione finora

- Rhetorical Analysis ArticleDocumento6 pagineRhetorical Analysis Articleapi-242472728Nessuna valutazione finora

- Socio-cultural influences on educationDocumento4 pagineSocio-cultural influences on educationofelia acostaNessuna valutazione finora

- Alfa Romeo Giulia Range and Quadrifoglio PricelistDocumento15 pagineAlfa Romeo Giulia Range and Quadrifoglio PricelistdanielNessuna valutazione finora

- Financial Services : An OverviewDocumento15 pagineFinancial Services : An OverviewAnirudh JainNessuna valutazione finora

- ComputerDocumento26 pagineComputer29.Kritika SinghNessuna valutazione finora

- Dental System SoftwareDocumento4 pagineDental System SoftwareHahaNessuna valutazione finora

- Measures of CentralityDocumento13 pagineMeasures of CentralityPRAGASM PROGNessuna valutazione finora

- Gregory University Library Assignment on Qualities of a Reader Service LibrarianDocumento7 pagineGregory University Library Assignment on Qualities of a Reader Service LibrarianEnyiogu AbrahamNessuna valutazione finora

- Pmls 1 Final Exam Reviewer: Clinical Chemistry ContDocumento14 paginePmls 1 Final Exam Reviewer: Clinical Chemistry ContPlant in a PotNessuna valutazione finora

- Falling Weight Deflectometer Bowl Parameters As Analysis Tool For Pavement Structural EvaluationsDocumento18 pagineFalling Weight Deflectometer Bowl Parameters As Analysis Tool For Pavement Structural EvaluationsEdisson Eduardo Valencia Gomez100% (1)

- Ubiquiti Af60-Xr DatasheetDocumento3 pagineUbiquiti Af60-Xr Datasheetayman rifaiNessuna valutazione finora

- 4 Exploring Your Personality Q and Scoring Key (Transaction Analysis)Documento3 pagine4 Exploring Your Personality Q and Scoring Key (Transaction Analysis)Tarannum Yogesh DobriyalNessuna valutazione finora

- Active Disturbance Rejection Control For Nonlinear SystemsDocumento8 pagineActive Disturbance Rejection Control For Nonlinear SystemsTrần Việt CườngNessuna valutazione finora

- Math-149 MatricesDocumento26 pagineMath-149 MatricesKurl Vincent GamboaNessuna valutazione finora

- OsmanabadDocumento5 pagineOsmanabadKirankumar MutnaliNessuna valutazione finora