Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Chap4 Field Effect Transistors

Caricato da

Mạnh Cường TrầnDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Chap4 Field Effect Transistors

Caricato da

Mạnh Cường TrầnCopyright:

Formati disponibili

Chap4 - 1 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

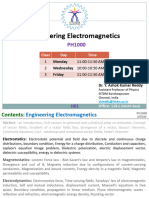

Chapter 4

Field-Effect Transistors

Microelectronic Circuit Design

Richard C. Jaeger

Travis N. Blalock

Chap4 - 2 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Chapter Goals

Describe operation of MOSFETs and JFETs.

Define FET characteristics in operation regions of cutoff, triode and

saturation.

Develop mathematical models for i-v characteristics of MOSFETs and

JFETs.

Introduce graphical representations for output and transfer

characteristic descriptions of electronic devices.

Define and contrast characteristics of enhancement-mode and

depletion-mode FETs.

Define symbols to represent FETs in circuit schematics.

Investigate circuits that bias transistors into different operating regions.

Learn basic structure and mask layout for MOS transistors and circuits.

Explore MOS device scaling

Chap4 - 3 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Chapter Goals (cont.)

Contrast 3 and 4 terminal device behavior.

Describe sources of capacitance in MOSFETs and JFETs.

Explore FET modeling in SPICE.

Chap4 - 4 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Types of Field-Effect Transistors

MOSFET (Metal-Oxide Semiconductor Field-Effect

Transistor)

Primary component in high-density VLSI chips such as

memories and microprocessors

JFET (Junction Field-Effect Transistor)

Finds application especially in analog and RF circuit

design

Chap4 - 5 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Capacitor Structure

First electrode - Gate : Consists of

low-resistivity material such as

highly-doped polycrystalline

silicon, aluminum or tungsten

Second electrode - Substrate or

Body: n- or p-type semiconductor

Dielectric - Silicon dioxide: stable

high-quality electrical insulator

between gate and substrate.

Chap4 - 6 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Substrate Conditions for Different Biases

Accumulation

V

G

<< V

TN

Depletion

V

G

< V

TN

Inversion

V

G

> V

TN

Chap4 - 7 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Low-frequency C-V Characteristics for MOS

Capacitor on P-type Substrate

MOS capacitance is non-

linear function of voltage.

Total capacitance in any

region dictated by the

separation between capacitor

plates.

Total capacitance modeled as

series combination of fixed

oxide capacitance and

voltage-dependent depletion

layer capacitance.

Chap4 - 8 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor: Structure

4 device terminals:

Gate(G), Drain(D),

Source(S) and Body(B).

Source and drain

regions form pn

junctions with substrate.

v

SB

, v

DS

and v

GS

always

positive during normal

operation.

v

SB

must always reverse

bias the pn junctions

Chap4 - 9 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor: Qualitative I-V

Behavior

V

GS

<< V

TN

: Only small leakage

current flows.

V

GS

< V

TN

: Depletion region formed

under gate merges with source and

drain depletion regions. No current

flows between source and drain.

V

GS

> V

TN

: Channel formed between

source and drain. If v

DS

> 0, finite i

D

flows from drain to source.

i

B

= 0 and

i

G

= 0.

Chap4 - 10 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor: Triode Region

Characteristics

=

D

i

i

D

= K

n

'

W

L

v

GS

V

TN

v

DS

2

|

\

|

.

|

|

v

DS

for v

GS

V

TN

> v

DS

> 0

where K

n

= K

n

'

W

L

K

n

'

=

n

C

ox

"

A V

2

| |

C

ox

"

=

c

ox

T

ox

c

ox

= oxide permittivity

F/cm

| |

T

ox

= oxide thickness (cm)

Chap4 - 11 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor: Triode Region

Characteristics (cont.)

Output characteristics

appear to be linear.

FET behaves like a

gate-source voltage-

controlled resistor

between source and

drain with

R

on

=

1

K

n

'

W

L

V

GS

V

TN

|

\

|

.

|

Chap4 - 12 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOSFET as Voltage-Controlled Resistor

Example 1: Voltage-Controlled Attenuator

v

O

v

S

=

R

on

R

on

+R

=

1

1+K

n

RV

GG

V

TN

|

\

|

.

|

v

O

v

S

=

1

1+500

A

V

2

2000O

|

\

|

.

|

1.51

|

\

|

.

| V

=0.667

To maintain triode region operation,

0.667v

S

s(1.51)V or v

S

s0.750 V

v

DS

sv

GS

V

TN

or v

O

sv

GG

V

TN

If K

n

= 500A/V

2

, V

TN

= 1V, R = 2kO and

V

GG

= 1.5V, then,

Chap4 - 13 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOSFET as Voltage-Controlled Resistor

(contd.)

Example 2: Voltage-Controlled High-Pass Filter

Voltage Transfer function,

T s

( )

=

V

O

s

( )

V

S

s

( )

=

s

s+e

o

where, cut-off frequency

e

o

=

1

R

on

C

=

K

n

(V

GS

V

TN

)

C

If K

n

= 500A/V

2

, V

TN

= 1V, C = 0.02F

and V

GG

= 1.5V, then,

f

o

=

500

A

V

2

1.51

|

\

|

.

| V

2t(0.02F)

=1.99 kHz

To maintain triode region operation,

v

S

sV

GG

V

TN

=0.5 V

Chap4 - 14 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor: Saturation Region

If v

DS

increases above triode region limit,

the channel region disappears - also said to

be pinched-off.

Current saturates at a constant value,

independent of v

DS.

Saturation region operation mostly used for

analog amplification.

Chap4 - 15 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor: Saturation Region

(contd.)

i

D

=

K

n

'

2

W

L

v

GS

V

TN

|

\

|

.

|

2

for v

DS

>v

GS

V

TN

v

DSAT

=v

GS

V

TN

is called the saturation or

pinch-off voltage

Chap4 - 16 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Transconductance of a MOS Device

Transconductance relates the change in drain current to a

change in gate-source voltage

Taking the derivative of the expression for the drain

current in the saturation region,

g

m

=

di

D

dv

GS

Q pt

g

m

=K

n

'

W

L

(V

GS

V

TN

)=

2I

D

V

GS

V

TN

Chap4 - 17 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Channel-Length Modulation

As v

DS

increases above

v

DSAT

, the

length of the depleted channel

beyond pinch-off point, AL,

increases and actual L decreases.

i

D

increases slightly with v

DS

instead of being constant.

i

D

=

K

n

'

2

W

L

v

GS

V

TN

|

\

|

.

|

2

1+v

DS

|

\

|

.

|

= channel length modulation

parameter

Chap4 - 18 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Depletion-Mode MOSFETS

NMOS transistors with

Ion implantation process is used to form a built-in n-type

channel in the device to connect source and drain by a

resistive channel

Non-zero drain current for v

GS

= 0; negative v

GS

required to

turn device off.

V

TN

s0

Chap4 - 19 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Transfer Characteristics of MOSFETS

Plots drain current versus gate-source voltage for a fixed

drain-source voltage

Chap4 - 20 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Body Effect or Substrate Sensitivity

Non-zero v

SB

changes threshold

voltage, causing substrate

sensitivity modeled by

where

V

TO

= zero substrate bias for V

TN

(V)

= body-effect parameter ( )

2u

F

= surface potential parameter (V)

V

TN

=V

TO

+ v

SB

+2|

F

2|

F

|

\

|

.

|

V

Chap4 - 21 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Enhancement-Mode PMOS Transistors:

Structure

p-type source and drain regions

in n-type substrate.

v

GS

< 0 required to create p-type

inversion layer in channel

region

For current flow, v

GS

< v

TP

To maintain reverse bias on

source-substrate and drain-

substrate junctions, v

SB

< 0 and

v

DB

< 0

Positive bulk-source potential

causes V

TP

to become more

negative

Chap4 - 22 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Enhancement-Mode PMOS Transistors:

Output Characteristics

For , transistor is

off.

For more negative v

GS

, drain

current increases in

magnitude.

PMOS is in triode region for

small values of V

DS

and in

saturation for larger values.

V

GS

>V

TP

Chap4 - 23 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOSFET Circuit Symbols

(g) and (i) are the

most commonly

used symbols in

VLSI logic design.

MOS devices are

symmetric.

In NMOS, n

+

region at higher

voltage is the drain.

In PMOS p

+

region

at lower voltage is

the drain

Chap4 - 24 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Process-defining Factors

Minimum Feature Size F : Width of smallest line or space that can

be reliably transferred to wafer surface using a given generation of

lithographic manufacturing tools

Alignment Tolerance T: Maximum misalignment that can occur

between two mask levels during fabrication

Chap4 - 25 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Mask Sequence for a Polysilicon-Gate

Transistor

Mask 1: Defines active area or

thin oxide region of transistor

Mask 2: Defines polysilicon gate

of transistor, aligns to mask 1

Mask 3: Delineates the contact

window, aligns to mask 2.

Mask 4: Delineates the metal

pattern, aligns to mask 3.

Channel region of transistor

formed by intersection of first

two mask layers. Source and

Drain regions formed wherever

mask 1 is not covered by mask 2

n

+

n

+

n

+

n

+

n

+

n

+

(a) (b)

(c)

(d)

Chap4 - 26 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Basic Ground Rules for Layout

F = 2A

T = F/2 = A

A could be 1, 0.5,

0.25 m, etc.

Polysilicon Gate

Aluminum

Interconnection

Contact

Active Region

Oxide

Metal

n

+

2 A 2 A 2 A 1 A 1 A

12 A

A

A

A

2A

A

10 A

B

B'

W

L

Polysilicon Below

Metal

n

+

Oxide

Metal

n

+

Chap4 - 27 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Internal Capacitances in Electronic

Devices

Limit high-frequency performance of the electronic device

Limit switching speed of circuits in logic applications

Limit frequency at which useful amplification can be

obtained in amplifiers.

MOSFET capacitances depend on operation region and are

non-linear functions of voltages at device terminals.

Chap4 - 28 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor Capacitances: Triode

Region

C

ox

= Gate-channel

capacitance per unit

area(F/m

2

).

C

GC

= Total gate channel

capacitance.

C

GS

= Gate-source

capacitance.

C

GD

= Gate-drain

capacitance.

C

GSO

and C

GDO

= overlap

capacitances (F/m).

C

GS

=

C

GC

2

+C

GSO

W=C

ox

"

WL

2

+C

GSO

W

C

GD

=

C

GC

2

+C

GSO

W=C

ox

"

WL

2

+C

GSO

W

Chap4 - 29 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor Capacitances: Triode

Region (cont.)

C

SB

= Source-bulk capacitance.

C

DB

= Drain-bulk capacitance.

A

S

and A

D

= junction bottom area

capacitance of the source and

drain regions.

P

S

and P

D

= perimeter of the

source and drain junction

regions.

C

SB

=C

J

A

S

+C

JSW

P

S

C

DB

=C

J

A

D

+C

JSW

P

D

Chap4 - 30 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor Capacitances:

Saturation Region

Drain no longer connected to channel

C

GS

=

2

3

C

GC

+C

GSO

W

C

GD

=C

GDO

W

Chap4 - 31 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Transistor Capacitances: Cutoff

Region

Conducting channel

region completely

gone.

C

GB

= Gate-bulk

capacitance

C

GBO

= gate-bulk

capacitance per unit

width.

C

GS

=C

GSO

W

C

GD

=C

GDO

W

C

GB

=C

GBO

W

Chap4 - 32 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

SPICE Model for NMOS Transistor

Typical default values used by SPICE:

K

n

or K

p

: KP = 20 A/V

2

: GAMMA= 0 : LAMBDA = 0

V

TO

= 1 V or V

TO

= -1 V

n

or

p

UO = 600 cm

2

/V-s

2u

F

: PHI = 0.6 V

C

GDO

= C

GSO

= C

GBO

= C

JSW

= 0

T

ox

: TOX = 100 nm

Chap4 - 33 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis Approach

Assume a region of operation (generally the saturation

region)

Use circuit analysis to find V

GS

Use V

GS

to calculate I

D

, and I

D

to find V

DS

Check validity of operation region assumptions

Change assumptions and analyze again if required.

NOTE: An enhancement-mode device with V

DS

= V

GS

is

always in saturation

Chap4 - 34 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Four-Resistor and Two-Resistor Biasing

Provide excellent bias for transistors in discrete circuits.

Stabilize bias point with respect to device parameter and

temperature variations using negative feedback.

Use single voltage source to supply both gate-bias voltage

and drain current.

Generally used to bias transistors in saturation region.

Two-resistor biasing uses fewer components than four-

resistor biasing

Chap4 - 35 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis: Example 1

(Four-Resistor Biasing)

Problem: Find Q-pt (I

D

, V

DS

)

Approach: Assume operating

region, find Q-point, check to see if

result is consistent with operation

region

Assumption: Transistor is saturated, I

G

= I

B

= 0

Analysis: First, simplify circuit, split

V

DD

into two equal-valued sources and

apply Thvenin transformation to find

V

EQ

and R

EQ

for gate-bias voltage

Chap4 - 36 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis: Example 1

(Four-Resistor Biasing - cont.)

V

EQ

=V

GS

+I

D

R

S

Since I

G

= 0,

V

EQ

=V

GS

+

K

n

R

S

2

V

GS

V

TN

|

\

|

.

|

2

4=V

GS

+

2510

6

|

\

|

.

|

|

3.910

4

|

\

|

.

|

|

2

V

GS

1

|

\

|

.

|

2

V

GS

2

+0.05V

GS

7.21=0

V

GS

=2.71V,+2.66V

Since V

GS

< V

TN

for V

GS

= -2.71 V

and MOSFET will be cut-off,

V

GS

=+2.66 V and I

D

= 34.4 A

Also, V

DD

= I

D

(R

D

+R

S

)+V

DS

and V

DS

=6.08 V

V

DS

> V

GS

-V

TN

. Hence

saturation region assumption is

correct.

Q-pt: (34.4 A, 6.08 V) with

V

GS

= 2.66 V

Chap4 - 37 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis: Example 2

(Four-Resistor Biasing)

Estimate value of I

D

and use it

to find V

GS

and V

SB

Use V

SB

to calculate V

TN

Find I

D

using above 2 steps

If I

D

is not same as original I

D

estimate, start again.

Analysis with body effect using

same assumptions as in example 1:

V

GS

=V

EQ

I

D

R

S

=622000I

D

V

SB

=I

D

R

S

=22000I

D

V

TN

=V

TO

+( V

SB

+2|

F

2|

F

)

V

TN

=1+0.5( V

SB

+0.6 0.6)

I

D

'=

2510

6

|

\

|

.

|

2

V

GS

V

TN

|

\

|

.

|

2

Iterative solution can be found by

following steps:

Chap4 - 38 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis: Example 2

(Four-Resistor Biasing - cont.)

The iteration sequence leads to I

D

= 88.0 A

V

DS

=V

DD

I

D

(R

D

+R

S

)=1040000I

D

=6.48V

V

DS

>V

GS

-V

TN

. Hence saturation region assumption is correct.

Q-pt: (88.0 A, 6.48 V)

Chap4 - 39 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis: Example 3

(Two-Resistor Biasing)

Assumption: I

G

= I

B

= 0, transistor is

saturated (since V

DS

=V

GS

)

Analysis:

V

DS

=V

DD

I

D

R

D

V

GS

=V

DD

K

n

R

D

2

V

GS

V

TN

|

\

|

.

|

2

V

GS

= 3.3

2.610

4

|

\

|

.

|

10

4

|

\

|

.

|

2

V

GS

1

|

\

|

.

|

2

V

GS

=0.769V, +2.00V

Since V

GS

<V

TN

for V

GS

= -0.769 V

and the MOSFET will be cut-off,

V

DS

>V

GS

-V

TN

. Hence saturation

region assumption is correct.

Q-pt: (130 A, 2.00 V)

V

GS

= 2.00 V and I

D

=130 A

Chap4 - 40 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis: Example 4 ( Biasing in

Triode Region)

Assumption: I

G

= I

B

= 0, transistor

is saturated (since V

DS

= V

GS

)

Analysis: V

GS

= V

DD

= 4 V

I

D

=

250

2

A

V

2

(41)

2

=1.13mA

V

DD

= I

D

(R

D

+R

S

)+V

DS

4=1600I

D

+V

DS

V

DS

=2.19 V

Also

But V

DS

< V

GS

-V

TN

. Hence,

saturation region assumption is

incorrect. Try again using the triode

region equation:

4V

DS

=1600

250

2

A

V

2

(41

V

DS

2

)V

DS

V

DS

=2.3 V and I

D

=1.06 mA

V

DS

<V

GS

-V

TN

, transistor is in triode

region

Q-pt: (1.06 mA, 2.3 V)

Chap4 - 41 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Bias Analysis: Example 5 (Two-Resistor

biasing for PMOS Transistor)

Assumption: I

G

= I

B

= 0, transistor

is saturated (since V

DS

=

V

GS

)

Analysis:

V

GS

+(470kO)I

G

+V

DS

=0

Also

15V(220kO)I

D

+V

DS

=0

15V(220kO)

50

2

A

V

2

V

GS

+2

|

\

|

.

|

2

+V

GS

=0

V

GS

=0.369V, 3.45V

Since V

GS

= -0.369 V is less than V

TP

= -2V,

V

GS

= -3.45 V

I

D

= 52.5 A and V

GS

= -3.45 V

Hence saturation assumption is correct.

Q-pt: (52.5 A, -3.45 V)

V

DS

> V

GS

V

TP

Chap4 - 42 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOSFET as a Current Source

Ideal current source

gives fixed output

current regardless of

voltage across it.

MOSFET behaves as as

an ideal current source if

biased in the pinch-off

region (output current

depends on gate-source

terminal voltage).

Chap4 - 43 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Current Mirror

Assumption: M

1

and M

2

have identical V

TN

, K

n

,

and W/L and are in

saturation.

I

REF

=

K

n

2

W

L

V

GS1

V

TN

( )

2

1+V

DS1

|

\

|

.

|

I

O

=

K

n

2

W

L

V

GS2

V

TN

( )

2

1+V

DS2

|

\

|

.

|

But V

GS2

=V

GS1

and

I

O

= I

REF

1+V

DS2

( )

1+V

DS1

( )

~ I

REF

Thus, the output current precisely

mirrors the reference current if

V

DS1

= V

DS2

.

Chap4 - 44 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Current Mirror: Example

Given data: I

REF

= 50 A, V

O

= 12 V, V

TN

= 1 V, K

n

= 150 A/V

2

, =

0.0133 V

-1

Determine: V

GS

, V

DS1

, I

O

Analysis:

V

DS1

=V

GS1

=V

TN

+

2I

REF

K

n

(1+V

DS1

)

Using trial-and-error,

V

DS1

=1V+

2(50A)

150

A

V

2

(1+

0.0133

V

V

DS1

)

Hence, V

DS1

= 1.81 V. Also, V

DS2

= 12 V

I

O

=(50A)

1+

0.0133

V

(12V)

|

\

|

.

|

|

1+

0.0133

V

(1.81V)

|

\

|

.

|

|

=56.6 A

Chap4 - 45 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Current Mirror Ratio

K

n1

= K

n

'

W

L

|

\

|

.

|

|

1

=2K

n

'

K

n2

= K

n

'

W

L

|

\

|

.

|

|

2

=10K

n

'

I

O

= I

REF

W/L

( )

2

W/L

( )

1

1+V

DS2

( )

1+V

DS1

( )

=5I

REF

1+V

DS2

( )

1+V

DS1

( )

I

O

~5I

REF

Thus, the ratio between I

O

and I

REF

can be modified by changing the

W/L ratios of the current mirror

transistors (ignoring differences due

to V

DS

mismatch)

Chap4 - 46 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Current Mirror Output Resistance

Output current changes with v

DS

due to channel length

modulation.

Output resistance is given by

In the current mirror, v

O

= v

DS2

R

o

=

ci

O

cv

O

Q pt

|

\

|

.

|

|

|

1

i

O

=

K

n

2

W

L

v

GS2

V

TN

|

\

|

.

|

2

1+v

O

|

\

|

.

|

R

o

=

I

O

1+I

O

|

\

|

.

|

|

|

|

1

=

1+I

O

I

O

~

1

I

O

Chap4 - 47 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Current Mirror Layout

Two possible layouts

for a current mirror

Chap4 - 48 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Design of Multiple Current Mirrors:

Example

I

D2

= I

REF

W/L

( )

2

W/L

( )

1

=50 A

I

D3

= I

REF

W/L

( )

3

W/L

( )

1

=125 A

I

D5

= I

REF

W/L

( )

5

W/L

( )

4

=25 A

Choose R to set I

REF

= 25 A

R=

10+V

GSP

V

GSN

I

REF

Chap4 - 49 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Design of Multiple Current Mirrors

(cont).

R=

101.71+1.45

25

V

A

=274kO

V

GSP

=V

TP

2I

D

K

p

=1.71V and V

GSN

=V

TN

+

2I

D

K

n

=1.45V

R can be replaced by transistor M

6

for better

integration. We know that V

GS6

= -6.84 V and I

D

= 25 A and M

6

is in saturation

I

D

=

K

p

'

2

W

L

|

\

|

.

|

|

V

GS

V

TP

( )

2

and

W

L

|

\

|

.

|

|

=

1

13.6

Chap4 - 50 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling

Drain Current:

Gate Capacitance and Circuit Delay:

where t is the circuit delay in a logic circuit.

K

n

*

=

n

c

ox

T

ox

/o

|

\

|

.

|

|

|

|

W/o

L/o

|

\

|

.

|

|

=o

n

c

ox

T

ox

|

\

|

.

|

|

|

|

W

L

|

\

|

.

|

|

=oK

n

i

D

*

=

n

c

ox

T

ox

/o

|

\

|

.

|

|

|

|

W/o

L/o

|

\

|

.

|

|

=

v

GS

o

v

TN

o

v

DS

2o

|

\

|

.

|

|

v

DS

o

=

i

D

o

C

GC

*

=(C

ox

"

)

*

W

*

L

*

=

c

ox

T

ox

/o

|

\

|

.

|

|

|

|

W/o

L/o

|

\

|

.

|

|

=

C

GC

o

t

*

=C

GC

*

AV

*

i

D

*

=

C

GC

o

AV/o

i

D

/o

|

\

|

.

|

|

|

|

=

t

o

Chap4 - 51 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling (cont.)

Circuit and Power Densities:

Power-Delay Product:

Cutoff Frequency:

f

T

improves with square of channel length reduction

P

*

=V

DD

*

i

D

*

=

V

DD

o

i

D

o

|

\

|

.

|

|

|

=

P

o

2

P

*

A

*

=

P

*

W

*

L

*

=

P/o

2

(W/o)(L/o)

=

P

WL

=

P

A

PDP

*

=P

*

t

*

=

P

o

2

t

o

|

\

|

.

|

|

=

PDP

o

3

f

T

=

1

2t

g

m

C

GC

=

1

2t

n

L

2

V

GS

V

TN

|

\

|

.

|

Chap4 - 52 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling (cont.)

High Field Limitations:

High electric fields arise if technology is scaled down

with supply voltage constant.

Cause reduction in mobility of the MOS transistors,

breakdown of the linear relationship between mobility

and electric field, and carrier velocity saturation.

Ultimately results in reduced long-term reliability and

breakdown of gate oxide or pn junction.

Drain current in saturation region is linearized to

i

D

=

C

ox

"

W

2

(v

GS

v

TN

)v

SAT

where, v

SAT

is the carrier

saturation velocity

Chap4 - 53 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling (cont.)

Sub-threshold Conduction:

I

D

decreases exponentially for

V

GS

< V

TN.

Reciprocal of the slope in

mV/decade gives the turn off

rate for the MOSFET.

V

TN

should be reduced if

dimensions are scaled down,

but curve in sub-threshold

region shifts horizontally

instead of scaling with V

TN

.

Chap4 - 54 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Junction Field-Effect Transistor (JFET)

Structure

Much lower input current and

much higher input impedance than

the BJT.

In triode region, JFET is a voltage-

controlled resistor,

= resistivity of channel

L = channel length

W = channel width between pn

junction depletion regions

t = channel depth

Inherently a depletion-mode device

n-type semiconductor block

houses the channel region in n-

channel JFET.

Two pn junctions form the gate.

Current enters channel at the drain

and exits at source.

R

CH

=

t

L

W

Chap4 - 55 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET with Gate-Source Bias

v

GS

= 0, gate isolated from channel.

V

P

< v

GS

<0, W < W, and channel

resistance increases; gate-source

junction is reverse-biased, i

G

almost 0.

v

GS

= V

P

< 0, channel region pinched-

off, channel resistance is infinite.

Chap4 - 56 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET Channel with Drain-Source Bias

With constant v

GS

, depletion region

near drain increases with v

DS

.

At v

DSP

= v

GS

- V

P

, channel is totally

pinched-off; i

D

is saturated.

JFET also suffers from channel-

length modulation like MOSFET at

larger values of v

DS

.

Chap4 - 57 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

N-Channel JFET

i-v Characteristics

Transfer Characteristics

Output Characteristics

Chap4 - 58 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

N-Channel JFET

i-v Characteristics (cont.)

For all regions :

In cutoff region:

In Triode region:

In pinch-off region:

i

G

=0 for v

GS

s0

i

D

=0 for v

GS

sV

P

V

P

<0

|

\

|

.

|

i

D

=

2I

DSS

V

P

2

v

GS

V

P

v

DS

2

|

\

|

.

|

|

2

v

DS

for v

GS

>V

P

and v

GS

V

P

>V

DS

>0

i

D

=I

DSS

1

v

GS

V

P

|

\

|

.

|

|

|

|

2

1+v

DS

|

\

|

.

| for v

DS

>v

GS

V

P

>0

Chap4 - 59 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

P-Channel JFET

Polarities of n- and p-type regions of the n-channel

JFET are reversed to get the p-channel JFET.

Channel current direction and operating bias voltages

are also reversed.

Chap4 - 60 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET Circuit Symbols

JFET structures are symmetric like MOSFETs.

Source and drain determined by circuit voltages.

Chap4 - 61 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET Capacitances and SPICE Modeling

C

GD

and C

GS

are determined by depletion-

layer capacitances of reverse-biased pn

junctions forming gate and are bias

dependent.

Typical default values used by SPICE:

V

p

= -2 V

= C

GD

= C

GD

= 0

Transconductance parameter BETA

BETA = I

DSS

/V

P

2

= 100 A/V

2

Chap4 - 62 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Biasing JFET and Depletion-Mode

MOSFET: Example

Assumptions: JFET is pinched-off, gate-channel junction is reverse-biased,

reverse leakage current of gate, I

G

= 0

N-channel JFET Depletion-mode MOSFET

Chap4 - 63 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Biasing JFET and Depletion-Mode

MOSFET: Example (cont.)

Analysis:

Since I

S

=I

D

, V

GS

=I

D

R

S

V

GS

=I

DSS

R

S

1

V

GS

V

P

|

\

|

.

|

|

|

2

= 510

3

A

|

\

|

.

|

1000O

( )

1

V

GS

5V

|

\

|

.

|

|

2

V

GS

=1.91V, 13.1V

Since V

GS

= -13.1 V is less than V

P

= -5 V, V

GS

= -1.91 V and, I

D

= I

S

=

1.91 mA. Also,

V

DS

=V

DD

I

D

(R

D

+R

S

)=12(1.91mA)(3kO)=6.27V

V

DS

>V

GS

-V

P

. Hence pinch-off region assumption is correct and gate-

source junction is reverse-biased by 1.91V.

Q-pt: (1.91 mA, 6.27 V)

Chap4 - 64 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

End of Chapter 4

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Lecture7 (20 3 11)Documento4 pagineLecture7 (20 3 11)Mạnh Cường TrầnNessuna valutazione finora

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Lecture23 (20 3 11)Documento4 pagineLecture23 (20 3 11)Mạnh Cường TrầnNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Devices and Circuits Ii: Lecture GoalsDocumento6 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Lecture5 (20 3 11)Documento6 pagineLecture5 (20 3 11)Mạnh Cường TrầnNessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Lecture2-Introduction To Electronics (20!3!11)Documento6 pagineLecture2-Introduction To Electronics (20!3!11)Mạnh Cường TrầnNessuna valutazione finora

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devices and Circuits Ii: Lecture GoalsDocumento5 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Devices and Circuits Ii: I-V Characteristics of Bipolar TransistorDocumento4 pagineDevices and Circuits Ii: I-V Characteristics of Bipolar TransistorMạnh Cường TrầnNessuna valutazione finora

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Lecture3 (20 3 11)Documento5 pagineLecture3 (20 3 11)Mạnh Cường TrầnNessuna valutazione finora

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Devices and Circuits Ii: Lecture GoalsDocumento4 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- Devices and Circuits Ii: Lecture GoalsDocumento4 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- Devices and Circuits Ii: Lecture GoalsDocumento4 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Devices and Circuits Ii: Lecture GoalsDocumento4 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Devices and Circuits Ii: Coupling & Bypass Capacitor DesignDocumento5 pagineDevices and Circuits Ii: Coupling & Bypass Capacitor DesignMạnh Cường TrầnNessuna valutazione finora

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Devices and Circuits Ii: Lecture GoalsDocumento4 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (3) (CB Amplifier)Documento4 pagineEE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (3) (CB Amplifier)Mạnh Cường TrầnNessuna valutazione finora

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (2) (CE Amplifier)Documento5 pagineEE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (2) (CE Amplifier)Mạnh Cường TrầnNessuna valutazione finora

- Lecture Goals: EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (5) (CS Amplifier)Documento3 pagineLecture Goals: EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (5) (CS Amplifier)Mạnh Cường TrầnNessuna valutazione finora

- Lecture Goals: EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (7) (CD Amplifier)Documento4 pagineLecture Goals: EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (7) (CD Amplifier)Mạnh Cường TrầnNessuna valutazione finora

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Lecture Goals: EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (6) (CG Amplifier)Documento3 pagineLecture Goals: EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (6) (CG Amplifier)Mạnh Cường TrầnNessuna valutazione finora

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- EE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (4) (CC Amplifier)Documento4 pagineEE 332 Devices and Circuits Ii Small-Signal Models and Single Transistor Amplifier (4) (CC Amplifier)Mạnh Cường TrầnNessuna valutazione finora

- Chap18-Feedback, Stability and OscillatorsDocumento58 pagineChap18-Feedback, Stability and OscillatorsMạnh Cường TrầnNessuna valutazione finora

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Devices and Circuits Ii: Lecture GoalsDocumento3 pagineDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNessuna valutazione finora

- Devices and Circuits Ii: Small Signal Parameters of MOSFETDocumento5 pagineDevices and Circuits Ii: Small Signal Parameters of MOSFETMạnh Cường TrầnNessuna valutazione finora

- Chap17 Frequency ResponseDocumento61 pagineChap17 Frequency ResponseMạnh Cường TrầnNessuna valutazione finora

- Chap14 Single Transistors AmplifiersDocumento59 pagineChap14 Single Transistors AmplifiersMạnh Cường TrầnNessuna valutazione finora

- Lecture1-Introduction To Electronics (20!3!11)Documento7 pagineLecture1-Introduction To Electronics (20!3!11)Mạnh Cường TrầnNessuna valutazione finora

- Chap15 Multistage AmplifiersDocumento70 pagineChap15 Multistage AmplifiersMạnh Cường TrầnNessuna valutazione finora

- Chap16-Analog Integrated CircuitsDocumento55 pagineChap16-Analog Integrated CircuitsMạnh Cường TrầnNessuna valutazione finora

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Chap13-Small-Signal Modeling and Linear AmplificationDocumento47 pagineChap13-Small-Signal Modeling and Linear AmplificationMạnh Cường TrầnNessuna valutazione finora

- Chap12-Operational Amplifier ApplicationsDocumento54 pagineChap12-Operational Amplifier ApplicationsMạnh Cường Trần100% (1)

- HV-EHV Cables Synthetic IsolationDocumento16 pagineHV-EHV Cables Synthetic IsolationA. HassanNessuna valutazione finora

- Lecture 28Documento15 pagineLecture 28KumarNessuna valutazione finora

- Digital Electronics ProjectDocumento13 pagineDigital Electronics ProjectET201040 Mohin UddinNessuna valutazione finora

- Dvor 432Documento234 pagineDvor 432Joshua CarrionNessuna valutazione finora

- Tesla'S Big Mistake?: William BeatyDocumento9 pagineTesla'S Big Mistake?: William BeatySunny ThomasNessuna valutazione finora

- Alstom Grid - Bushings - PNO LIGHT - UK - WEB PDFDocumento8 pagineAlstom Grid - Bushings - PNO LIGHT - UK - WEB PDFjtcool74Nessuna valutazione finora

- Panasonic Sa-Ak980pu SM PDFDocumento143 paginePanasonic Sa-Ak980pu SM PDFpolloNessuna valutazione finora

- This Project Is Available On 3 Different PC Boards:: Diesel Sound 3 - Called Diesel Sound 4 WattDocumento11 pagineThis Project Is Available On 3 Different PC Boards:: Diesel Sound 3 - Called Diesel Sound 4 WattΔημητριος ΣταθηςNessuna valutazione finora

- lmp91000 PDFDocumento31 paginelmp91000 PDFJoão CostaNessuna valutazione finora

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Gamma Ray InteractionDocumento12 pagineGamma Ray Interactionaungwinnaing100% (1)

- Motion and Recombination of Electrons and HolesDocumento24 pagineMotion and Recombination of Electrons and HolesFlor EsperanzaNessuna valutazione finora

- Electrical Estimator ManualDocumento48 pagineElectrical Estimator Manualjanmczeal100% (3)

- Transmitter of (3D-CAR) ROHINI/ REVATHI RadarDocumento28 pagineTransmitter of (3D-CAR) ROHINI/ REVATHI RadarUtkarsh Tyagi UTNessuna valutazione finora

- 520SL SLB Guide en USDocumento2 pagine520SL SLB Guide en USBruce CanvasNessuna valutazione finora

- 22 MM Installation Instructions For The M701E Output Module: Rotate Ruotare Girar Drehen Plug Inserire Conectar EinhakenDocumento4 pagine22 MM Installation Instructions For The M701E Output Module: Rotate Ruotare Girar Drehen Plug Inserire Conectar EinhakenRicardo Jose Cerdá AliagaNessuna valutazione finora

- NTE30180 Series LED, 3W, High Power 20mm X 20mm Star Base Aluminum PCBDocumento2 pagineNTE30180 Series LED, 3W, High Power 20mm X 20mm Star Base Aluminum PCBjulio quatriniNessuna valutazione finora

- JBL 2600Documento7 pagineJBL 2600oscaralvear67Nessuna valutazione finora

- Types of Luminous FixturesDocumento11 pagineTypes of Luminous Fixtures622 MANSI TANJILANessuna valutazione finora

- Allied PhysicsDocumento9 pagineAllied PhysicsJostin Punnassery50% (4)

- As501 YahamaDocumento91 pagineAs501 YahamaRaju NayagamNessuna valutazione finora

- PM11S3 0713Documento2 paginePM11S3 0713Alberto CastilloNessuna valutazione finora

- PFC Katalog 2009Documento88 paginePFC Katalog 2009jasperkenNessuna valutazione finora

- g3 GasDocumento2 pagineg3 GasiceschelNessuna valutazione finora

- PHYSICS 12th PAPER SEPTEMBER 2023Documento6 paginePHYSICS 12th PAPER SEPTEMBER 2023mehakNessuna valutazione finora

- M II - Electrostatics Class Material@Part IDocumento70 pagineM II - Electrostatics Class Material@Part ISurendar VijayNessuna valutazione finora

- Engineering Physics Laser NotesDocumento113 pagineEngineering Physics Laser NotesKd kumarNessuna valutazione finora

- S - 2.a Measurement of Distance, Angles, BearingsDocumento13 pagineS - 2.a Measurement of Distance, Angles, BearingsqetNessuna valutazione finora

- Humara Nam Ravi HaiDocumento8 pagineHumara Nam Ravi HaiRavi ShankarNessuna valutazione finora

- TPK-2W The TPK Series Are Miniature, Isolated 2W DC/DC Converters in A SIP Package.Documento3 pagineTPK-2W The TPK Series Are Miniature, Isolated 2W DC/DC Converters in A SIP Package.toppowerNessuna valutazione finora

- Thierry Van Cutsem, Costas Vournas Voltage StabilityDocumento375 pagineThierry Van Cutsem, Costas Vournas Voltage StabilityMani KandanNessuna valutazione finora