Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Dmacontroller8257 Satru

Caricato da

Satrughna KumarDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Dmacontroller8257 Satru

Caricato da

Satrughna KumarCopyright:

Formati disponibili

DMA CONTROLLER 8257

Features:

It is a 4-channel DMA. So 4 I/O devices can be interfaced to DMA It is designed by Intel Each channel have 16-bit address and 14 bit counter It provides chip priority resolver that resolves priority of channels in fixed or rotating mode. It provide on chip channel inhibit logic.

It

generates a TC signal to indicate the peripheral that the programmed number of data bytes have been transferred. It generates MARK signal to indicate the peripheral that 128 bytes have been transferred. It requires single phase clock. The maximum frequency is 3Mhz and minimum frequency is 250 Hz.

It

execute 3 DMA cycles 1.DMA read 2.DMA write 3.DMA verify. It provide AEN signal that can be used to isolate CPU and other devices from the system bus. It is operate in two modes. 1.Master Mode 2.Slave Mode

Pin Diagram of DMA controller

Description of pin diagram

D0-D7: it is a bidirectional ,tri state ,Buffered ,Multiplexed data (D0-D7)and (A8-A15). In the slave mode it is a bidirectional (Data is moving). In the Master mode it is a unidirectional (Address is moving).

IOR: It is active low ,tristate ,buffered ,Bidirectional lines. In the slave mode it function as a input line. IOR signal is generated by microprocessor to read the contents 8257 registers. In the master mode it function as a output line. IOR signal is generated by 8257 during write cycle

IOW: It is active low ,tristate ,buffered ,Bidirectional control lines. In the slave mode it function as a input line. IOR signal is generated by microprocessor to write the contents 8257 registers. In the master mode it function as a output line. IOR signal is generated by 8257 during read cycle

CLK: It is the input line ,connected with TTL clock generator. This signal is ignored in slave mode. RESET: Used to clear mode set registers and status registers A0-A3: These are the tristate, buffer, bidirectional address lines. In slave mode ,these lines are used as address inputs lines and internally decoded to access the internal registers. In master mode, these lines are used as address outputs lines,A0-A3 bits of memory address on the lines.

CS: It is active low, Chip select input line. In the slave mode, it is used to select the chip. In the master mode, it is ignored. A4-A7: These are the tristate, buffer, output address lines. In slave mode ,these lines are used as address outputs lines. In master mode, these lines are used as address outputs lines,A0-A3 bits of memory address on the lines.

READY: It is a asynchronous input line. In master mode, When ready is high it is received the signal. When ready is low, it adds wait state between S1 and S3 In slave mode ,this signal is ignored. HRQ: It is used to receiving the hold request signal from the output device.

HLDA: It is acknowledgment signal from microprocessor. MEMR: It is active low ,tristate ,Buffered control output line. In slave mode, it is tristated. In master mode ,it activated during DMA read cycle. MEMW: It is active low ,tristate ,Buffered control input line. In slave mode, it is tristated. In master mode ,it activated during DMA write cycle.

AEN (Address enable): It is a control output line. In master mode ,it is high In slave mode ,it is low Used it isolate the system address ,data ,and control lines. ADSTB: (Address Strobe) It is a control output line. Used to split data and address line. It is working in master mode only. In slave mode it is ignore.

TC (Terminal Count): It is a status of output line. It is activated in master mode only. It is high ,it selected the peripheral. It is low ,it free and looking for a new peripheral. MARK: It is a modulo 128 MARK output line. It is activated in master mode only. It goes high ,after transferring every 128 bytes of data block.

DRQ0-DRQ3(DMA Request): These are the asynchronous peripheral request input signal. The request signals is generated by external peripheral device. DACK0-DACK3: These are the active low DMA acknowledge output lines. Low level indicate that ,peripheral is selected for giving the information (DMA cycle). In master mode it is used for chip select.

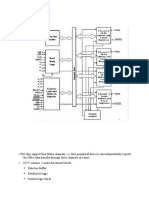

8257 BLOCK DIAGRAM

Description

1.

2. 3. 4. 5.

It containing Five main Blocks. Data bus buffer Read/Control logic Control logic block Priority resolver DMA channels.

DATA BUS BUFFER: It contain tristate ,8 bit bi-directional buffer. Slave mode ,it transfer data between microprocessor and internal data bus. Master mode ,the outputs A8-A15 bits of memory address on data lines (Unidirectional). READ/CONTROL LOGIC: It control all internal Read/Write operation. Slave mode ,it accepts address bits and control signal from microprocessor. Master mode ,it generate address bits and control signal.

Control logic block: It contains , 1. Control logic 2. Mode set register and 3. Status Register. CONTROL LOGIC: Master mode ,It control the sequence of DMA operation during all DMA cycles. It generates address and control signals. It increments 16 bit address and decrement 14 bit counter registers. It activate a HRQ signal on DMA channel Request. Slave ,mode it is disabled.

MODE SET REGISTERS: It is a write only registers. It is used to set the operating modes. This registers is programmed after initialization of DMA channel.

D7 AL

D6

D5

D4

D3

D2 D1

D0

TCS EW RP

EN3 EN2 EN1 EN0

AL=1=Auto load mode AL=0=Rotating mode

TCS=1=Stop after TC (Disable Channel) TCS=0=Start after TC (Enable Channel) EW=1=Extended write mode EW=0=normal mode.

RP=1=Rotating priority RP=0=Fixed priority.

EN3=1=Enable DMA CH-3 EN3=0=Disable DMA CH-3

EN2=1=Enable DMA CH-2 EN2=0=Disable DMA CH-2

EN1=1=Enable DMA CH-1 EN1=0=Disable DMA CH-1 EN0=1=Enable DMA CH-0 EN0=0=Disable DMA CH-0

STATUS REGISTERS: It is read only registers. It is tell the status of DMA channels TC status bits are set when TC signal is activated for that channel. Update flag is not affected during read operation. The UP bit is set during update cycle . It is cleared after completion of update cycle. D7 0 D6 0 D5 0 D4 UP D3 D2 D1 D0

TC3 TC2 TC1 TCO

UP=Update flag UP=1=8257 executing update cycle UP=0=8257 executing DMA cycle

TC3=1=TC activated CH-3 TC3=0=TC activated CH-3 TC2=1=TC activated CH-2 TC2=0=TC activated CH-2

TC1=1=TC activated CH-1 TC1=0=TC activated CH-1 TC0=1=TC activated CH-0 TC0=0=TC activated CH-0 The address of status register is A3A2A1A0=1000.

FIRST/LAST FLIP FLOP: 8257 have 8bit data line and 16 bit address line. 8085 it is getting 8-bit data in simultaneously. 8085 can not access 16-bit address in simultaneously.

A0-A3 lines are used to distinguish between registers ,but they are not distinguish lower and higher address. It is reset by external RESET signal. It is also reset by whenever mode set register is loaded. So program initialization with a dummy (00 H). FF=1=Higher byte of address FF=0=Lower byte of address.

Modes of Operation

Rotating priority Mode: The priority of the channels has a circular sequence. Fixed Priority Rotating Mode: The priority is fixed. TC Stop Mode Auto Load mode Extended Write mode

Potrebbero piacerti anche

- Dma Controller 8257Documento27 pagineDma Controller 8257Rathore Yuvraj SinghNessuna valutazione finora

- Dmacontroller 8257Documento27 pagineDmacontroller 8257satyanarayana12Nessuna valutazione finora

- Dma Controller 8257Documento35 pagineDma Controller 8257balakasriram123Nessuna valutazione finora

- Dma Controller 8257Documento27 pagineDma Controller 8257aj3120Nessuna valutazione finora

- Dma Controller 8257Documento28 pagineDma Controller 8257mnshraoNessuna valutazione finora

- Dma ControllerDocumento28 pagineDma ControllerVEL TECHNessuna valutazione finora

- Dma 8257Documento27 pagineDma 8257Rahul RajanNessuna valutazione finora

- Mic Unit1Documento21 pagineMic Unit1xboyxman1000Nessuna valutazione finora

- 8257 DmaDocumento6 pagine8257 DmaAdarsh AmzeNessuna valutazione finora

- 8257 - Microprocessors and Microcontrollers NotesDocumento25 pagine8257 - Microprocessors and Microcontrollers NotesFathima HeeraNessuna valutazione finora

- Pin Diagram of 8086Documento21 paginePin Diagram of 8086Radha SudheeraNessuna valutazione finora

- Unit 2 8086 System Bus Structures FullunitDocumento36 pagineUnit 2 8086 System Bus Structures Fullunitlauro eugin brittoNessuna valutazione finora

- Microprocessor 8088Documento11 pagineMicroprocessor 8088bobby khanNessuna valutazione finora

- Pin Diagram of 8086Documento21 paginePin Diagram of 8086adithya123456100% (5)

- Pinouts of 8086Documento12 paginePinouts of 8086Infinity Star GamingNessuna valutazione finora

- 8086 Pin DiagramDocumento9 pagine8086 Pin Diagram12343567890100% (2)

- 8086 NotesDocumento43 pagine8086 NotesSuma LathaNessuna valutazione finora

- 8086 FullDocumento72 pagine8086 FullNandhini Nachiyar100% (4)

- 8259 PIC AND 8237 DMA: by Harjot Kaur (2203448) Isha (2203461)Documento13 pagine8259 PIC AND 8237 DMA: by Harjot Kaur (2203448) Isha (2203461)Harjot KaurNessuna valutazione finora

- Memory InterfacingDocumento16 pagineMemory InterfacingTharshninipriya RajasekarNessuna valutazione finora

- Direct Memory Access (DMA) : Burst ModeDocumento7 pagineDirect Memory Access (DMA) : Burst ModeAnand ReddyNessuna valutazione finora

- Microprocessors: BY: Prof. Dileep J Dept. of TCE K.S.I.TDocumento16 pagineMicroprocessors: BY: Prof. Dileep J Dept. of TCE K.S.I.TsenthilNessuna valutazione finora

- System BusDocumento12 pagineSystem Busdipyaman patgiriNessuna valutazione finora

- Overview or Features of 8086Documento33 pagineOverview or Features of 8086Supraja SundaresanNessuna valutazione finora

- Microprocessor (ECC15101)Documento10 pagineMicroprocessor (ECC15101)MATAVALAM CHANDU PRIYANessuna valutazione finora

- Overview or Features of 8086: It Is A 16-Bit MicroprocessorDocumento33 pagineOverview or Features of 8086: It Is A 16-Bit MicroprocessorSamuel KuantumNessuna valutazione finora

- Unit 5Documento26 pagineUnit 5veenayak sirohiNessuna valutazione finora

- DMA Controller - 8237Documento9 pagineDMA Controller - 8237Umesh Harihara sudanNessuna valutazione finora

- 8085 Features, Signal DescriptionDocumento13 pagine8085 Features, Signal DescriptionRakesh Kumar DNessuna valutazione finora

- MP 07Documento36 pagineMP 07Jake GlobioNessuna valutazione finora

- Minimum and Maximum ModesDocumento21 pagineMinimum and Maximum ModesSubash BasnyatNessuna valutazione finora

- Unit I PDFDocumento25 pagineUnit I PDFSomnath2014Nessuna valutazione finora

- Unit 3 8086 Microprocessor InterfacingDocumento29 pagineUnit 3 8086 Microprocessor InterfacingDere JesusNessuna valutazione finora

- Interfacing With Intel 8251aDocumento7 pagineInterfacing With Intel 8251aSanthosh KumarNessuna valutazione finora

- Pin DaigramDocumento3 paginePin Daigramrathavachirag921Nessuna valutazione finora

- The Dma Controller 8257 and 8237 .Documento78 pagineThe Dma Controller 8257 and 8237 .BETHWEL KIPROTICHNessuna valutazione finora

- DMA Controller - DMA Controller 8257: Internal Architecture of 8257Documento8 pagineDMA Controller - DMA Controller 8257: Internal Architecture of 8257LAVANYA DURAISAMYNessuna valutazione finora

- MODULE-2 - Pin Diagram - Part 4Documento16 pagineMODULE-2 - Pin Diagram - Part 4eshwar211104Nessuna valutazione finora

- Minimum and Maximum Mode of 8086 of 8086: Sutapa SarkarDocumento26 pagineMinimum and Maximum Mode of 8086 of 8086: Sutapa SarkarNishal Bharadwaj NNessuna valutazione finora

- Ec6504 MPMC Unit 2Documento194 pagineEc6504 MPMC Unit 2dkNessuna valutazione finora

- 8086 System Bus StructureDocumento19 pagine8086 System Bus StructureArman IslamNessuna valutazione finora

- The 8086 Microprocessor Hardware Specifications: Pin Diagram of 8086 and Pin Description of 8086Documento9 pagineThe 8086 Microprocessor Hardware Specifications: Pin Diagram of 8086 and Pin Description of 8086bale baleNessuna valutazione finora

- 21CS1302 - Camp - Unit 4 NotesDocumento41 pagine21CS1302 - Camp - Unit 4 Notespec libraryNessuna valutazione finora

- Unit-1 (1) Draw and Explain The Internal Architecture of 8085Documento11 pagineUnit-1 (1) Draw and Explain The Internal Architecture of 8085Mann MehtaNessuna valutazione finora

- Mpa Question Bank1Documento16 pagineMpa Question Bank1Sharon FrancisNessuna valutazione finora

- The 8086 Microprocessor Architecture: (8086 Datasheet)Documento31 pagineThe 8086 Microprocessor Architecture: (8086 Datasheet)Feyisa BekeleNessuna valutazione finora

- Microprocessors 4Documento9 pagineMicroprocessors 4Ajnamol N RNessuna valutazione finora

- Pin Diagram of 8086, MIN Mode - MAX ModeDocumento10 paginePin Diagram of 8086, MIN Mode - MAX Modenskprasad89Nessuna valutazione finora

- Berry B Brey Part IDocumento49 pagineBerry B Brey Part Ikalpesh_chandakNessuna valutazione finora

- Signal Description of 8086 MicroprocessorDocumento8 pagineSignal Description of 8086 MicroprocessorRabiul Robi100% (1)

- 8086 MicroprocessorDocumento4 pagine8086 MicroprocessorTanu GuptaNessuna valutazione finora

- Parul University: Pin Diagram of 8086Documento14 pagineParul University: Pin Diagram of 8086Lakshmi KumariNessuna valutazione finora

- Unit II 8086 SYSTEM Bus Structure: BookDocumento194 pagineUnit II 8086 SYSTEM Bus Structure: BookGomathi PsNessuna valutazione finora

- MicroprocessorDocumento29 pagineMicroprocessorArnab RayNessuna valutazione finora

- DatasheetDocumento16 pagineDatasheetAmmu PuniNessuna valutazione finora

- Minimum and Maximum Modes of 8086Documento3 pagineMinimum and Maximum Modes of 8086Riya Chaudhary100% (1)

- Unit 3 Interfacing: InterfaceDocumento21 pagineUnit 3 Interfacing: Interfacechirag khandelwalNessuna valutazione finora

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Da EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Nessuna valutazione finora

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- SPANNING TREE PROTOCOL: Most important topic in switchingDa EverandSPANNING TREE PROTOCOL: Most important topic in switchingNessuna valutazione finora

- Materials Management - 1 - Dr. VP - 2017-18Documento33 pagineMaterials Management - 1 - Dr. VP - 2017-18Vrushabh ShelkarNessuna valutazione finora

- Pipe Freezing StudyDocumento8 paginePipe Freezing StudymirekwaznyNessuna valutazione finora

- Aex-Kissan KeralaDocumento25 pagineAex-Kissan Keralabsh08070Nessuna valutazione finora

- Prometric Questions-1 AnswersDocumento45 paginePrometric Questions-1 AnswersNina Grace Joy Marayag-Alvarez100% (1)

- V13 D03 1 PDFDocumento45 pagineV13 D03 1 PDFFredy Camayo De La CruzNessuna valutazione finora

- Zillah P. Curato: ObjectiveDocumento1 paginaZillah P. Curato: ObjectiveZillah CuratoNessuna valutazione finora

- The Sandbox Approach and Its Potential For Use inDocumento13 pagineThe Sandbox Approach and Its Potential For Use invalentina sekarNessuna valutazione finora

- The Ethics of Peacebuilding PDFDocumento201 pagineThe Ethics of Peacebuilding PDFTomas Kvedaras100% (2)

- ING C1 CO JUN2016 CorrectorDocumento6 pagineING C1 CO JUN2016 CorrectoraciameNessuna valutazione finora

- Iso 22301 2019 en PDFDocumento11 pagineIso 22301 2019 en PDFImam Saleh100% (3)

- QSasDocumento50 pagineQSasArvin Delos ReyesNessuna valutazione finora

- IoT Security Checklist Web 10 17 r1Documento39 pagineIoT Security Checklist Web 10 17 r1SubinNessuna valutazione finora

- 3DS 2017 GEO GEMS Brochure A4 WEBDocumento4 pagine3DS 2017 GEO GEMS Brochure A4 WEBlazarpaladinNessuna valutazione finora

- ASTR 323 Homework 4Documento2 pagineASTR 323 Homework 4Andrew IvanovNessuna valutazione finora

- Book Chapter 11 SubmissionDocumento18 pagineBook Chapter 11 Submissioncristine_2006_g5590Nessuna valutazione finora

- RS2 Stress Analysis Verification Manual - Part 1Documento166 pagineRS2 Stress Analysis Verification Manual - Part 1Jordana Furman100% (1)

- Chemical & Biological Depopulation (By Water Floridation and Food Additives or Preservatives) PDFDocumento178 pagineChemical & Biological Depopulation (By Water Floridation and Food Additives or Preservatives) PDFsogunmola100% (2)

- Penelitian Tindakan Kelas - Alberta Asti Intan Sherliana 20220049Documento25 paginePenelitian Tindakan Kelas - Alberta Asti Intan Sherliana 20220049Asti SherlyanaNessuna valutazione finora

- Action Plan in T.L.E Project Title Objectives Activities Person-In-Charge Time Frame Success IndicatorDocumento1 paginaAction Plan in T.L.E Project Title Objectives Activities Person-In-Charge Time Frame Success IndicatorEdelmar BenosaNessuna valutazione finora

- CrimDocumento29 pagineCrimkeziahmae.bagacinaNessuna valutazione finora

- Embedded Software Development ProcessDocumento34 pagineEmbedded Software Development ProcessAmmar YounasNessuna valutazione finora

- Lab 1Documento51 pagineLab 1aliNessuna valutazione finora

- WCDMA Radio Access OverviewDocumento8 pagineWCDMA Radio Access OverviewDocMasterNessuna valutazione finora

- (Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of TheraphyDocumento58 pagine(Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of Theraphyblueyes247Nessuna valutazione finora

- Collins Ks3 Science Homework Book 3Documento5 pagineCollins Ks3 Science Homework Book 3g3pz0n5h100% (1)

- Student Research Project Science ReportDocumento8 pagineStudent Research Project Science Reportapi-617553177Nessuna valutazione finora

- Unit 20: TroubleshootingDocumento12 pagineUnit 20: TroubleshootingDongjin LeeNessuna valutazione finora

- ANTINEOPLASTICSDocumento21 pagineANTINEOPLASTICSGunjan KalyaniNessuna valutazione finora

- ProjectDocumento32 pagineProjectroshan jaiswalNessuna valutazione finora

- Cella Di Carico Sartorius MP77 eDocumento3 pagineCella Di Carico Sartorius MP77 eNCNessuna valutazione finora