Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Tomasulo With Re-Order Buffer-V3

Caricato da

prakash_shrCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Tomasulo With Re-Order Buffer-V3

Caricato da

prakash_shrCopyright:

Formati disponibili

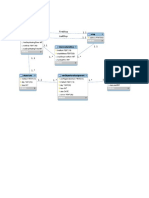

Tomasulo without Re-order Buffer

4 3 2 1 Opcode SD F0, Y MUL F0, F3, F4 SD F0, X MUL F0, F1, F2 Tag Tag Tag Tag Value Value Value Value F0 F1 F2 F3

Issue

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS Store1 RS Store2

Reservation station MUL1 Mul unit 2 Store unit 1 Store unit 2 Multiply unit 1

Issue:

Each instruction is issued in order Issue unit collects operands from the two instructions source registers Result may be a value, or, if value will be computed by an uncompleted instruction, the tag of the RS to which it was issued. When instruction 1 is issued, F0 is updated to get result from MUL1 When instruction 3 is issued, F0 is updated to get result from MUL2

Tomasulo without Re-order Buffer

4 3 2 1 Opcode SD F0, Y MUL F0, F3, F4 SD F0, X MUL F0, F1, F2 Tag Tag Tag Tag Value Value Value Value F0 F1 F2 F3

Issue

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS Store1 RS Store2

Reservation station MUL1 Mul unit 2 Store unit 1 Store unit 2 Multiply unit 1

Write-back:

Common data bus Instructions may complete out of order Result is broadcast on CDB Carrying tag of RS to which instruction was originally issued All RSs and registers monitor CDB and collect value if tag matches Any RS which has both operands and whose FU is free fires. When MUL1 completes result goes to store unit but not F0

4 3 2 1

SD F0, Y MUL F0, F3, F4 SD F0, X MUL F0, F1, F2

Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Opcode

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1 4 Dst null, Src STORE2

Reservation station MUL1

3 Mul unit 2 Add unit 2 Store unit 1 2

Dst F0, Src MUL2 Dst null, Src STORE1 Dst F0, Src MUL1

Multiply unit 1

Common data bus Commit F0 F1 F2 F3 value value value value

Tomasulo with Re-order Buffer

4 3 2 1

SD F0, Y MUL F0, F3, F4 SD F0, X MUL F0, F1, F2

Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Opcode

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1 4 Dst null, Src STORE2

Reservation station MUL1

3 Mul unit 2 Add unit 2 Store unit 1 2

Dst F0, Src MUL2 Dst null, Src STORE1 Dst F0, Src MUL1

Multiply unit 1

Issue: As before, but ROB entry is also allocated ROB entry for each instruction Holds destination register + value/tag for where it will come from F0 F1 F2 F3 value value value value

Common data bus Commit

Tomasulo with Re-order Buffer

4 3 2 1

SD F0, Y MUL F0, F3, F4 SD F0, X MUL F0, F1, F2

Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Opcode

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1 4 Dst null, Src STORE2

Reservation station MUL1

3 Mul unit 2 Add unit 2 Store unit 1 2

Dst F0, Src MUL2 Dst null, Src STORE1 Dst F0, Src MUL1

Multiply unit 1

Write Back:

Common data bus Commit value value value value

As before, but ROB entry with matching tag also updated

F0 F1 ROB entry for instruction 3 holds another value for F0 F2 F3 ROB entry for instruction 1 holds value for F0

Tomasulo with Re-order Buffer

4 3 2 1

SD F0, Y MUL F0, F3, F4 SD F0, X MUL F0, F1, F2

Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Opcode

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1 4 Dst null, Src STORE2

Reservation station MUL1

3 Mul unit 2 Add unit 2 Store unit 1 2

Dst F0, Src MUL2 Dst null, Src STORE1 Dst F0, Src MUL1

Multiply unit 1

Commit: Commit unit processes ROB entries in issue order Each instruction waits in turn and commits when its operands are completed Committed registers updated with values from ROB F0 is updated first with result from MUL1 then result from MUL2 F0 F1 F2 F3 value value value value

Common data bus Commit

4 3 2 1

SD F0, Y MUL F0, F3, F4 SD F0, X MUL F0, F1, F2

Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Opcode

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1 4 Dst null, Src STORE2

Reservation station MUL1

3 Mul unit 2 Add unit 2 Store unit 1 2

Dst F0, Src MUL2 Dst null, Src STORE1 Dst F0, Src MUL1

Multiply unit 1

Common data bus Issue-side registers (updated speculatively) Commit-side registers (updated when speculation resolved) F0 F1 F2 F3 value value value value Commit

Tomasulo with Re-order Buffer

5 4 3 2 1 Opcode

SD F0, Y MUL F0, F3, F4 BEQ R10, Lab SD F0, X MUL F0, F1, F2 Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1 5 Dst null, Src STORE2

Reservation station MUL1 Mul unit 2 Add unit 2 Store unit 1 Multiply unit 1

4 3 2

Dst F0, Src MUL2 BEQ R10, Lab (predNT) Dst null, Src STORE1 Dst F0, Src MUL1

1 Now extend example with conditional branch

Assume predicted Not Taken When BEQ reaches head of commit queue, all instructions which have been issued but have not yet committed are erroneous F0 F1 F2 F3 value value value value

Commit

5 4 3 2 1 Opcode

SD F0, Y MUL F0, F3, F4 BEQ R10, Lab SD F0, X MUL F0, F1, F2 Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1

Reservation station MUL1 Mul unit 2 Add unit 2 Store unit 1 5 Multiply unit 1 4 3 Misprediction: all ROB entries are trashed Issue-side registers reset from commit-side registers Correct branch target instruction fetched and issued F0 F1 F2 F3

Dst null, Src STORE2

Dst F0, Src MUL2

BEQ R10, Lab (predNT)

Commit Value from MUL1 value value value

5 4 3 2 1 Opcode

SD F0, Y MUL F0, F3, F4 BEQ R10, Lab SD F0, X MUL F0, F1, F2 Issue

Tag

Tag Tag Tag

Value

Value Value Value

F0

F1 F2 F3

Operand values/tags

Opcode Operand1 Operand2 RS MUL2 RS ADD1 RS Store1

Reservation station MUL1 Mul unit 2 Add unit 2 Store unit 1 5 Multiply unit 1 4 3 Committed F0 holds value from first MUL

Dst null, Src STORE2

Dst F0, Src MUL2

BEQ R10, Lab (predNT)

Commit

RS of uncompleted speculatively-executed instruction F0 Value from MUL1 cannot be re-used until its FU (eg MUL2) completes F1 value F2 value F3 value

Potrebbero piacerti anche

- Dynamic Scheduling Using Tomasulo's Algorithm: Lotzi BölöniDocumento54 pagineDynamic Scheduling Using Tomasulo's Algorithm: Lotzi BölöniChaitanya NittaNessuna valutazione finora

- cs433 Fa19 hw4 SolutionDocumento12 paginecs433 Fa19 hw4 Solutionheba AladwanNessuna valutazione finora

- ILP ScoreBoardDocumento45 pagineILP ScoreBoardRenuka ChilukuriNessuna valutazione finora

- L11 DS PDFDocumento41 pagineL11 DS PDFDarshanNessuna valutazione finora

- Advanced Computer Architecture-06CS81 Hardware Based Speculation (Unit 3)Documento5 pagineAdvanced Computer Architecture-06CS81 Hardware Based Speculation (Unit 3)Swastik NayakNessuna valutazione finora

- ILP2 (Unit4)Documento27 pagineILP2 (Unit4)Roxane holNessuna valutazione finora

- Tomasulo 2Documento8 pagineTomasulo 2tesfuNessuna valutazione finora

- Computer ArchitectureDocumento46 pagineComputer Architecturejaime_parada3097100% (2)

- Tomasulo Algorithm and Dynamic Branch PredictionDocumento57 pagineTomasulo Algorithm and Dynamic Branch PredictionEndless TravellerNessuna valutazione finora

- Lecture 6: Dynamic Scheduling With Scoreboarding and Tomasulo Algorithm (Section 2.4)Documento31 pagineLecture 6: Dynamic Scheduling With Scoreboarding and Tomasulo Algorithm (Section 2.4)Jan jan1Nessuna valutazione finora

- Dynamic Scheduling Using Tomasulo's Algorithm: Lotzi BölöniDocumento54 pagineDynamic Scheduling Using Tomasulo's Algorithm: Lotzi Bölöniprakash_shrNessuna valutazione finora

- Lecture04 DynamicSchedulingDocumento81 pagineLecture04 DynamicSchedulingNikitasNessuna valutazione finora

- HW3 Sol PDFDocumento5 pagineHW3 Sol PDFAnonymous GJK5Z8ZNessuna valutazione finora

- TomasuloDocumento54 pagineTomasulokickass12Nessuna valutazione finora

- ACA Unit 3 - Part - Hardware Based Speculation Notes - Unit 8Documento5 pagineACA Unit 3 - Part - Hardware Based Speculation Notes - Unit 8Ashwini BangeraNessuna valutazione finora

- Computer Architecture 計算機結構: ScoreboardDocumento36 pagineComputer Architecture 計算機結構: Scoreboardlloyd24390_874347375Nessuna valutazione finora

- Score BoardingDocumento38 pagineScore BoardingAqib AsadNessuna valutazione finora

- Dynamic SchedulingDocumento70 pagineDynamic Schedulingkasyap saiNessuna valutazione finora

- Lecture 9: Dynamic Scheduling: Kunle Olukotun Gates 302 Kunle@ogun - Stanford.eduDocumento14 pagineLecture 9: Dynamic Scheduling: Kunle Olukotun Gates 302 Kunle@ogun - Stanford.eduaakankshasssNessuna valutazione finora

- Dynamic Scheduling Using Tomasulo's Approach: - A Big PictureDocumento29 pagineDynamic Scheduling Using Tomasulo's Approach: - A Big PictureSridhar MenonNessuna valutazione finora

- Dynamic Approach Hardware Based SpeculationDocumento27 pagineDynamic Approach Hardware Based Speculationccn07Nessuna valutazione finora

- Memory-Mapped Peripherals (Ch.12)Documento46 pagineMemory-Mapped Peripherals (Ch.12)Suhaib AbugderaNessuna valutazione finora

- Lecture: Static ILP: Topics: Predication, Speculation (Sections C.5, 3.2)Documento26 pagineLecture: Static ILP: Topics: Predication, Speculation (Sections C.5, 3.2)Purab RanjanNessuna valutazione finora

- 18f Cpe221 Test2 SolutionDocumento6 pagine18f Cpe221 Test2 SolutionKyra LathonNessuna valutazione finora

- HardwareDocumento24 pagineHardwarepriyankaNessuna valutazione finora

- Adv Topic Compiler Supported ILPSlidesDocumento18 pagineAdv Topic Compiler Supported ILPSlidesAtharvaNessuna valutazione finora

- CSE502 Lec10 11-Dynamic-schedB SpeculationS10Documento36 pagineCSE502 Lec10 11-Dynamic-schedB SpeculationS10Ankita SharmaNessuna valutazione finora

- Instruction Level Parallelism: 1. Scoreboard and Tomasulo AlgorithmsDocumento72 pagineInstruction Level Parallelism: 1. Scoreboard and Tomasulo AlgorithmsSAMNessuna valutazione finora

- L12 TomasuloDocumento28 pagineL12 TomasuloNida CHNessuna valutazione finora

- 1 - 6. Exploiting ILPDocumento45 pagine1 - 6. Exploiting ILPMd JubairNessuna valutazione finora

- Dynamic Pipeline Scheduling: Ggitm-Cse 1Documento52 pagineDynamic Pipeline Scheduling: Ggitm-Cse 1vikram gargNessuna valutazione finora

- Intro To Static Pipelining: CS252 Graduate Computer ArchitectureDocumento52 pagineIntro To Static Pipelining: CS252 Graduate Computer Architectureشايك يوسفNessuna valutazione finora

- 2021 FinalDocumento16 pagine2021 Finalmorris gichuhiNessuna valutazione finora

- Tomasulo Algorithm: Register Renaming ProvidedDocumento12 pagineTomasulo Algorithm: Register Renaming ProvidedThiravia SelviNessuna valutazione finora

- Sections 3.2 and 3.3 Dynamic Scheduling - Tomasulo's AlgorithmDocumento53 pagineSections 3.2 and 3.3 Dynamic Scheduling - Tomasulo's AlgorithmvpsampathNessuna valutazione finora

- CSCI 510: Computer Architecture Written Assignment 2 SolutionsDocumento6 pagineCSCI 510: Computer Architecture Written Assignment 2 Solutionss_subbulakshmiNessuna valutazione finora

- Assignment 2Documento2 pagineAssignment 2Fateh Ali AlimNessuna valutazione finora

- Clearing Light Off: - Exxdrt005 - StoplightoffDocumento3 pagineClearing Light Off: - Exxdrt005 - StoplightoffJosephNessuna valutazione finora

- Lot Processing and Serial Number ControlDocumento25 pagineLot Processing and Serial Number ControlEdNessuna valutazione finora

- 2162 Term Project: The Tomasulo Algorithm ImplementationDocumento5 pagine2162 Term Project: The Tomasulo Algorithm ImplementationThomas BoyerNessuna valutazione finora

- Reset: - INV081 - Reset: INV 081 Basic Function SymbolDocumento4 pagineReset: - INV081 - Reset: INV 081 Basic Function SymbolJosephNessuna valutazione finora

- CortexM4 FPUDocumento14 pagineCortexM4 FPUMohamedAliFerjaniNessuna valutazione finora

- Configurable 2K/4K/8K Fft-Ifft Core For DVB-T and DVB-HDocumento4 pagineConfigurable 2K/4K/8K Fft-Ifft Core For DVB-T and DVB-HQuân NguyễnNessuna valutazione finora

- Lect12 TomasuloExample PDFDocumento41 pagineLect12 TomasuloExample PDFAhmad AsgharNessuna valutazione finora

- Station 1Documento140 pagineStation 1duyphuocNessuna valutazione finora

- Lec 21Documento35 pagineLec 21venuNessuna valutazione finora

- Assignment 2 SolutionDocumento3 pagineAssignment 2 SolutionAshley BNessuna valutazione finora

- Exception Handling: M. Krishna Kumar MM/M4/LU11/V1/2004 1Documento33 pagineException Handling: M. Krishna Kumar MM/M4/LU11/V1/2004 1bhuvi2312Nessuna valutazione finora

- Lecture 20Documento28 pagineLecture 20Udai ValluruNessuna valutazione finora

- The 8051Documento29 pagineThe 8051Rabia SaeedNessuna valutazione finora

- Information For Standards MT November 2016: Message Standards Deployment Package and Online HelpDocumento20 pagineInformation For Standards MT November 2016: Message Standards Deployment Package and Online HelpOscar Alberto ZambranoNessuna valutazione finora

- Score Board Contd. and Tomasulo's Algorithm: Instructor: Laxmi BhuyanDocumento62 pagineScore Board Contd. and Tomasulo's Algorithm: Instructor: Laxmi Bhuyanbobchang321Nessuna valutazione finora

- Ee660 2017 Spring Materials Week 04 SlidesDocumento40 pagineEe660 2017 Spring Materials Week 04 SlidesqaeszNessuna valutazione finora

- 1.1 Switch Status (Transmitted) : Auxiliary Input / Output Status 1Documento4 pagine1.1 Switch Status (Transmitted) : Auxiliary Input / Output Status 1ass manNessuna valutazione finora

- Setting Light Off: - Exxdrt004 - ExelightoffDocumento3 pagineSetting Light Off: - Exxdrt004 - ExelightoffJosephNessuna valutazione finora

- Pic Microcontroller: Technological University of The PhilippinesDocumento15 paginePic Microcontroller: Technological University of The PhilippinesRonnel Joseph Cooper Renedo100% (1)

- Sony Sirc ProtocolDocumento10 pagineSony Sirc ProtocolFrancisco HernandezNessuna valutazione finora

- Spos As1 305a027 Gadewar Parth 01Documento14 pagineSpos As1 305a027 Gadewar Parth 01Parth GadewarNessuna valutazione finora

- Anais Do Workshop De Micro-ondasDa EverandAnais Do Workshop De Micro-ondasNessuna valutazione finora

- JPT - SearchDocumento3 pagineJPT - Searchprakash_shrNessuna valutazione finora

- Slickdeals The Best Deals, Coupons, Promo Codes & DiscountsDocumento75 pagineSlickdeals The Best Deals, Coupons, Promo Codes & Discountsprakash_shrNessuna valutazione finora

- Computer Science ResumedocxDocumento1 paginaComputer Science ResumedocxMuja AhmadNessuna valutazione finora

- JPT - Google SearchDocumento2 pagineJPT - Google Searchprakash_shrNessuna valutazione finora

- JPT - SearchDocumento3 pagineJPT - Searchprakash_shrNessuna valutazione finora

- Computer Science ResumedocxDocumento1 paginaComputer Science ResumedocxMuja AhmadNessuna valutazione finora

- Readywares Waxed Canvas Tool Bucket Organizer $36.74 Free ShippingDocumento7 pagineReadywares Waxed Canvas Tool Bucket Organizer $36.74 Free Shippingprakash_shrNessuna valutazione finora

- Upload Me2Documento12 pagineUpload Me2prakash_shrNessuna valutazione finora

- Nepal NewsDocumento14 pagineNepal Newsprakash_shrNessuna valutazione finora

- Student Athlete ResumeDocumento1 paginaStudent Athlete Resumeappie yhunazcaNessuna valutazione finora

- UPload MeDocumento2 pagineUPload Meprakash_shrNessuna valutazione finora

- 100 Series Chipset Datasheet Vol 1Documento306 pagine100 Series Chipset Datasheet Vol 1prakash_shrNessuna valutazione finora

- Birthday MSGDocumento21 pagineBirthday MSGprakash_shrNessuna valutazione finora

- K Ho KK HoDocumento14 pagineK Ho KK Hoprakash_shrNessuna valutazione finora

- I 865instr PDFDocumento5 pagineI 865instr PDFprakash_shrNessuna valutazione finora

- UPload Me1Documento2 pagineUPload Me1prakash_shrNessuna valutazione finora

- Read MeDocumento1 paginaRead Meprakash_shrNessuna valutazione finora

- Canon EOS Rebel T5Documento342 pagineCanon EOS Rebel T5ab5918590Nessuna valutazione finora

- Something of A, Somewhat, A Bit: BBC Learning English Ask About EnglishDocumento3 pagineSomething of A, Somewhat, A Bit: BBC Learning English Ask About EnglishNguyen Quang HuyNessuna valutazione finora

- Github Git Cheat SheetDocumento2 pagineGithub Git Cheat SheetsuneelaemNessuna valutazione finora

- Atlassian Git Cheatsheet PDFDocumento2 pagineAtlassian Git Cheatsheet PDFJohn Le TourneuxNessuna valutazione finora

- D3300 SG (En) 02Documento144 pagineD3300 SG (En) 02Christer John UyNessuna valutazione finora

- 5 - Asynchronous Serial CommunicationDocumento3 pagine5 - Asynchronous Serial Communicationprakash_shrNessuna valutazione finora

- 4 - ADC and DACDocumento6 pagine4 - ADC and DACprakash_shrNessuna valutazione finora

- Lab4 PC Communications Ver00Documento4 pagineLab4 PC Communications Ver00prakash_shrNessuna valutazione finora

- 3 - Interrupts and IODocumento3 pagine3 - Interrupts and IOprakash_shrNessuna valutazione finora

- Lab 0 - IntroductionDocumento13 pagineLab 0 - Introductionprakash_shrNessuna valutazione finora

- Lab2 - PowerModes and ADC MSP430Documento6 pagineLab2 - PowerModes and ADC MSP430prakash_shrNessuna valutazione finora

- Lab 1 - OLED, GPIO, InterruptDocumento6 pagineLab 1 - OLED, GPIO, Interruptprakash_shrNessuna valutazione finora

- LAB 3: PWM and Timer: 2.1 Tool RequirementsDocumento4 pagineLAB 3: PWM and Timer: 2.1 Tool Requirementsprakash_shrNessuna valutazione finora

- Answer: C: Exam Name: Exam Type: Exam Code: Total QuestionsDocumento26 pagineAnswer: C: Exam Name: Exam Type: Exam Code: Total QuestionsMohammed S.GoudaNessuna valutazione finora

- Landscape ArchitectureDocumento9 pagineLandscape Architecturelisan2053Nessuna valutazione finora

- Chapter 13 Current Liabilities Test Bank Versi 2Documento72 pagineChapter 13 Current Liabilities Test Bank Versi 2Slamet Tri PrastyoNessuna valutazione finora

- Unit 1 Bearer PlantsDocumento2 pagineUnit 1 Bearer PlantsEmzNessuna valutazione finora

- Method Statement FINALDocumento61 pagineMethod Statement FINALshareyhou67% (3)

- The Intel 8086 / 8088/ 80186 / 80286 / 80386 / 80486 Jump InstructionsDocumento3 pagineThe Intel 8086 / 8088/ 80186 / 80286 / 80386 / 80486 Jump InstructionsalexiouconNessuna valutazione finora

- HKUST 4Y Curriculum Diagram CIVLDocumento4 pagineHKUST 4Y Curriculum Diagram CIVLfrevNessuna valutazione finora

- JEE Mains Paper 1 (12 Apr 2019 Shift 2) EnglishDocumento131 pagineJEE Mains Paper 1 (12 Apr 2019 Shift 2) EnglishRudraksha KushwahaNessuna valutazione finora

- What Is The PCB Shelf Life Extending The Life of PCBsDocumento9 pagineWhat Is The PCB Shelf Life Extending The Life of PCBsjackNessuna valutazione finora

- Oil List: Audi Front Axle DriveDocumento35 pagineOil List: Audi Front Axle DriveAska QianNessuna valutazione finora

- Dynamic Study of Parabolic Cylindrical Shell A Parametric StudyDocumento4 pagineDynamic Study of Parabolic Cylindrical Shell A Parametric StudyEditor IJTSRDNessuna valutazione finora

- Present Tenses ExercisesDocumento4 paginePresent Tenses Exercisesmonkeynotes100% (1)

- Sheetal PatilDocumento4 pagineSheetal PatilsheetalNessuna valutazione finora

- BV DoshiDocumento6 pagineBV DoshiNimNessuna valutazione finora

- Fashion DatasetDocumento2.644 pagineFashion DatasetBhawesh DeepakNessuna valutazione finora

- Fuentes v. Office of The Ombudsman - MindanaoDocumento6 pagineFuentes v. Office of The Ombudsman - MindanaoJ. JimenezNessuna valutazione finora

- PathologyDocumento31 paginePathologyStudy Usmle100% (1)

- Kortz Center GTA Wiki FandomDocumento1 paginaKortz Center GTA Wiki FandomsamNessuna valutazione finora

- Celula de CargaDocumento2 pagineCelula de CargaDavid PaezNessuna valutazione finora

- 95-03097 Ballvlv300350 WCB PDFDocumento26 pagine95-03097 Ballvlv300350 WCB PDFasitdeyNessuna valutazione finora

- Employee of The Month.Documento2 pagineEmployee of The Month.munyekiNessuna valutazione finora

- (Problem Books in Mathematics) Antonio Caminha Muniz Neto - An Excursion Through Elementary Mathematics, Volume III - Discrete Mathematics and Polynomial Algebra (2018, Springer)Documento647 pagine(Problem Books in Mathematics) Antonio Caminha Muniz Neto - An Excursion Through Elementary Mathematics, Volume III - Discrete Mathematics and Polynomial Algebra (2018, Springer)Anonymous iH6noeaX7100% (2)

- 6int 2008 Dec ADocumento6 pagine6int 2008 Dec ACharles_Leong_3417Nessuna valutazione finora

- SHS G11 Reading and Writing Q3 Week 1 2 V1Documento15 pagineSHS G11 Reading and Writing Q3 Week 1 2 V1Romeo Espinosa Carmona JrNessuna valutazione finora

- New Presentation-Group AuditingDocumento23 pagineNew Presentation-Group Auditingrajes wariNessuna valutazione finora

- Index: © Christopher Pitt 2018 C. Pitt, The Definitive Guide To AdonisjsDocumento5 pagineIndex: © Christopher Pitt 2018 C. Pitt, The Definitive Guide To AdonisjsZidi BoyNessuna valutazione finora

- Rapp 2011 TEREOS GBDocumento58 pagineRapp 2011 TEREOS GBNeda PazaninNessuna valutazione finora

- ManualDocumento50 pagineManualspacejung50% (2)

- Writ Petition 21992 of 2019 FinalDocumento22 pagineWrit Petition 21992 of 2019 FinalNANDANI kumariNessuna valutazione finora

- Makalah Bahasa Inggris TranslateDocumento14 pagineMakalah Bahasa Inggris TranslatevikaseptideyaniNessuna valutazione finora