Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Microprocessor 8085 Architecture

Caricato da

Yeswanth GollaDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Microprocessor 8085 Architecture

Caricato da

Yeswanth GollaCopyright:

Formati disponibili

Basic Processor Architecture

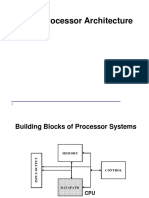

Building Blocks of Processor Systems

MEM ORY

INPUT-OUTPUT

CONTROL

DATAPATH

CPU

Processor System Architecture

The typical processor system consists of:

CPU (central processing unit) ALU (arithmetic-logic unit) Control Logic Registers, etc Memory Input / Output interfaces

Interconnections between these units:

3

Address Bus Data Bus Control Bus

Bus and CPU

Bus: A shared group of wires used for communicating signals among devices

address bus: the device and the location within the device that is being accessed data bus: the data value being communicated control bus: describes the action on the address and data buses

CPU: Core of the processor, where instructions are executed

High-level language: a = b + c Assembly language: add r1 r2 r3 Machine language: 0001001010111010101

Memory and I/O

Memory: Where instructions (programs) and data are stored

Organized in arrays of locations (addresses), each storing one byte (8 bits) in general A read operation to a particular location always returns the last value stored in that location

I/O devices: Enable system to interact with the world

Device interface (a.k.a. controller or adapter) hardware connects actual device to bus The CPU views the I/O device registers just like memory that can be accessed over the bus. However, I/O registers are connected to external wires, device control logic, etc. Reads may not return last value written Writes may have side effects

8085 Microprocessor Architecture

The 8085 Bus Structure

The 8-bit 8085 CPU (or MPU Micro Processing Unit) communicates with the other units using a 16-bit address bus, an 8-bit data bus and a control bus.

The 8085 Bus Structure

Address Bus

Consists of 16 address lines: A0 A15

Operates in unidirectional mode: The address bits are always sent from the MPU to peripheral devices, not reverse. 16 address lines are capable of addressing a total of 216 = 65,536 (64k) memory locations. Address locations: 0000 (hex) FFFF (hex)

The 8085 Bus Structure

Data Bus Consists of 8 data lines: D0 D7 Operates in bidirectional mode: The data bits are sent from the MPU to peripheral devices, as well as from the peripheral devices to the MPU. Data range: 00 (hex) FF (hex)

Control Bus Consists of various lines carrying the control signals such as read / write enable, flag bits.

The 8085: CPU Internal Structure

The internal architecture of the 8085 CPU is capable of performing the following operations:

Store 8-bit data (Registers, Accumulator) Perform arithmetic and logic operations (ALU) Test for conditions (IF / THEN)

Sequence the execution of instructions

Store temporary data in RAM during execution

10

The 8085: CPU Internal Structure

Simplified block diagram

11

The 8085: Registers

12

The 8085: CPU Internal Structure

Registers Six general purpose 8-bit registers: B, C, D, E, H, L They can also be combined as register pairs to perform 16-bit operations: BC, DE, HL Registers are programmable (data load, move, etc.)

Accumulator

13

Single 8-bit register that is part of the ALU !

Used for arithmetic / logic operations the result is always stored in the accumulator.

The 8085: CPU Internal Structure

Flag Bits Indicate the result of condition tests. Carry, Zero, Sign, Parity, etc.

Conditional operations (IF / THEN) are executed based on the condition of these flag bits.

Program Counter (PC)

Contains the memory address (16 bits) of the instruction that will be executed in the next step.

Stack Pointer (SP)

14

Example: Memory Read Operation

15

Example: Instruction Fetch Operation

All instructions (program steps) are stored in memory.

To run a program, the individual instructions must be read from the memory in sequence, and executed.

Program counter puts the 16-bit memory address of the instruction on the address bus Control unit sends the Memory Read Enable signal to access the memory The 8-bit instruction stored in memory is placed on the data bus and transferred to the instruction decoder Instruction is decoded and executed

16

Example: Instruction Fetch Operation

17

Example: Instruction Fetch Operation

18

8085 Functional Block Diagram

19

Potrebbero piacerti anche

- EC1362 Microprocessor & Microcontroller: Building Blocks of Processor SystemsDocumento4 pagineEC1362 Microprocessor & Microcontroller: Building Blocks of Processor SystemsPrakash ShankarNessuna valutazione finora

- EC1362 Microprocessor & Microcontroller: Building Blocks of Processor SystemsDocumento4 pagineEC1362 Microprocessor & Microcontroller: Building Blocks of Processor SystemsPrakash ArumugamNessuna valutazione finora

- Microprocessor 8085 ArchitectureDocumento19 pagineMicroprocessor 8085 ArchitecturevigneshNessuna valutazione finora

- Microprocessor 8085 ArchitectureDocumento19 pagineMicroprocessor 8085 ArchitectureSuresh PalanisamyNessuna valutazione finora

- Microprocessor 8085 ArchitectureDocumento19 pagineMicroprocessor 8085 ArchitectureraviNessuna valutazione finora

- Basic Processor ArchitectureDocumento19 pagineBasic Processor ArchitectureBhagyashree SharmaNessuna valutazione finora

- Microprocessor 8085 ArchitectureDocumento19 pagineMicroprocessor 8085 ArchitectureSravanthi BunnuNessuna valutazione finora

- Number Representations and Basic Processor Architecture: Prof. Yusuf Leblebici Microelectronic Systems Laboratory (LSM)Documento26 pagineNumber Representations and Basic Processor Architecture: Prof. Yusuf Leblebici Microelectronic Systems Laboratory (LSM)vikramNessuna valutazione finora

- Name: S. Karthikeyan. Class: ll-MECHATRONICS. ROLL NO: 17MC023. Sub: Microprocessor & Microcontroller. DATE: 16/04/2019Documento14 pagineName: S. Karthikeyan. Class: ll-MECHATRONICS. ROLL NO: 17MC023. Sub: Microprocessor & Microcontroller. DATE: 16/04/2019Shocky SNessuna valutazione finora

- 8085Documento56 pagine8085Kunal MeherNessuna valutazione finora

- Microprocessor 8-bit TitleDocumento55 pagineMicroprocessor 8-bit TitleAASTHA KIETNessuna valutazione finora

- Experiment No: 1: OBJECTIVE: To Study About The Bus Organization and Programmable Model ofDocumento5 pagineExperiment No: 1: OBJECTIVE: To Study About The Bus Organization and Programmable Model ofRutul PrajapatiNessuna valutazione finora

- Architecture of 8085 MicroprocessorDocumento69 pagineArchitecture of 8085 Microprocessornamrata puranikNessuna valutazione finora

- Unit I The 8086 MicroprocessorDocumento21 pagineUnit I The 8086 Microprocessor16211a0470100% (1)

- Basics of Micro ProcessorDocumento27 pagineBasics of Micro ProcessorBibin LeeNessuna valutazione finora

- Eec 503 PDFDocumento22 pagineEec 503 PDFmohitNessuna valutazione finora

- of Unit-1: Introduction To Microprocessor and Microprocessor 8085Documento22 pagineof Unit-1: Introduction To Microprocessor and Microprocessor 8085abahynNessuna valutazione finora

- CSEMPMSLNotes2013 PDFDocumento102 pagineCSEMPMSLNotes2013 PDFnskprasad89Nessuna valutazione finora

- Ebooks For FreeDocumento24 pagineEbooks For FreeNihar KhuranaNessuna valutazione finora

- MPMC Eee Unit - III 8051 MicrocontrollerDocumento35 pagineMPMC Eee Unit - III 8051 MicrocontrollerAnonymous 4u5XkWGONessuna valutazione finora

- 8085 MicroprocessorDocumento25 pagine8085 Microprocessorprofessor2062Nessuna valutazione finora

- Introduction To Microprocessor and Microcomputer ArchitectureDocumento6 pagineIntroduction To Microprocessor and Microcomputer Architecturesri vatsaNessuna valutazione finora

- MP ND MCDocumento58 pagineMP ND MCPraveen SinghNessuna valutazione finora

- Introduction to 8085 Architecture and Programming TutorialDocumento23 pagineIntroduction to 8085 Architecture and Programming TutorialKorak MitraNessuna valutazione finora

- UNIT-I: Introduction To Microprocessors: Microprocessor and MicrocontrollersDocumento14 pagineUNIT-I: Introduction To Microprocessors: Microprocessor and MicrocontrollersAtif HussainNessuna valutazione finora

- UNIT-I: Introduction To Microprocessors: Microprocessor and MicrocontrollersDocumento14 pagineUNIT-I: Introduction To Microprocessors: Microprocessor and MicrocontrollersGagandeep SinghNessuna valutazione finora

- Microprocessor & microcontroller introductionDocumento20 pagineMicroprocessor & microcontroller introductionjeravi84Nessuna valutazione finora

- Microprocessors and MicrocontrollersDocumento22 pagineMicroprocessors and Microcontrollers6012 ANILNessuna valutazione finora

- Microprocessor - SGDocumento15 pagineMicroprocessor - SGSugata Ghosh0% (1)

- MICROPROCESSOR ARCHITECTUREDocumento40 pagineMICROPROCESSOR ARCHITECTUREAlango Jr TzNessuna valutazione finora

- 8085 MicroprocessorDocumento23 pagine8085 Microprocessorauromaaroot196% (55)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Da EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Nessuna valutazione finora

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Da EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Nessuna valutazione finora

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12Da EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12Nessuna valutazione finora

- Foundation Course for Advanced Computer StudiesDa EverandFoundation Course for Advanced Computer StudiesNessuna valutazione finora

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDa EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNessuna valutazione finora

- Assembly Language:Simple, Short, And Straightforward Way Of Learning Assembly ProgrammingDa EverandAssembly Language:Simple, Short, And Straightforward Way Of Learning Assembly ProgrammingValutazione: 2 su 5 stelle2/5 (1)

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6Da EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6Nessuna valutazione finora

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Da EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Nessuna valutazione finora

- SNES Architecture: Architecture of Consoles: A Practical Analysis, #4Da EverandSNES Architecture: Architecture of Consoles: A Practical Analysis, #4Nessuna valutazione finora

- Master System Architecture: Architecture of Consoles: A Practical Analysis, #15Da EverandMaster System Architecture: Architecture of Consoles: A Practical Analysis, #15Nessuna valutazione finora

- ARM Microcontrollers Programming for Embedded SystemsDa EverandARM Microcontrollers Programming for Embedded SystemsValutazione: 5 su 5 stelle5/5 (1)

- Modern Assembly Language Programming with the ARM ProcessorDa EverandModern Assembly Language Programming with the ARM ProcessorNessuna valutazione finora

- Game Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7Da EverandGame Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7Nessuna valutazione finora

- Operating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesDa EverandOperating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNessuna valutazione finora

- Embedded Controller Forth For The 8051 FamilyDa EverandEmbedded Controller Forth For The 8051 FamilyValutazione: 4 su 5 stelle4/5 (1)

- Rtos AssignmentDocumento3 pagineRtos AssignmentYeswanth GollaNessuna valutazione finora

- Circular: Description Period RemarksDocumento1 paginaCircular: Description Period RemarksYeswanth GollaNessuna valutazione finora

- VIS Lab Record Exp No 5 - Arrays and Clusters in LabVIEWDocumento4 pagineVIS Lab Record Exp No 5 - Arrays and Clusters in LabVIEWYeswanth GollaNessuna valutazione finora

- Opamp CircuitDocumento24 pagineOpamp Circuitlinuxlism100% (1)

- Prepaid mobile charging solution for stationsDocumento2 paginePrepaid mobile charging solution for stationsYeswanth GollaNessuna valutazione finora

- PassportApplicationForm Main English V1.0Documento2 paginePassportApplicationForm Main English V1.0Triloki KumarNessuna valutazione finora

- Cisf HardwareDocumento32 pagineCisf Hardwarethinesshvaran.kNessuna valutazione finora

- Lesson 3Documento4 pagineLesson 3api-251229542Nessuna valutazione finora

- Studentnotes CDocumento29 pagineStudentnotes Cshwetamud1Nessuna valutazione finora

- Quick Start Guide for ZigBee Operator ToolDocumento21 pagineQuick Start Guide for ZigBee Operator ToolrahulbhansaliNessuna valutazione finora

- Introduction To The Microprocessor and MicrocomputerDocumento4 pagineIntroduction To The Microprocessor and MicrocomputerAriane Faye SalongaNessuna valutazione finora

- Research Examples in Computer Forensics (Michael M. W. de Silva, 2009)Documento29 pagineResearch Examples in Computer Forensics (Michael M. W. de Silva, 2009)Michael M. W. de SilvaNessuna valutazione finora

- JNTU Embedded Systems SyllabusDocumento110 pagineJNTU Embedded Systems Syllabus9740177035Nessuna valutazione finora

- Programmable Logic ControllerDocumento25 pagineProgrammable Logic Controllermanoj4sivaNessuna valutazione finora

- Instruction Manual Bush Spira B3 10" TabletDocumento56 pagineInstruction Manual Bush Spira B3 10" TabletNoss DakoNessuna valutazione finora

- Server Master Class Main Deck v3 (Partners Share) PDFDocumento96 pagineServer Master Class Main Deck v3 (Partners Share) PDFAbdul Rehman AbidNessuna valutazione finora

- Week 2 Introduction To OS StudentDocumento69 pagineWeek 2 Introduction To OS StudentArnold NarvacanNessuna valutazione finora

- Netapp V-Series For Heterogeneous Storage Environments: SystemsDocumento4 pagineNetapp V-Series For Heterogeneous Storage Environments: SystemsdebajyotiguhaNessuna valutazione finora

- Serial Interface c135-6 EnglishDocumento90 pagineSerial Interface c135-6 EnglishLucian IftemieNessuna valutazione finora

- Basics of Computer Application: Shivangi Singh M.SC Electronic MediaDocumento7 pagineBasics of Computer Application: Shivangi Singh M.SC Electronic MediaAnjali GuptaNessuna valutazione finora

- Operating System Questions MCQDocumento13 pagineOperating System Questions MCQSwetha D75% (4)

- Operation Manual Mazak: Micro Disc SystemDocumento38 pagineOperation Manual Mazak: Micro Disc SystemRashedul HasanNessuna valutazione finora

- Hitachi Unified Storage Getting Started Guide PDFDocumento92 pagineHitachi Unified Storage Getting Started Guide PDFquynhto89Nessuna valutazione finora

- IBM I (AS/400) System Operations and AdministrationDocumento3 pagineIBM I (AS/400) System Operations and AdministrationMadhuNessuna valutazione finora

- H.264 DVR6304 User's ManualDocumento73 pagineH.264 DVR6304 User's ManualbozapubNessuna valutazione finora

- 23 Best Practices To Improve Hyper-V and VM PerformanceDocumento6 pagine23 Best Practices To Improve Hyper-V and VM PerformanceAlemseged HabtamuNessuna valutazione finora

- Latitude 7.0 System Specifications 24 Sep 2015Documento7 pagineLatitude 7.0 System Specifications 24 Sep 2015Hansel Manuel Torres EyssericNessuna valutazione finora

- CS001 Midterm Solved McQs Papers by Waqar SidhuDocumento16 pagineCS001 Midterm Solved McQs Papers by Waqar SidhuAhmed NawazNessuna valutazione finora

- 1.1 Fill in The Blanks in Each of The FollowingDocumento3 pagine1.1 Fill in The Blanks in Each of The FollowingMuhammad Mahadi HasanNessuna valutazione finora

- MTA 98-368 Mobile Fundamentals - Study GuideDocumento89 pagineMTA 98-368 Mobile Fundamentals - Study GuideTom100% (1)

- UT165 Flash Compatibility ListDocumento2 pagineUT165 Flash Compatibility ListRaul Trujillo PNessuna valutazione finora

- Asa Flash Error TsDocumento6 pagineAsa Flash Error Tsdeivid_10Nessuna valutazione finora

- Jagadesh 600 MCQDocumento131 pagineJagadesh 600 MCQraajiNessuna valutazione finora

- Memory Chips and Finite State MachinesDocumento18 pagineMemory Chips and Finite State MachinesAlexander TaylorNessuna valutazione finora

- Computer parts and program executionDocumento8 pagineComputer parts and program executionRabab ElkomyNessuna valutazione finora

- QuizDocumento6 pagineQuizbijiNessuna valutazione finora