Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Folded Cascode Chopper

Caricato da

girishknathDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Folded Cascode Chopper

Caricato da

girishknathCopyright:

Formati disponibili

LOW-POWER LOW-VOLTAGE CHOPPED

TRANSCONDUCTANCE AMPLIFIER FOR

NOISE AND OFFSET REDUCTION

M.A.T. Sanduleanu

1

, B. Nauta

2

and H.Wallinga

1

1

University of Twente, Department of Electrical Engineering

P.O.Box 217, 7500 AE Enschede, The Netherlands

E_mail: m.a.t.sanduleanu@el.utwente.nl

2

Philips Research Laboratories, Prof. Holstlaan 4, 5656 AA

Eindhoven, The Netherlands

ABSTRACT

This paper describes the principle and design of a CMOS low-power, low-

voltage, chopped transconductance amplifier, for noise and offset reduction

in mixed analogue digital applications. The operation is based on chopping

and dynamic element matching, to reduce noise and offset, without

excessive increase of the charge injection residual offset. Experimental

results show residual offsets of less than 150V at 100kHz chopping

frequency, a signal to noise ratio of 95dB, in audio band, for 100KHz

chopping and a THD of -89dB. The power consumption is 594W.

1. INTRODUCTION

The CMOS technology for mixed signal applications becomes less and less compatible with

analog requirements due to the process tuning towards digital needs. As a consequence for

analog functions built in digital CMOS the signal swing reduces with power supply and so

does the dynamic range. Besides, 1/f noise properties are worsened for surface PMOSTs in

comparison to buried transistors, with an order of magnitude, and this under the conditions of

a heavy crosstalk via the substrate from digital functions. At 3.3V and a 0.5m CMOS

technology, the substrate bounce can reach 300mV in amplitude with spectral contributions in

GHz range, further reducing the voltage swing [1], [4]. In conventional chopper stabilized

opamps for 1/f noise and offset reduction, differential amplifiers are being used and

bandwidth is limited to few tens of kHz [2]. Switching at the differential output will introduce

most of the switching noise and residual offset. This paper presents a chopped

transconductance amplifier which circumvents the above mentioned drawbacks. The chopping

frequency can reach MHz range without excessive increase in offset.

2. CIRCUIT PRINCIPLE

Fig.1 shows the circuit diagram. The input chopper M10, M11, M13 and M15 transposes the

differential input signal applied to the terminals IN+ and IN- to the alternate output nodes.

Fig.1: Circuit diagram

As a result, the signal is modulated at odd harmonics of the chopper frequency. The second chopper

M19, M20, M21 and M22 demodulates the signal and modulates 1/f noise and offset at odd

harmonics. A cascoded mirror M24, M25, M12 and M14 performs a broadband differential to

single ended conversion. The need for large bandwidth implies small transistor lengths for M12 and

M14 and therefore extra offset and 1/f noise. For this reason a third chopper is being introduced in

the signal path: M27, M28, M29 and M30. The transistors M12 and M14 are dynamically matched

[3] without consequences on signal. The unswitched cascode transistors provide further

improvement in switching noise and residual offset by low pass filtering some of the HF noise

components generated from chopping and keeping low voltage swings at their sources. In order to

minimize substrate interferences, only PMOS transistors and NMOS switches with small

dimensions are being used in the signal path [4]. The oxide capacitance of M34 decouples the BIAS

line to VSS. Substrate interferences present in the sources of cascode transistors M23 and M26 will

be also present at their gates such that gate source voltages of the same transistors can be considered

constant for HF substrate noise [4]. For the same reason, the current sources M6 and M7 have their

gates decoupled to VSS via a large capacitance.

3. NOISE AND OFFSET

Neglecting the noise introduced by cascode transistors and switches, the power spectral density of

the white and 1/f noise referred to the input is:

( )

( )

( )

( )

( )

Sv f

kT

g

g

g

g

g

k

W L f

k

k

W L

W L

g

g

W L

W L

g

g

w f

m

m

m

m

m

FP FN

FP

m

m

m

m

+

+ +

1

]

1

+ +

_

,

+

_

,

1

]

1

1

1/

2

6

2

12

2 2 2

2 2

6 6

6

2

2

2 2

12 12

12

2

2

8

3

2 1 2 1 ( ) (1)

where k

FN

and k

FP

are process dependent constants. Large transconductances of the differential input

pair give low white noise. 1/f noise can be minimized by increasing the area of the input pair and

increasing the transconductance of the input transistors in comparison to the transconductances of

M6 and M12. If V

T

denotes the threshold mismatch, / the relative gain factor mismatch, V

GT

the effective gate voltage (V

GS

-V

T

), n the slope factor and U

T

the thermal voltage, the offset voltage

referred to the input can be computed from:

( ) ( ) ( ) ( )

V V n U

n U

V

V n U

n U

V

V n U

OS T T

T

GT

T T

T

GT

T T

+

_

,

+ +

_

,

+ +

_

,

2

2

2 2 2

2

2

2 2

12

2 12

2

2 2 12

12

2

2 2

6

2 6

2

2 2 7

7

2

16

4

32

8 (2)

The dominant terms in the offset voltage are due to the threshold mismatch of the input pair and the

threshold mismatch of M12 and M14. Large phase margins can be obtained when M12 and M14

have small lengths. This increases their contribution to the offset and noise. Dynamic element

matching is being used to reduce this effect. Fig.2 shows the simulated static dynamic range of the

OTA and the static offset as a function of the bias current JBIAS. The OTA has been configured as

a follower with 10MHz gain bandwidth product (GBW). By scaling down the current according to

W scaling [1] and keeping the same power supply voltage and GBW, a factor 10 reduction in power

gives a 10dB reduction in DR. This can be seen also from the DR*GBW product of the OTA. If P

denotes the total power, the saturation limits at the output node, n the slope factor and NEF the

noise excess factor DR*GBW is:

DR GBW

P

n KT NEF

V

U V

DD

T DD

_

,

80

1

2

2

(3)

By chopping, the offset of the amplifier is removed in the same way as 1/f noise. Charge injection in

the input modulator causes spikes at the input and this gives residual offset. The residual offset in a

follower configuration and after low pass filtering can be computed from:

Vos residual Vinj

jk

T T

j

k T

g C

j k

T

T

o

m gs

k

k odd

,

/

/

/

+

_

,

_

,

4

1 2 1 2

2 23

0

(4)

V

inj

represents the amplitude of the spikes at the input, T

0

the time constant of the charge injected, T

is the chopping period and C

gs23

the gate-source capacitance of M23 and M26. By using Poisson

summation rule for series and considering g

m2

/2C

gs23

larger than F

chopp

, we get:

( )

( ) ( )

Vos residual Vinj

g C

T g C

T g C

T g C

T T

T T

VinjT F

m gs

m gs

m gs

m gs

chopp

,

/

/ /

tanh /

/

tanh /

/

1

]

1

1

2 23

0 2 23

2 23

2 23

0

0

0

2

1 2

4

2

4

2

2 (5)

This shows an increase of the residual offset with chopping frequency and the energy of the spikes.

4. EXPERIMENTAL RESULTS

The chopped transconductance amplifier has

been realized in a 0.5 m CMOS technology.

For measurements purposes OTA has been

configured as a follower with a bias current of

30 A. Fig.3 shows the static offset and the

residual offset for 6 arbitrarily chosen circuit

samples after low pass filtering the output.

Without chopping (Fchopp=0), static offsets

of less than 680V can occur. Chopping will

reduce the offset for relatively low chopper

frequencies but increasing the chopping

frequency the residual offset will increase.

This is in close agreement with eq. (5). The

Fig.2: DR(static) and offset(static)

residual offset at 100KHz chopping frequency is less than 150V. At low chopping frequencies, a

minimum in residual offset occurs. Fig.4 shows the signal to noise plus distortion figure (SINAD)

for 100KHz chopping and 1KHz input. The input signal at 0dB reaches 2.8Vpp where distortion is

high and dominates SINAD. For low signal amplitudes the noise level is higher than the distortion

level. The measured signal to noise ratio in audio band (0..20KHz) after chopping is -95dB and

harmonic distortion (THD) is -89dB at -15dB signal level. Chopping increases signal to noise ratio

with about 6dB. The same performance can be achieved without chopping but increasing the power

consumption 4 times (2.4mW) as estimated by eq.(3). Fig.5 shows the chip photo and Table1 a

performance summary of the circuit.

Fig.3: Static(F

chopp

=0) and residual offset

Fig.4: SINAD at Fchopp=93KHz

Fig.5: Chip photo

5. CONCLUSIONS

Open-loop gain >75dB

GBW 10MHz

Offset(static) <1.1mV

Offset(chopped) <370V

Chopping frequency Fchopp1MHz

S/N|

Fchopp=93KHz

95dB

S/N|

Fchopp=0

89dB

Harmonic distortion -89dB

Supply voltage 3.3Vt10%

Power consumption 594W

Technology 0.5m, 2PS,

3AL, CMOS

Area 0.0308mm

2

Table 1: Performance summary

A low-voltage, low-power, chopped transconductance amplifier for mixed analogue digital

applications has been presented. Chopping and dynamic element matching allow low noise and low

residual offsets up to 1MHz. The unswitched cascode transistors provide further improvement in

residual offset and switching noise by low pass filtering some of the HF components generated from

chopping. The sensitivity to substrate noise is taken into account in the design. Experimental results

show residual offsets of less than 150V at 100KHz chopping frequency and a signal to noise ratio

in audio band of 95dB at 93KHz chopping. The power consumption is 594W at 3.3V supply.

ACKNOWLEDGEMENTS

The authors acknowledge the help of M. Dijkstra from Philips Research during measurements.

REFERENCES

[1] B. Nauta, Analog CMOS low-power design considerations, Low-Power Low-voltage

workshop at ESSCIRC96, Neuchatel-Switzerland, September 1996.

[2] K.C. Hsieh et al., A low-noise chopper-stabilized differential switched-capacitor filtering

technique, IEEE J. Solid-State Circuits, vol. SC-18, pp. 708-715, Dec. 1981.

[3] R.J. van de Plassche et al., A monolithic 14-bit D/A converter, IEEE J. Solid-State Circuits,

vol. SC-14, pp.552-556, June 1979.

[4] B. Nauta and G.Hoogzaad, How to deal with substrate noise in analog CMOS circuits,

European Conference on Circuit Theory and Design, Budapest, September 1997.

Potrebbero piacerti anche

- A Fully Differential Chopper Circuit in 130nm CMOSDocumento10 pagineA Fully Differential Chopper Circuit in 130nm CMOSWala SaadehNessuna valutazione finora

- PROJECT1 S 2013 v2 PDFDocumento4 paginePROJECT1 S 2013 v2 PDFHarshal SinghNessuna valutazione finora

- Question BankDocumento6 pagineQuestion Banksweetkhushboo786_592Nessuna valutazione finora

- Design of CMOS Fully Differential Operational Transconductance AmplifierDocumento24 pagineDesign of CMOS Fully Differential Operational Transconductance AmplifierAbhijit Kuvar100% (2)

- A CMOS Bandgap Reference Circuit With Sub-1V OperationDocumento5 pagineA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyNessuna valutazione finora

- Fully Differential CMOS Voltage AmplifierDocumento16 pagineFully Differential CMOS Voltage AmplifierAjit Narwal0% (1)

- Lecture 12 SRAMDocumento37 pagineLecture 12 SRAMSachin MalikNessuna valutazione finora

- Comparative Analysis of Different Architectures of CMOS ComparatorDocumento4 pagineComparative Analysis of Different Architectures of CMOS Comparatorj4everNessuna valutazione finora

- MMIC Design, Part 2 - ProcessingDocumento23 pagineMMIC Design, Part 2 - ProcessingVishal IyerNessuna valutazione finora

- EC2 Exp2 F09Documento17 pagineEC2 Exp2 F09Nurul Hanim HashimNessuna valutazione finora

- Two-Stage Operational Amplifier Design Using Gm/Id MethodDocumento7 pagineTwo-Stage Operational Amplifier Design Using Gm/Id Methodabhinav kumarNessuna valutazione finora

- CMOS Design RulesDocumento21 pagineCMOS Design Rulesrakheep123Nessuna valutazione finora

- MIM Cap ModelDocumento4 pagineMIM Cap ModelDuc DucNessuna valutazione finora

- Layout 02Documento38 pagineLayout 02Bulcea PaulNessuna valutazione finora

- Differential Amplifier LayoutDocumento9 pagineDifferential Amplifier LayoutFrancisco De KamimoreNessuna valutazione finora

- An Operational Amplifier Architecture With A Single Gain Stage and Distortion CancellationDocumento21 pagineAn Operational Amplifier Architecture With A Single Gain Stage and Distortion CancellationLuis FreitasNessuna valutazione finora

- Design High Speed, Low Noise, Low Power Two Stage CMOSDocumento5 pagineDesign High Speed, Low Noise, Low Power Two Stage CMOSsanjeevsoni64Nessuna valutazione finora

- Amplifier Project GradDocumento5 pagineAmplifier Project Gradمحمد قاسم نفل سميرNessuna valutazione finora

- Design of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Documento2 pagineDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Shahin ShahNessuna valutazione finora

- Design and Implementation of A 10 Bit SAR ADCDocumento4 pagineDesign and Implementation of A 10 Bit SAR ADCVipul ChauhanNessuna valutazione finora

- Buffer AmplifierDocumento9 pagineBuffer AmplifierDicky D.M.Nessuna valutazione finora

- FM - PM Demodulation - The Phase Lock LoopDocumento5 pagineFM - PM Demodulation - The Phase Lock LoopSunit Kumar Sharma100% (1)

- Two Stage Op-AmpDocumento4 pagineTwo Stage Op-AmpShreerama Samartha G BhattaNessuna valutazione finora

- Study On Equalizers: Anik Sengupta Sohom DasDocumento11 pagineStudy On Equalizers: Anik Sengupta Sohom DasAnikSenguptaNessuna valutazione finora

- Cmos Two Stage OpamppublishedDocumento5 pagineCmos Two Stage Opamppublisheddeepak pandeyNessuna valutazione finora

- Low Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsDocumento11 pagineLow Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsIJAR JOURNALNessuna valutazione finora

- Tiq ComparatorDocumento16 pagineTiq ComparatorKuldeep GuptaNessuna valutazione finora

- Design of 12-Bit DAC Using CMOS TechnologyDocumento5 pagineDesign of 12-Bit DAC Using CMOS TechnologysanthoshNessuna valutazione finora

- Design and Simulation of LNA: (Cadence Spectre RF)Documento19 pagineDesign and Simulation of LNA: (Cadence Spectre RF)Kushal GajavellyNessuna valutazione finora

- CD-29-Doc Design and Simulation of Successive Approximation Adc in VerilogDocumento56 pagineCD-29-Doc Design and Simulation of Successive Approximation Adc in VerilogDeepak SalianNessuna valutazione finora

- Matlab 8Documento12 pagineMatlab 8M Azeem100% (1)

- Design of A Fully Differential High-Speed High-Precision AmplifierDocumento10 pagineDesign of A Fully Differential High-Speed High-Precision Amplifierkirkland1337Nessuna valutazione finora

- Ee 215 ADocumento8 pagineEe 215 AArjun Singhal100% (1)

- High Speed Vlsi DesignDocumento93 pagineHigh Speed Vlsi DesignDr Narayana Swamy RamaiahNessuna valutazione finora

- A 4.596 GHZ, High Slew Rate, Ultra Low PowerDocumento6 pagineA 4.596 GHZ, High Slew Rate, Ultra Low PowerAlberto DanNessuna valutazione finora

- Self Biased High Performance Folded Cascode Cmos OpampDocumento6 pagineSelf Biased High Performance Folded Cascode Cmos OpampArvind MishraNessuna valutazione finora

- Low Voltage CMOS SAR ADC DesignDocumento68 pagineLow Voltage CMOS SAR ADC DesignAyush SukaniNessuna valutazione finora

- Two-Stage CMOS Op-Amp Circuit Design - Jianfeng SunDocumento17 pagineTwo-Stage CMOS Op-Amp Circuit Design - Jianfeng Sunjianfeng sun100% (2)

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceDocumento8 paginePerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceAnonymous kw8Yrp0R5r100% (1)

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocumento4 pagineA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinNessuna valutazione finora

- CMOS CM & Biasing CircuitsDocumento50 pagineCMOS CM & Biasing Circuitsabhi_jNessuna valutazione finora

- 9086 CMOS Analog Design Chapter 6Documento24 pagine9086 CMOS Analog Design Chapter 6Yogindr SinghNessuna valutazione finora

- LC Ladder Matching NetworksDocumento33 pagineLC Ladder Matching NetworksCarriceiros TourNessuna valutazione finora

- Ibis Switch ModelingDocumento122 pagineIbis Switch ModelingteomondoNessuna valutazione finora

- Signal Integrity in The Real WorldDocumento52 pagineSignal Integrity in The Real WorldpatarinwNessuna valutazione finora

- Ese570 Mos Theory p206Documento41 pagineEse570 Mos Theory p206premkumar8719Nessuna valutazione finora

- Chapter-3 Wideband AmplifierDocumento113 pagineChapter-3 Wideband AmplifierTanya Srivastava100% (3)

- Fully Differential Amplifier Design2Documento76 pagineFully Differential Amplifier Design2dragos_bondNessuna valutazione finora

- Lect08 GM ID Sizing MethodDocumento55 pagineLect08 GM ID Sizing MethodAmith NayakNessuna valutazione finora

- GM Vs Id Design FlowDocumento5 pagineGM Vs Id Design Flowapi-19755952Nessuna valutazione finora

- Recommendations For Port Setup When Using ADS Momentum and Modelithics ModelsDocumento7 pagineRecommendations For Port Setup When Using ADS Momentum and Modelithics ModelsConteNessuna valutazione finora

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDocumento5 pagineDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezNessuna valutazione finora

- CMFB DesignDocumento4 pagineCMFB Designaminkhan83Nessuna valutazione finora

- TRANSMISSION LINES JNTUK Question BankDocumento5 pagineTRANSMISSION LINES JNTUK Question BankMunni 1123Nessuna valutazione finora

- Analysis of Sense Amplifier Circuit Used in High Performance & Low Power SramDocumento5 pagineAnalysis of Sense Amplifier Circuit Used in High Performance & Low Power SramGJESRNessuna valutazione finora

- Design and Analysis of Low Power Bandgap Voltage ReferenceDocumento8 pagineDesign and Analysis of Low Power Bandgap Voltage ReferencePraveen Kumar ReddyNessuna valutazione finora

- Eric Thesis SlidesDocumento43 pagineEric Thesis SlidesHumberto JuniorNessuna valutazione finora

- Design of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFDocumento6 pagineDesign of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFWestern777Nessuna valutazione finora

- OTA DesignDocumento18 pagineOTA DesignAnandNessuna valutazione finora

- Millimicrosecond Pulse Techniques: International Series of Monographs on Electronics and InstrumentationDa EverandMillimicrosecond Pulse Techniques: International Series of Monographs on Electronics and InstrumentationNessuna valutazione finora

- A. CHANDRA-Cap. Bank DesigningDocumento5 pagineA. CHANDRA-Cap. Bank Designingluizwillcox100% (2)

- Application Note XC9572XLDocumento6 pagineApplication Note XC9572XLSidharth ChaturvedyNessuna valutazione finora

- 15A99301 Basic Electrical and Electronics EngineeringDocumento1 pagina15A99301 Basic Electrical and Electronics EngineeringjagadeeshNessuna valutazione finora

- BMD101 PDFDocumento14 pagineBMD101 PDFrajNessuna valutazione finora

- Cpc1020N: 30V Normally-Open Single-Pole 4-Pin Sop Optomos RelayDocumento6 pagineCpc1020N: 30V Normally-Open Single-Pole 4-Pin Sop Optomos RelayLuis SandovalNessuna valutazione finora

- IC TESTING - DCAClab BlogDocumento5 pagineIC TESTING - DCAClab BlogshafieeNessuna valutazione finora

- 01 - Sol Gel CuZro2Documento5 pagine01 - Sol Gel CuZro2myalemusNessuna valutazione finora

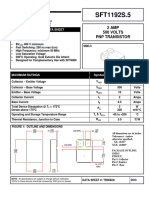

- SFT1192S.5: Solid State Devices, IncDocumento2 pagineSFT1192S.5: Solid State Devices, IncIPUNK PURNOMONessuna valutazione finora

- List of Iec StandardDocumento3 pagineList of Iec Standardanjes1Nessuna valutazione finora

- Lab 6Documento5 pagineLab 6Stephen BridgesNessuna valutazione finora

- Microfabrication, Microstructures and Microsystems: 3.3 Rapid PrototypingDocumento20 pagineMicrofabrication, Microstructures and Microsystems: 3.3 Rapid PrototypingDinesh KumarNessuna valutazione finora

- Transformer Inrush Currents and Protection 2603 003 A00Documento4 pagineTransformer Inrush Currents and Protection 2603 003 A00Joshi DhvanitNessuna valutazione finora

- Preset Counters Electronic: 2 Presets, Totalizer and Batch Counter Display LED, 8-Digits, ProgrammableDocumento4 paginePreset Counters Electronic: 2 Presets, Totalizer and Batch Counter Display LED, 8-Digits, Programmablenabil160874Nessuna valutazione finora

- Pid TS101Documento30 paginePid TS101Victor YosafatNessuna valutazione finora

- Automotive Digital Clock Ic: DescriptionDocumento7 pagineAutomotive Digital Clock Ic: DescriptionppanagosNessuna valutazione finora

- Poster Template PortraitDocumento1 paginaPoster Template PortraitTuanito NguyenNessuna valutazione finora

- Altistart 48 - ATS48C32QDocumento5 pagineAltistart 48 - ATS48C32Qabdur rafayNessuna valutazione finora

- Project of Analog and Digital Communication SystemDocumento8 pagineProject of Analog and Digital Communication SystemsohaibNessuna valutazione finora

- Long-Tail Pair Transistor Circuit: Sheet 1 of 7Documento7 pagineLong-Tail Pair Transistor Circuit: Sheet 1 of 7karan007_mNessuna valutazione finora

- HuanYang 400Hz Setup PDFDocumento71 pagineHuanYang 400Hz Setup PDFRadovan KnezevicNessuna valutazione finora

- 35kW Active Rectifier PDFDocumento6 pagine35kW Active Rectifier PDFKashifNessuna valutazione finora

- The Solder Paste Printing Process: Critical Parameters, Defect Scenarios, Specifications, and Cost ReductionDocumento14 pagineThe Solder Paste Printing Process: Critical Parameters, Defect Scenarios, Specifications, and Cost ReductionNurul KhomariyahNessuna valutazione finora

- Lecture13 Chapter4 BoostandBuckBoost CCM Analysis-1Documento22 pagineLecture13 Chapter4 BoostandBuckBoost CCM Analysis-1Buridi JahnaviNessuna valutazione finora

- Count Down CounterDocumento2 pagineCount Down CounterJose GarciaNessuna valutazione finora

- Real-Time Monitoring and Capture of Power System Transients D. F. Peelo, F. Rahmatian, M. Nagpal, and D. SYDOR Consultant, Quanta Technology, and BC Hydro CanadaDocumento8 pagineReal-Time Monitoring and Capture of Power System Transients D. F. Peelo, F. Rahmatian, M. Nagpal, and D. SYDOR Consultant, Quanta Technology, and BC Hydro CanadaDycha Kent TuckyNessuna valutazione finora

- 62nd ECTC Advance ProgramDocumento32 pagine62nd ECTC Advance Programmuh9904Nessuna valutazione finora

- Exam Questions-Section 1Documento38 pagineExam Questions-Section 1Gecca VergaraNessuna valutazione finora

- Yx 360 TRDocumento14 pagineYx 360 TRNovian ArmaNessuna valutazione finora

- Experiment 8Documento7 pagineExperiment 8anjujobin24Nessuna valutazione finora

- Presentazione Definitiva Uis TestDocumento23 paginePresentazione Definitiva Uis TestDavideNessuna valutazione finora