Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Characteristics of The NMOS Inverter: Experiment 11 MOSFET Logic Circuits

Caricato da

Minimol RajTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Characteristics of The NMOS Inverter: Experiment 11 MOSFET Logic Circuits

Caricato da

Minimol RajCopyright:

Formati disponibili

ECE322 Lab 11

Experiment 11 MOSFET Logic Circuits

Fall 2002 Holland

Goal: Obtain the transfer characteristic of MOS inverters and study the characteristics of some MOS logic circuits. 1 1.1

Characteristics of the NMOS Inverter

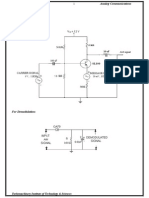

NMOS Inverter with Ohmic Load

1. Connect the NMOS inverter circuit with an ohmic load as shown in Fig. 1. Use an NMOS transistor from the MOS transistor array CD 4007 (Fig. 6). Make sure Pin 7 is connected to ground and Pin 14 connected to 5V. 2. Apply a low-frequency (100Hz) triangular voltage with a peak-to-peak voltage of 0 to 5V, (adjust offset) to the input of the inverter. 3. Using the X-Y mode of the oscilloscope, observe and sketch the transfer characteristic of the inverter. Adjust the frequency to avoid any hysteresis effect. 4. Measure all voltage levels and in particular the voltages corresponding to logic 1and 0. If necessary, use the waveforms in the X-t mode. 5. Calculate the values of VOH, VOL, VIL, and VIH of the gate. 6. Calculate the noise margins NMH and NML.

Figure 1 NMOS Inverter with R load

1.2

NMOS Inverter with Constant-current Load

1. Connect the inverter circuit as shown in Fig. 2. The connection of gate and drain together forces the load transistor Q2 to operate in the constant current region. 2. Apply a low-frequency (100Hz) triangular voltage with a peak-to-peak voltage of 0 to 5V, (adjust offset) to the input of the inverter. 3. Using the X-Y mode of the oscilloscope, observe and sketch the transfer characteristic of the inverter. Adjust the frequency to avoid any hysteresis effect. 4. Measure all voltage levels and in particular the voltages corresponding to logic 1and 0. If necessary, use the waveforms in the X-t mode. 5. Calculate the values of VOH, VOL, VIL, and VIH of the gate. 6. Calculate the noise margins NMH and NML. C:\Rod\NDSU\EE322\Lab11\ECE322lab11.doc 1 of 4

ECE322 Lab 11

Experiment 11 MOSFET Logic Circuits

Fall 2002 Holland

Figure 2 NMOS Inverter with CC load

CMOS Inverter

1. Connect the CMOS inverter circuit as shown in Fig. 3. 2. Apply a low-frequency (100Hz) triangular voltage with a peak to peak voltage of 0 to 5V, (adjust offset) to the input of the inverter. 3. Using the X-Y mode of the oscilloscope, observe and sketch the transfer characteristic of the inverter. Adjust the frequency to avoid any hysteresis effect. 4. Measure all voltage levels and in particular the voltages corresponding to logic 1and 0. If necessary, use the waveforms in the X-t mode. 5. Under Step 4, observe and sketch the waveform of the current drawn by the gate. This can be done by adding a very small resistance between the source of Q1 and the supply ground. The voltage across this resistance is proportional to the drain current. 6. Calculate the values of VOH, VOL, VIL, and VIH of the gate. 7. Calculate the noise margins NMH and NML.

Figure 3 CMOS inverter

C:\Rod\NDSU\EE322\Lab11\ECE322lab11.doc 2 of 4

ECE322 Lab 11

Experiment 11 MOSFET Logic Circuits

Fall 2002 Holland

3

3.1

CMOS Logic

NAND Gate

1. Selecting MOSFETs from the CD 4007 array, connect the circuit of the CMOS NAND circuit as shown in Fig. 4. 2. Verify the truth table for the logic circuit. Also check the condition of all four transistors. Indicate whether each device is ON (Ohmic) or ON (Constant Current) or OFF. 3. Tie both the inputs together and obtain the transfer characteristic. 4. Measure the voltage levels for logic 1 and logic 0. 5. Sketch the transfer characteristic. 6. Calculate the values of NMH and NML. 7. Comment on the power dissipated by the CMOS gate.

Figure 4 CMOS NAND gate

3.2

NOR Gate

1. Connect the circuit of the two-input NOR gate as shown in Fig. 5. 2. Verify the truth table for the logic circuit. Also check the condition of all four transistors. Indicate whether each device is ON (Ohmic) or ON (Constant Current) or OFF. 3. Tie both the inputs together and obtain the transfer characteristic. 4. Measure the voltage levels for logic 1 and logic 0. 5. Sketch the transfer characteristic. 6. Calculate the values of NMH and NML. 7. Comment on the power dissipated by the CMOS gate.

C:\Rod\NDSU\EE322\Lab11\ECE322lab11.doc 3 of 4

ECE322 Lab 11

Experiment 11 MOSFET Logic Circuits

Fall 2002 Holland

Figure 5 CMOS NOR gate

Figure 6 Layout diagram of CD 4007

Note: Make sure Pin 7 is connected to the lowest potential (Ground) and Pin 14 is connected to the highest potential (VDD) for any circuit built using this IC.

C:\Rod\NDSU\EE322\Lab11\ECE322lab11.doc 4 of 4

Potrebbero piacerti anche

- Locating Faults AG en US1Documento3 pagineLocating Faults AG en US1Neelakandan MasilamaniNessuna valutazione finora

- Solved Problems: EE160: Analog and Digital CommunicationsDocumento145 pagineSolved Problems: EE160: Analog and Digital CommunicationsZoryel Montano33% (3)

- Solved Problems: EE160: Analog and Digital CommunicationsDocumento145 pagineSolved Problems: EE160: Analog and Digital CommunicationsZoryel Montano33% (3)

- Basic Insulation & Power Factor Theory ExplainedDocumento17 pagineBasic Insulation & Power Factor Theory ExplainedNeelakandan Masilamani100% (2)

- T. Henry Moray Device Generates Free EnergyDocumento9 pagineT. Henry Moray Device Generates Free Energyrocism01100% (1)

- Commissioning of DAVRDocumento70 pagineCommissioning of DAVRPMG Bhuswal Project100% (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Da EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Valutazione: 4.5 su 5 stelle4.5/5 (3)

- Digital Electronics Lab Experiments on Transistor Switches, Logic Gates and CharacteristicsDocumento37 pagineDigital Electronics Lab Experiments on Transistor Switches, Logic Gates and CharacteristicsKishore ReddyNessuna valutazione finora

- VLSILABVVVVIMPDocumento19 pagineVLSILABVVVVIMPGirija M HegdeNessuna valutazione finora

- EXP6Documento10 pagineEXP6fatih_ealNessuna valutazione finora

- Astable CircuitsDocumento9 pagineAstable CircuitsRavindranath ShrivastavaNessuna valutazione finora

- Characterization of TTLDocumento15 pagineCharacterization of TTLYellasiri SureshNessuna valutazione finora

- EESB423 Sem1 1314 Assignment2Documento3 pagineEESB423 Sem1 1314 Assignment2Shamraj KunnasagarNessuna valutazione finora

- 3ECE-AC Lab ManualDocumento62 pagine3ECE-AC Lab ManualShannon DunnNessuna valutazione finora

- DLC LAB - 08 - Student - ManualDocumento10 pagineDLC LAB - 08 - Student - ManualImtiaj SajinNessuna valutazione finora

- High OH IH LOW IL OL: SS DDDocumento3 pagineHigh OH IH LOW IL OL: SS DDTALLANessuna valutazione finora

- CMOS Logic Gates and Switch DesignDocumento34 pagineCMOS Logic Gates and Switch DesignsahithikocharlakotaNessuna valutazione finora

- Lab Manual - 32050502 - Digital ElectronicsDocumento31 pagineLab Manual - 32050502 - Digital ElectronicsFoad alzhraniNessuna valutazione finora

- CMOS Inverter Layout SimulationDocumento10 pagineCMOS Inverter Layout SimulationVinny VenizNessuna valutazione finora

- I. Instructional Objectives: D S G D GDocumento4 pagineI. Instructional Objectives: D S G D Gcokelat_kNessuna valutazione finora

- Lab1 Tranzistoare EngDocumento11 pagineLab1 Tranzistoare Engtoufik bendibNessuna valutazione finora

- VLSI 100 QuestionsDocumento2 pagineVLSI 100 QuestionsAman BatraNessuna valutazione finora

- Vlsi Questions-2Documento8 pagineVlsi Questions-2Chinu SoodNessuna valutazione finora

- Assignment 1Documento1 paginaAssignment 1Radha KuraNessuna valutazione finora

- SPICE Lab ExperimentsDocumento59 pagineSPICE Lab ExperimentsAviral VarshneyNessuna valutazione finora

- VLSI 100 QuestionsDocumento4 pagineVLSI 100 Questionsapi-3824368Nessuna valutazione finora

- Anallysis and Design of Analog Integrated Circuits QuestionsDocumento5 pagineAnallysis and Design of Analog Integrated Circuits QuestionsshankarNessuna valutazione finora

- Analog IC Design Viva Questions SummaryDocumento2 pagineAnalog IC Design Viva Questions Summarylucky jNessuna valutazione finora

- 20EC01016 Lab2Documento10 pagine20EC01016 Lab2Speed SystemNessuna valutazione finora

- Silicon Wafer (Substrate) Preparation 2. Epitaxial Growth 3. Oxidation 4. Photolithography 5. Diffusion 6. Ion Implantation 7. Isolation Techniques 8. MetallizationDocumento21 pagineSilicon Wafer (Substrate) Preparation 2. Epitaxial Growth 3. Oxidation 4. Photolithography 5. Diffusion 6. Ion Implantation 7. Isolation Techniques 8. MetallizationMangaiyarkarasi VengatachalamNessuna valutazione finora

- Characteristics and Compensation of ServomotorsDocumento46 pagineCharacteristics and Compensation of Servomotorsabixek100% (2)

- Lab3 - MOSFET IV CharacteristicDocumento11 pagineLab3 - MOSFET IV Characteristickzankz100% (1)

- Experiment 5 - Inverter CharacteristicsDocumento7 pagineExperiment 5 - Inverter CharacteristicsGowtham SpNessuna valutazione finora

- General Instructions To The CandidateDocumento4 pagineGeneral Instructions To The Candidateapurv shuklaNessuna valutazione finora

- EMF and MMF MethodDocumento6 pagineEMF and MMF MethodBritto Tiger100% (2)

- ESE 324 Electronics Lab Phase Detector DesignDocumento9 pagineESE 324 Electronics Lab Phase Detector DesignRaman SinghNessuna valutazione finora

- Vlsi Question Paper 2Documento3 pagineVlsi Question Paper 2Chinu SoodNessuna valutazione finora

- Ee 501 Project2 ReportDocumento15 pagineEe 501 Project2 Reportapi-626683514Nessuna valutazione finora

- Homework #6: EE 209: Fall 2017Documento2 pagineHomework #6: EE 209: Fall 2017Mahmoud SalamaNessuna valutazione finora

- LabbDocumento35 pagineLabbGowtham SpNessuna valutazione finora

- LIC Question Bank 2021 - LevelsDocumento12 pagineLIC Question Bank 2021 - LevelsPavan ParthikNessuna valutazione finora

- 11 Chapter03 PDFDocumento13 pagine11 Chapter03 PDFAtulNessuna valutazione finora

- Device Lab Report 10 PDFDocumento6 pagineDevice Lab Report 10 PDFScribble RiYaDNessuna valutazione finora

- Laboratory Exercise 4 Digital Integrated Circuit CMOS: The Aim of The ExerciseDocumento4 pagineLaboratory Exercise 4 Digital Integrated Circuit CMOS: The Aim of The ExerciseRoshdy AbdelRassoulNessuna valutazione finora

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Documento16 pagineApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaNessuna valutazione finora

- Circuit Diagram:: Turbomachinery Institute of Technology & SciencesDocumento59 pagineCircuit Diagram:: Turbomachinery Institute of Technology & SciencesSubhashini MurugesanNessuna valutazione finora

- Ebook - Electronics Explained - Transistor CircuitsDocumento11 pagineEbook - Electronics Explained - Transistor CircuitsDhuvi LuvioNessuna valutazione finora

- Lab ManualDocumento38 pagineLab ManualsruharithaNessuna valutazione finora

- SiC power devices advantagesDocumento9 pagineSiC power devices advantages20EUEE053- MADHUBALAN.SNessuna valutazione finora

- Vsli Unit 2 Question Bank With AnswersDocumento10 pagineVsli Unit 2 Question Bank With AnswersPavani NNessuna valutazione finora

- Experiment No. 3: Characteristics of CMOS InverterDocumento6 pagineExperiment No. 3: Characteristics of CMOS Inverterselvi0412Nessuna valutazione finora

- ECE2274 Pre-Lab For MOSFET Logic NAND Gate, NOR Gate, and CMOS Inverter 1. Nmos Nand GateDocumento6 pagineECE2274 Pre-Lab For MOSFET Logic NAND Gate, NOR Gate, and CMOS Inverter 1. Nmos Nand GateRudra MishraNessuna valutazione finora

- Study of Clamping CircuitsDocumento4 pagineStudy of Clamping Circuitsh9emanth4Nessuna valutazione finora

- Ec2405 - Optical and Microwave Laboratory (Manual)Documento32 pagineEc2405 - Optical and Microwave Laboratory (Manual)Jonathan SheltonNessuna valutazione finora

- Nand 2 Nor 2Documento19 pagineNand 2 Nor 2Nagendra BoyellaNessuna valutazione finora

- Ec3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopDocumento2 pagineEc3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopGamer AnonymousNessuna valutazione finora

- Labreport ThreeDocumento8 pagineLabreport ThreeTeshome GirmaNessuna valutazione finora

- UNIT-3 Gate Level Design NotesDocumento22 pagineUNIT-3 Gate Level Design NotesPallavi Ch100% (2)

- Unit-3 - Function Generator Using IC 8038Documento10 pagineUnit-3 - Function Generator Using IC 8038yp2401553Nessuna valutazione finora

- Assignment 2Documento5 pagineAssignment 2Haribabu VeludandiNessuna valutazione finora

- AC Lab Oscilloscope Rev03Documento8 pagineAC Lab Oscilloscope Rev03Abdelaziz AbdoNessuna valutazione finora

- EE 528 Modelling and Analysis of Electrical MachinesDocumento3 pagineEE 528 Modelling and Analysis of Electrical MachinesKuldeepNessuna valutazione finora

- Hilbert Transformer: Dr. Salahedin RehanDocumento11 pagineHilbert Transformer: Dr. Salahedin RehanMinimol RajNessuna valutazione finora

- Ipv 6Documento20 pagineIpv 6Minimol RajNessuna valutazione finora

- Mobile Communications Chapter: Wireless Systems OverviewDocumento52 pagineMobile Communications Chapter: Wireless Systems OverviewMinimol RajNessuna valutazione finora

- Jemh 108Documento22 pagineJemh 108ahmadomar89Nessuna valutazione finora

- Thecellularconcept 130227020319Documento28 pagineThecellularconcept 130227020319yarmeenaNessuna valutazione finora

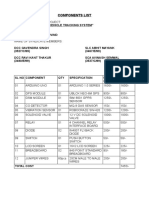

- COMPONENTS (1) .OdtDocumento2 pagineCOMPONENTS (1) .OdtMinimol RajNessuna valutazione finora

- Ktu Students: For More Study Materials WWW - Ktustudents.inDocumento14 pagineKtu Students: For More Study Materials WWW - Ktustudents.inMinimol RajNessuna valutazione finora

- Link Layer: Computer Networking: A Top Down ApproachDocumento97 pagineLink Layer: Computer Networking: A Top Down ApproachMinimol RajNessuna valutazione finora

- Satellite CommunicationDocumento63 pagineSatellite CommunicationMinimol RajNessuna valutazione finora

- Ships Classification Basing On Acoustic SignaturesDocumento14 pagineShips Classification Basing On Acoustic SignaturesMinimol RajNessuna valutazione finora

- Analog Communication Engineering EC S4 B.Tech KTU 2017Documento2 pagineAnalog Communication Engineering EC S4 B.Tech KTU 2017Minimol RajNessuna valutazione finora

- Ultrasonic Distance Measurer KIT Experimental ManualDocumento8 pagineUltrasonic Distance Measurer KIT Experimental ManualMinimol RajNessuna valutazione finora

- Design and Analysis of Band Pass Fir Filter Using Different Window Techniques IJERTV3IS20288Documento6 pagineDesign and Analysis of Band Pass Fir Filter Using Different Window Techniques IJERTV3IS20288Minimol RajNessuna valutazione finora

- AnswersComputer Networks 159334 Assignment 1 2010Documento12 pagineAnswersComputer Networks 159334 Assignment 1 2010Zulkarnain Zainal100% (1)

- Relaible CommunicationDocumento20 pagineRelaible CommunicationMinimol RajNessuna valutazione finora

- PHD Syllabus: Department of Electronics and CommunicationDocumento1 paginaPHD Syllabus: Department of Electronics and CommunicationMinimol RajNessuna valutazione finora

- BE2101 - Basic Electronics: (1 Semester - CS, IT) Credits: 3 Contact Hours: 3Documento3 pagineBE2101 - Basic Electronics: (1 Semester - CS, IT) Credits: 3 Contact Hours: 3Minimol RajNessuna valutazione finora

- Chapter 21 SOLUTIONS Practice Problems PDFDocumento2 pagineChapter 21 SOLUTIONS Practice Problems PDFdzulfikarNessuna valutazione finora

- Brocecure of Seminar Vlsi FinalDocumento3 pagineBrocecure of Seminar Vlsi FinalMinimol RajNessuna valutazione finora

- ENTC 3320 555 Timer Operation and ApplicationsDocumento20 pagineENTC 3320 555 Timer Operation and ApplicationsMinimol RajNessuna valutazione finora

- Introduction To Computers and Windows Operating Systems Set 1 - BitsofcomputerDocumento7 pagineIntroduction To Computers and Windows Operating Systems Set 1 - BitsofcomputerMamatha Mantena100% (1)

- Study PAM Generation and CharacteristicsDocumento9 pagineStudy PAM Generation and CharacteristicsGaurav Kumar GoyalNessuna valutazione finora

- PPT RE2-introductionDocumento23 paginePPT RE2-introductionLutfyNessuna valutazione finora

- CS11002Documento1 paginaCS11002Rinaldy67% (3)

- SMI Confidential: SM3267 Test Program and ISP Release NoteDocumento3 pagineSMI Confidential: SM3267 Test Program and ISP Release NoteRaul Trujillo PNessuna valutazione finora

- AN944-1 Microwave Transistor Bias ConsiderationsDocumento11 pagineAN944-1 Microwave Transistor Bias ConsiderationsCharles FarhleyNessuna valutazione finora

- R8563C Kitz 204Documento64 pagineR8563C Kitz 204Rinda_Rayna100% (1)

- Vs 85hfrseriesDocumento10 pagineVs 85hfrserieskhaled shboulNessuna valutazione finora

- Kaneyuki Kurokawa Received A B.S. Degree in Electrical Engineering in 1951 and A Ph.D. DegreeDocumento2 pagineKaneyuki Kurokawa Received A B.S. Degree in Electrical Engineering in 1951 and A Ph.D. DegreethgnguyenNessuna valutazione finora

- (Codientu - Org) - (Codientu - Org) - AV 21F7 mn1873287 nn5198kDocumento10 pagine(Codientu - Org) - (Codientu - Org) - AV 21F7 mn1873287 nn5198kGioVoTamNessuna valutazione finora

- BAV16W/1N4148W Features Mechanical Data: Surface Mount Fast Switching DiodeDocumento5 pagineBAV16W/1N4148W Features Mechanical Data: Surface Mount Fast Switching DiodeshareatorNessuna valutazione finora

- P72x - EN T - C21 - V11DDocumento334 pagineP72x - EN T - C21 - V11DTlili MahmoudiNessuna valutazione finora

- Ch-1 Adv Optical Fiber CommDocumento15 pagineCh-1 Adv Optical Fiber CommZain HamzaNessuna valutazione finora

- Quick Charge Device List PDFDocumento20 pagineQuick Charge Device List PDFEnoNessuna valutazione finora

- Chapter 11 Lecture PowerPointDocumento45 pagineChapter 11 Lecture PowerPointMaritess CationNessuna valutazione finora

- BT136FDocumento7 pagineBT136FMiloud ChouguiNessuna valutazione finora

- Mitsubishi 7-Unit 400mA Darlington Transistor ArrayDocumento4 pagineMitsubishi 7-Unit 400mA Darlington Transistor ArrayRomi KabelNessuna valutazione finora

- HSPICE Tutorial PDFDocumento7 pagineHSPICE Tutorial PDFXman-exNessuna valutazione finora

- BoardSet v160522Documento2 pagineBoardSet v160522Pepe CastilloNessuna valutazione finora

- A New Physical Design Flow For A Selective State Retention Based ApproachDocumento15 pagineA New Physical Design Flow For A Selective State Retention Based ApproachJoseph HuangNessuna valutazione finora

- Auto Recloser GEDocumento36 pagineAuto Recloser GERamzan QureshiNessuna valutazione finora

- Catalog Power Ind Oct-11Documento44 pagineCatalog Power Ind Oct-11Suraj MohapatraNessuna valutazione finora

- Pasco Microwave Optics WA-9314BDocumento54 paginePasco Microwave Optics WA-9314BJoaquin Casanova50% (2)

- EPB ManualDocumento86 pagineEPB ManualMohamed BnNessuna valutazione finora

- IQ CorrectionDocumento1 paginaIQ Correctionsrinivasnaik1989Nessuna valutazione finora

- TM 11 1520 221 34Documento122 pagineTM 11 1520 221 34Tod A. WulffNessuna valutazione finora

- 2014-Green-The Emergence of Perovskite Solar CellsDocumento10 pagine2014-Green-The Emergence of Perovskite Solar CellsChris VilaNessuna valutazione finora