Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Modulo de Captura de Entrada

Caricato da

Edu Pollo RomCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Modulo de Captura de Entrada

Caricato da

Edu Pollo RomCopyright:

Formati disponibili

ITSS MODULO DE CAPTURA DE ENTRADA

MODULO DE CAPTURA DE ENTRADA Eduardo Luis Romero Len e-mail: edurom.pollo@hotmail.com

RESUMEN: El funcionamiento de las puertas de entrada y salida de un dsPic30F y todos sus registros

Significado de los bits del registro de control IxCON: Bit 15-14 No se implementa: se lee como 0 Bit 13 ICSIDL: 1= el modulo se detiene en modo Idle 0= el modulo continua operando en modo Idle Bits 12-8 No se implementa: se lee como 0 Bits 7 ICTMR: 1= se utiliza el timer 2 0= se utiliza el timer 3 Bits 6-5 ICI<1:0>: 11=interrupcin cada 4 eventos de captura 10=interrupcin cada3 eventos de captura 01=interrupcin cada2 eventos de captura 00=interrupcin cada vez que se produce un evento Bits 4 ICOV: 1=existe sobrepasamiento 0= no hay sobrepasamiento Bits 3 ICOV: Bit que indico si el buffer no esta vacio Con el bit 1 o si esta vaco(el bit se pone 0) Bits 2-0 Bits que selecciona el modo d captura de entrada 111= el modulo funciona como patita de interrupcion 110= no se utiliza (modulo desabilitado) 101= modo captura de 16 flanco ascendentes 100= modo captura de 4 flanco ascendentes 011= modo captura cada flanco ascendentes 010= modo captura cada flanco ascendentes 001= modo captura, en todos los flancos (ascendentes y descendentes) 000= para desconectar el modulo de captura de entrada 2.3 SELECCIN DEL TIMER El modulo de captura de entrada puede tener hasta 8 canales de captura y cada canal puede seleccionar uno de los dos temporizadores como base de tiempos (TIMER2 o TIMER3) La eleccin del temporizador se lleva a cabo a travs del bit de control ICTMR (ICxCON<7>). 2.4 MODOS DE CAPTURA DE EVENTOS DE ENTRADA El modulo de captura de entrada lee un valor de 16bits de la base de tiempos elegida cuando se produce un evento pre programado en la patita ICx, pueden ser de 3 categoras 1. Modo ce captura simple En flanco ascendente de entrada en el pin ICx En flanco descendente de entrada en el pin ICx 2. Captura del valor del temporizador con cada flanco (ascendente y descendente)

1. INTRODUCCIN

El tiempo se controla con una de las dos bases de tiempos posibles (Timer 2 o Timer 3). Las posibilidades del modulo de captura de entrada son muy utilizadas en aplicaciones que se requieran control de frecuencia y medida de pulsos, as como en fuentes adicinales de interrupciones externas. Las caractersticas operacionales principales son: Modo simple de captura de eventos. Seleccin como base de tiempos al temporizador 2 (Timer 2) o al temporizador 3 (Timer 3). Interrupciones provocadas por eventos de captura de entrada. Los modos de trabajo son: Modo captura del temporizador por flanco descendente de entrada en la patita ICx. Modo captura del valor del temporizador con cada flanco ascendente de entrada en la patita ICx. Modo captura cada 4 flancos ascendentes en ICx. Modo captura con cada flanco ascendente y descendente en ICx.

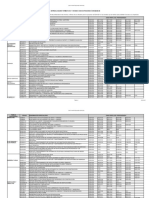

2. REGISTROS DE CAPTURA DE ENTRADA

1. 2. ICxCON: Registro de Control de Captura de Entrada. ICxBUF: Registro Buffer de Captura de Entrada.

Byte de mas peso:

U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0

ICSIDL

Byte de menos peso:

R/W-0 R/W-0 R/W-0 R-0, HC R-0, HC R/W-0 R/W-0 R/W-0

ICTMR

ICI<1:0>

ICOV

ICBNE

ICM<2:0>

Fig1. IxCON: Registro de Control de Captura de Entrada.

HC= Borrado en hardware. HS= Establecido en hardware. R=Leible W=Escribible U=bit no implementado, se lee como 0

ITSS MODULO DE CAPTURA DE ENTRADA

2.4.1

Cada 4 flancos ascendentes de entrada en el pin ICx Cada 16 flancos descendentes de entrada en el pin ICx MODO DE CAPTURA SIMPLE

Establece el flag de interrupcin en captura de entrada (ICxIF) con cada ascendente y descendente Los bits de interrupcin del modo captura No se genera el bit de sobre pasamiento 2.5 OPERACIN CAPTURA DEL BUFFER DE

El modulo de captura puede recoger el valor del temporizador seleccionado (TIMER2 o TIMER3) en el flanco prederminado (ascendente y descendente, segn este definido por el modo) de la seal estrada aplicada en la patita ICx. La lgica de captura de entrada detecta y sincroniza el flanco ascendente o descendente de la seal en la patita correspondiente. Cuando el numero de eventos capturados coincide con el numero especificado en los bits de control ICI<1:0>se activa el respectivo flag de estado de la interrupcin del canal der captura (ICSI), pero se produce 2 ciclos de instruccin despus 2.4.2 PREDIVISOR DE CAPTURA DE EVEVTOS

Cada canal de captura tiene un buffer tipo FIFO asociado que dispone de 4 palabras de 16 bits. El registro ICxBUF es el registro buffer visible por el usuario y esta mapeado en memoria. Despus de un reset ICM<210>=000 el modulo har y esta mapeado en memoria. Borra el flag de condicin de sobre pasamiento o desbordamiento Resetear el buffer de captura Si se lee el buffer FUIFO bajo las siguientes condiciones, se puede producir resultado indeterminado: En el caso en el que el modulo de captura se deshabilita y despus d un tiempo se vuelve a habilitar Cuando se hace una lectura del FIFO cuando el buffer esta vaco Despus de un resett Hay dos bits del registro de control de estado ICBNE(ICxCON<3>): buffer de captura de entrada lleno ICOV(ICxCON<4>): hay sobre pasamiento 2.5.1 ICBNE

E modulo de captura admite dos modos de trabajo del predivisor. Los modos se seleccionan poniendo los bits registro ICI<2:>(ICxCON<1:2>) a100 o 101, respectivamente. En estos modos se cuentan 4 o 16 flancos ascendentes antes de capturar el evento. Cuando se cambia ;la configuracin de un tipo de predivisor a otro se puede generar una interrupcin. El contador predivisor no se borrada, por lo que la primera captura debe proceder desde un predivisor distinto de 0 PROGRAMA EJEMPLOS El cdigo del ejemplo 1 elige el modulo 1 de captura de entrada, realiza la captura en el cuarto flanco ascendente y selecciona como base de tiempos el TIMER2. Para evitar interrupciones inesperadas borra el registro ICxCON. BSET IPCO, #ICI1IP0 BCLR IPCO, #ICI1IP1 BCLR IPCO, #ICI1IP2 BCLR IPCO, #ICI1IF BSET IPCO, #ICI1IE CLR IC1CON MOV #0x00A2, W0 MOV W0, IC1CON MOV #IC1BUF, W0 MOV TEMP_BUFF, W1 2.4.3 MODO DETECCION DE FLANCO

Bit que indica que el buffer de captura esta lleno. El bit de control de solo lectura ICBNE se activa con el primer evento de captura de entrada y continua mantenindose hasta que todos los eventos hayan sido ledos del buffer de captura 2.5.2 ICON

Bit que indica sise produce sobre pasamiento. El bit de estado de solo lectura ICON se activa cuando se produce sobre pasamiento el buffer de captura para borra la condicin de sobre pasamiento, el buffer debe ser ledo 4 veces. Despus de la cuarta lectura el flag de estado ICON se borra y e; canal de captura reanuda un funcionamiento normal 2.6 INTERRUPCIONES

Es posible capturar un valor de la base de tiempos en cada flanco ascendente o descendente de la seal de entrada puesta en el pic ICx Cuando el modulo de captura de entrada se configura en modo deteccin de flanco:

Los canales de captura de entrada tiene; a capacidad de generar una interrupcin en base al numero de eventos de captura seleccionados. Este numero se establece con los bits de control, ICI<1:0>(ICxCON<6:5>) 2.6.1 BITS DE CONTROL INTERRUPCIONES DE

ITSS MODULO DE CAPTURA DE ENTRADA

Cada canal de captura debe dispone de bits para el manejo de las interrupciones (ICxIF), bits que habilitan ;a interrupcin (ICxIE) y bits de prioridad de la interrupcin(ICxIP<2:0>) 2.7 SOPORTE DE UART El modulo de captura de entrada puede usarse por el modulo UART cuando es configuracin en el modo de funcionamiento Auto baud, ABAUD=1(UxMODE<5>). El modulo de captura debe estar configurado para el modo de deteccin de flanco para poder obtener mayores ventajas de las caractersticas del Autobaud. 2.7.1 EN MODO SLEEP Cuando el dispositivo entra en modo sleep el reloj del sistema se deshabilita y el modulo de captura de entrada solo puede funcionar como una fuente de interrupcin externa este modo se deshabilita poniendo los bits de control .ICM<2:0> a111. 2.7.2 EN MODO IDLE Cuando el dispositivo entra en modo IDLE las fuentes del reloj del sistema siguen funcionado pero la CPU detiene la ejecucin del cdigo. El bit ICSIDL (ICxCON<13>) selecciona si el modulo se detiene en este modo Idle o sigue funcionando Si ICSIDL=0, el modulo continua operando en modo Idle. Se requiere que el temporizador seleccionado este habilitado mientras este activo el modo Idle Si ICSIDL=1, el modulo se detendr en el modo Idle. El modulo realiza las mismas funcione cuando esta parado tanto en el modo Idle como en el sleep. 2.7.2 LA SALIDA DE SLEEP E IDLE LOS MODOS

Un evento de captura de entrada genera una salida o <<despertar>> de los modos sleep e idle o una interrupcin 2.8 CONTROL DE LAS PATITAS DE E/S

Cuando se activa el modulo de captura el usuario debe asegurar que al direccin de la patita de E/S correspondiente esta configuracin como entrada cargando el bit de registro TRIS adecuadamente

Potrebbero piacerti anche

- Modulacion de Simple Banda LateraDocumento3 pagineModulacion de Simple Banda LateraEdu Pollo RomNessuna valutazione finora

- Memoria Flahs y Memoria EpromDocumento6 pagineMemoria Flahs y Memoria EpromEdu Pollo RomNessuna valutazione finora

- Modulo CanDocumento6 pagineModulo CanEdu Pollo RomNessuna valutazione finora

- Modulo PWM para Control de MotoresDocumento10 pagineModulo PWM para Control de MotoresEdu Pollo Rom100% (1)

- Memoria Flahs y Memoria EpromDocumento6 pagineMemoria Flahs y Memoria EpromEdu Pollo RomNessuna valutazione finora

- Resumen Relacion Señal A RuidoDocumento3 pagineResumen Relacion Señal A RuidoEdu Pollo RomNessuna valutazione finora

- Resumen Relacion Señal A RuidoDocumento3 pagineResumen Relacion Señal A RuidoEdu Pollo RomNessuna valutazione finora

- ConversoresDocumento8 pagineConversoresEdu Pollo RomNessuna valutazione finora

- Resumen Relacion Señal A RuidoDocumento3 pagineResumen Relacion Señal A RuidoEdu Pollo RomNessuna valutazione finora

- Memoria Flahs y Memoria EpromDocumento6 pagineMemoria Flahs y Memoria EpromEdu Pollo RomNessuna valutazione finora

- Capitulo 15 EduDocumento3 pagineCapitulo 15 EduEdu Pollo RomNessuna valutazione finora

- Temas Trabajo Sistemas DiscretosDocumento10 pagineTemas Trabajo Sistemas DiscretosEdu Pollo RomNessuna valutazione finora

- Interrupciones y ExcepcionesDocumento8 pagineInterrupciones y ExcepcionesEdu Pollo RomNessuna valutazione finora

- Sistemas DiscretosDocumento2 pagineSistemas DiscretosEdu Pollo RomNessuna valutazione finora

- Tarea Sistemas DiscretosDocumento2 pagineTarea Sistemas DiscretosEdu Pollo RomNessuna valutazione finora

- Ejercicio de Serie de FourierDocumento3 pagineEjercicio de Serie de FourierEdu Pollo RomNessuna valutazione finora

- Instituto Tecnologico SudamericanoDocumento6 pagineInstituto Tecnologico SudamericanoEdu Pollo RomNessuna valutazione finora

- Trabajo de Sistemas DiscretosDocumento9 pagineTrabajo de Sistemas DiscretosEdu Pollo RomNessuna valutazione finora

- INTELLIGENCE PARTNERS El Proceso de Ventas - IESE - CASODocumento11 pagineINTELLIGENCE PARTNERS El Proceso de Ventas - IESE - CASOEstefano RamirezNessuna valutazione finora

- Transmittal Envio de RFI 27 A ANDDESDocumento2 pagineTransmittal Envio de RFI 27 A ANDDESjnu6mnju6njNessuna valutazione finora

- Cómo Probar El Sensor Del CigüeñalDocumento8 pagineCómo Probar El Sensor Del CigüeñalGustavoEstradaNessuna valutazione finora

- Cómo activar Windows CMDDocumento9 pagineCómo activar Windows CMDCharly Torres IzarraNessuna valutazione finora

- Cotizacion Insuagro 2Documento1 paginaCotizacion Insuagro 2Mateo RodriguezNessuna valutazione finora

- Tarea de EPT - 9na E-A Primero 1ra ActividadDocumento7 pagineTarea de EPT - 9na E-A Primero 1ra ActividadMary Llerena anccoNessuna valutazione finora

- Formato Plan de TrabajoDocumento1 paginaFormato Plan de TrabajoMichel Gallegos OsorioNessuna valutazione finora

- Códigos ConvolucionalesDocumento4 pagineCódigos ConvolucionalesČ Põmã KârîmNessuna valutazione finora

- Práctica IperfDocumento6 paginePráctica IperfAlexander Sócola CoronelNessuna valutazione finora

- MacrocomputadorasDocumento25 pagineMacrocomputadorasKevin ManCastNessuna valutazione finora

- Todo Lo Que Debes Saber Sobre Los Valores de La Ciudadanía DigitalDocumento6 pagineTodo Lo Que Debes Saber Sobre Los Valores de La Ciudadanía DigitalAlba Soledad AlmironNessuna valutazione finora

- Estructura de Buses Compartidos para Microprocesadores Y MicrocontroladoresDocumento17 pagineEstructura de Buses Compartidos para Microprocesadores Y MicrocontroladoresMarco de SantiagoNessuna valutazione finora

- Capitulo I. Que Es La P.P.IDocumento8 pagineCapitulo I. Que Es La P.P.Ilucy janeth arboleda mosqueraNessuna valutazione finora

- Actividad - Semana - 4 Ana Milena Mesa MarinDocumento9 pagineActividad - Semana - 4 Ana Milena Mesa MarinAna Milena Mesa MarinNessuna valutazione finora

- Auditoría Complejo Deportivo UNJFSCDocumento142 pagineAuditoría Complejo Deportivo UNJFSCLuis Alberto Valerio RosasNessuna valutazione finora

- IO-Link Master EtherNet IP 8 PortsDocumento4 pagineIO-Link Master EtherNet IP 8 PortscelectricNessuna valutazione finora

- BSBXCM501 Project Portfolio - En.esDocumento15 pagineBSBXCM501 Project Portfolio - En.esMaria Paula Moreno0% (1)

- HaskellDocumento48 pagineHaskelladousmonribotNessuna valutazione finora

- Presentacion Biblioteca VirtualDocumento20 paginePresentacion Biblioteca VirtualMarcos JongueNessuna valutazione finora

- Consulta Modbus Rtu y Modelo OsiDocumento14 pagineConsulta Modbus Rtu y Modelo OsiErick LopezNessuna valutazione finora

- Taller 4 de Informática 3pDocumento9 pagineTaller 4 de Informática 3poveimarNessuna valutazione finora

- Carta de Renuncia Voluntaria Con PreavisoDocumento4 pagineCarta de Renuncia Voluntaria Con PreavisoNando Rivera SoletoNessuna valutazione finora

- CNOs Perfil Profesorado 2020-2021Documento6 pagineCNOs Perfil Profesorado 2020-20211147forNessuna valutazione finora

- Lectura 05Documento19 pagineLectura 05Enrique LlanosNessuna valutazione finora

- Cotizacion TransformadorDocumento4 pagineCotizacion TransformadorAlejandro RodriguezNessuna valutazione finora

- 6 Millones de Novatos Han Comprado Monedas en Robinhood Crypto Ya en 2021Documento6 pagine6 Millones de Novatos Han Comprado Monedas en Robinhood Crypto Ya en 2021Pedro BoxerNessuna valutazione finora

- Router OdpDocumento11 pagineRouter OdpverevereNessuna valutazione finora

- Tiempos y MovimientosDocumento4 pagineTiempos y MovimientosMostri MostriNessuna valutazione finora

- Coordinacion de MatematicaDocumento5 pagineCoordinacion de MatematicaVanessa Vallejo BureNessuna valutazione finora

- Gráfica Interactiva SIA: 1000075Documento3 pagineGráfica Interactiva SIA: 1000075Maria Camila Diaz SanchezNessuna valutazione finora