Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Head's Up: Last Week's Material Week's Material

Caricato da

mastrmindTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Head's Up: Last Week's Material Week's Material

Caricato da

mastrmindCopyright:

Formati disponibili

Heads Up

Last weeks material

Memory hierarchies, the basics of cache design Main memory architectures; advanced topics in computer architecture

- Reading assignment PH: 5.1-5.2, C.9

This weeks material

Next (last!) weeks material

Cumulative review

CSE331 W14&15.2

Irwin Fall 09 PSU

Review: Major Components of a Computer

Processor Control

Devices

Memory Input Output

Main Memory uses DRAM for density (size)

Datapath

Higher density (1 transistor cells), lower power, cheaper but slower (access times of 50 to 70 nsec) Dynamic, so needs to be refreshed regularly (~ every 8 ms)

Main Memory

Cache

Secondary Memory (Disk)

CSE331 W14&15.5

Irwin Fall 09 PSU

Review: The Memory Hierarchy

Take advantage of the principle of locality to present the user with as much memory as is available in the cheapest technology at the speed offered by the fastest technology

Processor

4-8 bytes (word)

Increasing distance from the processor in access time

L1$ (SRAM)

8-32 bytes (block)

L2$ (SRAM)

1 to 4 blocks

Main Memory (DRAM)

Inclusive what is in L1$ is a subset of what is in L2$ is a subset of what is in MM that is a subset of is in SM

1,024+ bytes (disk sector = page)

Secondary Memory (Disks)

CSE331 W14&15.6

(Relative) size of the memory at each level

Irwin Fall 09 PSU

DRAM Performance Metrics

DRAM addresses are divided into 2 halves (row and column)

RAS or Row Access Strobe that triggers the row decoder

CAS or Column Access Strobe that triggers the column selector

Latency: Time to access one word

Access Time: time between request and when word is read or written

- read access and write access times can be different

Cycle Time: time between successive (read or write) requests

Usually cycle time > access time

Bandwidth: How much data can be supplied per unit time

width of the data channel * the rate at which it can be used

Irwin Fall 09 PSU

CSE331 W14&15.7

Review: A Typical Interconnect System

Interrupts

Processor

Cache

Memory - I/O Bus

Main Memory

I/O Controller

I/O Controller

Graphics

I/O Controller

Network

Disk

Disk

CSE331 W14&15.8

Irwin Fall 09 PSU

Main Memory (DRAM) System

Its important to match the cache characteristics

Remember, caches want information provided to them one block at a time (and a block is usually more than one word)

with the main memory characteristics

use DRAMs that support fast multiple word accesses, preferably ones that match the block size of the cache

with the memory-bus characteristics

make sure the memory-bus can support the DRAM access rates and patterns with the goal of increasing the Memory-Bus_to_Cache bandwidth

CSE331 W14&15.9

Irwin Fall 09 PSU

DRAM Packaging - DIMMs

Dual In-line Memory Modules

Small printed circuit board that holds DRAMs with a 64-bit datapath

Each contain eight x4 (by 4) DRAM parts or x8 DRAM parts

Front Side Bus (1333MHz, 10.5GB/sec)

FB DDR2 667 (5.3GB/sec)

Intel Xeon 5300 processor

Main memory DIMMs

Memory Controller Hub (north bridge) 5000P

CSE331 W14&15.10

Irwin Fall 09 PSU

Classical DRAM Organization (~Square Planes)

bit (data) lines

r o w

Each intersection represents a 1-T DRAM cell

word (row) select line

d e c o d e r

DRAM Cell Array

m planes (where m is the # of bits in the part)

column Address (CAS)

row Address (RAS)

Column Selector & I/O Circuits

data bit

data bit data bit

CSE331 W14&15.11

The column address selects the requested bit from the row in each plane Irwin Fall 09 PSU

Classical DRAM Operation

DRAM Organization:

Column Address

N rows x N column x M-bit (planes) Reads or Writes M-bit at a time

N rows

N cols

DRAM

Each M-bit access requires a RAS / CAS cycle

Row Address

Cycle Time Access Time

M bits M-bit Output

1st M-bit

RAS

2nd M-bit

CAS

Row Address

CSE331 W14&15.12

Col Address

Row Address

Col Address

Irwin Fall 09 PSU

(Fast) Page Mode DRAM Operation

A row

is kept open by keeping the RAS asserted

Column Address

N cols

Pulse CAS to access other M-bit blocks on that row Successive reads or writes within the row are faster since dont have to precharge and (re)access that row

Cycle Time 2nd M-bit

DRAM N rows

Row Address

N x M row M bits M-bit Output 3rd M-bit 4th M-bit

1st M-bit

RAS

CAS Row Address

CSE331 W14&15.13

Col Address

Col Address

Col Address

Col Address

Irwin Fall 09 PSU

Synchronous DRAMs (SDRAMs)

Like page mode DRAMS, synchronous DRAMs have the ability to transfer a burst of data from a series of sequential addresses that are in the same row

For words in the same burst, dont have to provide the complete (row and column) addresses

Specify the starting (row+column) address and the burst length (burst must all be in the same DRAM row). The row is accessed from the DRAM and loaded into a row cache (SRAM). Data words in the burst are then accessed from that SRAM under control of a clock signal.

DDR SDRAMs (Double Data Rate SDRAMs)

Transfers burst data on both the rising and falling edge of the clock (so twice fast)

Now have DDR2 and DDR3 with even higher clock rates

Irwin Fall 09 PSU

CSE331 W14&15.14

Synchronous DRAM (SDRAM) Operation

After RAS loads a row into the SRAM cache

Column Address

+1 N cols

Input CAS as the starting burst address along with a burst length to read a burst of data from a series of sequential addresses within that row on the clock edge

DRAM N rows

Row Address

N x M SRAM M-bit Output

M bit planes

clock

RAS CAS

1st M-bit

2st M-bit

3st M-bit

4st M-bit

Row Address

CSE331 W14&15.15

Col Address

Row Address

Irwin Fall 09 PSU

http://en.wikipedia.org/wiki/DDR_SDRAM

DRAM Memory Latency & Bandwidth Milestones

DRAM Page DRAM Page DRAM Page DRAM SDRAM DDR SDRAM

Module Width

Year

16b

1980

16b

1983

32b

1986

64b

1993

64b

1997

64b

2000

Mb/chip

Die size (mm2) Pins/chip

0.06

35 16

0.25

45 16

1

70 18

16

130 20

64

170 54

256

204 66

BWidth (MB/s)

Latency (nsec)

13

225

40

170

160

125

267

75

640

62

1600

52

Patterson, CACM Vol 47, #10, 2004

In the time that the memory to processor bandwidth has more than doubled the memory latency has improved by a factor of only 1.2 to 1.4 To deliver such high bandwidth, the internal DRAM has to be organized as interleaved memory banks

CSE331 W14&15.16 Irwin Fall 09 PSU

Memory Systems that Support Caches

The off-chip interconnect and memory architecture can affect overall system performance in dramatic ways

on-chip

CPU

One word wide organization (one word wide bus and one word wide memory)

Assume

1.

Cache

bus

1 memory bus clock cycle to send the addr

2.

32-bit data & 32-bit addr per cycle

15 memory bus clock cycles to get the 1st word in the block from DRAM (row cycle time), 5 memory bus clock cycles for 2nd, 3rd, 4th words (column access time) 1 memory bus clock cycle to return a word of data number of bytes accessed from memory and transferred to cache/CPU per memory bus clock cycle

Irwin Fall 09 PSU

DRAM Memory

3.

Memory-Bus to Cache bandwidth

CSE331 W14&15.18

One Word Wide Bus, One Word Blocks

on-chip

CPU

Cache bus

If the block size is one word, then for a memory access due to a cache miss, the pipeline will have to stall for the number of cycles required to return one data word from memory

cycle to send address

cycles to read DRAM

cycle to return data

DRAM Memory

total clock cycles miss penalty

Number of bytes transferred per clock cycle (bandwidth) for a single miss is

bytes per memory bus clock cycle

CSE331 W14&15.19

Irwin Fall 09 PSU

One Word Wide Bus, Four Word Blocks

on-chip

What if the block size is four words and each word is in a different DRAM row?

cycle to send 1st address

CPU

cycles to read DRAM

Cache bus

cycles to return last data word total clock cycles miss penalty

DRAM Memory

Number of bytes transferred per clock cycle (bandwidth) for a single miss is

bytes per memory bus clock cycle

CSE331 W14&15.21

Irwin Fall 09 PSU

One Word Wide Bus, Four Word Blocks

on-chip

What if the block size is four words and all words are in the same DRAM row?

cycle to send 1st address

CPU

cycles to read DRAM

Cache bus

cycles to return last data word total clock cycles miss penalty

DRAM Memory

Number of bytes transferred per clock cycle (bandwidth) for a single miss is

bytes per memory bus clock cycle

CSE331 W14&15.23

Irwin Fall 09 PSU

Interleaved Memory, One Word Wide Bus

on-chip

For a block size of four words

cycle to send 1st address

cycles to read DRAM banks cycles to return last data word

CPU

Cache bus DRAM DRAM DRAM DRAM Memory Memory Memory Memory bank 0 bank 1 bank 2 bank 3

total clock cycles miss penalty

Number of bytes transferred per clock cycle (bandwidth) for a single miss is

CSE331 W14&15.25

bytes per memory bus clock cycleFall 09 PSU Irwin

Extracting Yet More Performance

Superpipelining

Increase the depth of the pipeline to overlap more instructions

Dynamic multiple-issue (superscalar)

Execute multiple instructions at one time with the decisions on which instructions to execute simultaneously being made dynamically by the hardware E.g., Pentium 4

Static multiple-issue (VLIW or EPIC)

Execute multiple instructions at one time with the decisions on which instructions to execute simultaneously being made statically by the compiler

E.g., Intel Itanium and Itanium 2

Hyperthreading Multicore

Irwin Fall 09 PSU

CSE331 W14&15.28

Super Pipelined Processors

Increasing the depth of the pipeline leads to very short clock cycles, so very high clock rates (and more instructions in flight at one time)

The higher the degree of superpipelining

the more forwarding/hazard hardware needed

the more stall cycles (noop instructions) incurred

the more pipeline latch overhead (i.e., the pipeline latch accounts for a larger and larger percentage of the clock cycle time)

the bigger the clock skew issues (i.e., because of faster and faster clocks)

CSE331 W14&15.29

Irwin Fall 09 PSU

Super Scalar Processors

Execute multiple instructions at one time with the decisions on which instructions to execute simultaneously being made dynamically by the hardware

In-order fetch, in-order issue, out-of-order execution, and in-order commit

Pipelining creates true dependencies (read before write)

Out-of-order execution creates antidependencies (write before read) and output dependencies (write before write) In-order commit allows speculation and is required to implement precise interrupts

Register renaming (RUU) architecture structures are used to solve these storage dependencies in superscalar processors

CSE331 W14&15.30

Irwin Fall 09 PSU

A Super Scalar Example

Intel Pentium 4 (IA-32 ISA)

Decodes the IA-32 instructions into microoperations

Does register renaming with a RUU-like structure Has a 20 stage pipeline

op queue

RUU allocation 4 FU queues Instr dispatch 5 RegFile access 2 Execution

I$ access (Bpredict) # cycles 5

RUU queue

Commit

7 Functional Units: 2 integer ALUs, 1 FP ALU, 1FP move, load, store, complex Up to 126 instructions in flight, including 48 loads and 24 stores

4K entry branch predictor

CSE331 W14&15.31

Irwin Fall 09 PSU

VLIW Processors

Execute multiple instructions at one time with the decisions on which instructions to execute simultaneously being made statically at compile time by the compiler

Issue packet the set of instructions that are bundled together and issued in one clock cycle think of it as one large instruction with multiple operations

- The mix of instructions in the packet (bundle) is usually restricted a single instruction with several predefined fields

The compiler does static branch prediction and code scheduling to reduce (control) or eliminate (data) hazards

VLIWs have

Multiple functional units Multi-ported register files

Wide program bus

Irwin Fall 09 PSU

CSE331 W14&15.32

Hyperthreading (aka Multithreading, SMT)

Can hide true data dependency stalls, cache miss stalls, and branch stalls by finding instructions (from other process threads) that are independent of those stalling instructions Hardware multithreading allows multiple processes (threads) to share the functional units of a single processor

Processor must duplicate the state hardware for each thread a separate register file, PC, instruction buffer, and store buffer for each thread

The caches, TLBs, BHT, BTB, RUU can be shared (although the miss rates may increase if they are not sized accordingly) The memory can be shared through virtual memory mechanisms

Hardware must support efficient thread context switching

CSE331 W14&15.33

Irwin Fall 09 PSU

Hyperthreading Example: Suns Niagara

Cores are simple (single-issue, 6 stage, no branch prediction), small, and power-efficient

Fetch Thrd Sel Decode RegFile x8 Execute Memory WB

I$ ITLB

Inst bufx8

Thrd Sel Mux

Decode

ALU Mul Shft Div

D$ DTLB Stbufx8

Crossbar Interface

Thread Select Logic

Thrd Sel Mux

PC logicx8

Instr type Cache misses Traps & interrupts Resource conflicts

From MPR, Vol. 18, #9, Sept. 2004

CSE331 W14&15.34 Irwin Fall 09 PSU

Potrebbero piacerti anche

- CS2100 – Review of Computer Memory TechnologiesDocumento33 pagineCS2100 – Review of Computer Memory TechnologiesamandaNessuna valutazione finora

- Computer Structure - MemoryDocumento61 pagineComputer Structure - MemoryLotso Chik100% (1)

- CS 152 Computer Architecture and Engineering Lecture 6 - MemoryDocumento29 pagineCS 152 Computer Architecture and Engineering Lecture 6 - Memorysam_almasryNessuna valutazione finora

- Unit-III: Memory: TopicsDocumento54 pagineUnit-III: Memory: TopicsZain Shoaib MohammadNessuna valutazione finora

- O MemorijamaDocumento36 pagineO MemorijamazaleksNessuna valutazione finora

- Chapter 5-The Memory SystemDocumento84 pagineChapter 5-The Memory SystemupparasureshNessuna valutazione finora

- Chapter 5-The Memory SystemDocumento80 pagineChapter 5-The Memory SystemPuneet BansalNessuna valutazione finora

- Lect 05 DramDocumento63 pagineLect 05 DramTupa HasanNessuna valutazione finora

- The Memory Hierarchy: TopicsDocumento43 pagineThe Memory Hierarchy: TopicsrobinptNessuna valutazione finora

- Mc9211unit 5 PDFDocumento89 pagineMc9211unit 5 PDFsanthoshNessuna valutazione finora

- Lec2 MemDocumento12 pagineLec2 MemparagNessuna valutazione finora

- Design of Sram in VerilogDocumento124 pagineDesign of Sram in VerilogAbhi Mohan Reddy100% (3)

- Unit 3 OF ESDDocumento22 pagineUnit 3 OF ESDTanveer ShariffNessuna valutazione finora

- ECE 554 Computer Architecture Main Memory Spring 2013Documento35 pagineECE 554 Computer Architecture Main Memory Spring 2013Emmanuel KishoreNessuna valutazione finora

- Memory and StorageDocumento46 pagineMemory and StoragekasthurimahaNessuna valutazione finora

- Computer Science 146 Computer ArchitectureDocumento16 pagineComputer Science 146 Computer ArchitectureharshvNessuna valutazione finora

- Os nOTESDocumento21 pagineOs nOTESBARATHNessuna valutazione finora

- Memory Access ShedulingDocumento11 pagineMemory Access ShedulingZzzzeeeNessuna valutazione finora

- Computer Architecture Cache DesignDocumento28 pagineComputer Architecture Cache Designprahallad_reddy100% (3)

- CSE 420 - Computer Architecture I Lecture 9 MemoriesDocumento21 pagineCSE 420 - Computer Architecture I Lecture 9 MemoriesBruno MalakianNessuna valutazione finora

- Low-Power SRAM-Based Delay Buffer Using Gated Driver TreeDocumento49 pagineLow-Power SRAM-Based Delay Buffer Using Gated Driver TreeydsrajuNessuna valutazione finora

- Memory Types LaptopDocumento4 pagineMemory Types LaptopNsb El-kathiriNessuna valutazione finora

- Microprocessor CoursePDFDocumento31 pagineMicroprocessor CoursePDFahmadzaatariNessuna valutazione finora

- Main Memory DRAM's: - Access Time - Cycle TimeDocumento3 pagineMain Memory DRAM's: - Access Time - Cycle TimeelexboyNessuna valutazione finora

- DPCO Unit 5 2mark Q&ADocumento20 pagineDPCO Unit 5 2mark Q&Akanimozhi rajasekarenNessuna valutazione finora

- Lecture 7 Main MemoryDocumento36 pagineLecture 7 Main MemoryKhadija Ali BaigNessuna valutazione finora

- Memory Hierarchy Levels: Block (Aka Line) : Unit of Copying If Accessed Data Is Present in Upper LevelDocumento16 pagineMemory Hierarchy Levels: Block (Aka Line) : Unit of Copying If Accessed Data Is Present in Upper LevelalexNessuna valutazione finora

- Mentor: Sanjeev Kumar: Poorva Anand GROUP-11 (ECE)Documento31 pagineMentor: Sanjeev Kumar: Poorva Anand GROUP-11 (ECE)Poorva AnandNessuna valutazione finora

- RAM TechnologiesDocumento25 pagineRAM TechnologiesAmarnath M DamodaranNessuna valutazione finora

- Main Memory DRAM's:: Time Between The Read Is Requested and The DesiredDocumento3 pagineMain Memory DRAM's:: Time Between The Read Is Requested and The DesiredManikanta ManiNessuna valutazione finora

- Computer Organization & Architecture: Internal MemoryDocumento28 pagineComputer Organization & Architecture: Internal Memorymuhammad farooqNessuna valutazione finora

- Sdram Wiki FileDocumento16 pagineSdram Wiki Filelng_babie19Nessuna valutazione finora

- Unit 5Documento33 pagineUnit 5LekshmiNessuna valutazione finora

- Sram Memory Cell: By:-Udit Shah & Rajdeep KandiyalDocumento13 pagineSram Memory Cell: By:-Udit Shah & Rajdeep KandiyalSrasVelNessuna valutazione finora

- BY: For:: Ahmad Khairi HalisDocumento19 pagineBY: For:: Ahmad Khairi HalisKhairi B HalisNessuna valutazione finora

- Exploiting Memory HierarchyDocumento49 pagineExploiting Memory HierarchySara AlkheilNessuna valutazione finora

- Computer MemoryDocumento34 pagineComputer MemoryAlice GuarinNessuna valutazione finora

- 5 - Internal MemoryDocumento22 pagine5 - Internal Memoryerdvk100% (1)

- DRAM Lecture2Documento32 pagineDRAM Lecture2santanu_sinha87Nessuna valutazione finora

- SRAM: Static Random-Access Memory GuideDocumento9 pagineSRAM: Static Random-Access Memory GuideSantosh KumarNessuna valutazione finora

- Basic DRAM Operation and EvolutionDocumento7 pagineBasic DRAM Operation and EvolutionKelvinNessuna valutazione finora

- Memories: Volatile and Non-VolatileDocumento8 pagineMemories: Volatile and Non-VolatilejancyphilipNessuna valutazione finora

- Optimizing Main Memory PerformanceDocumento17 pagineOptimizing Main Memory PerformanceJagdeep ArryNessuna valutazione finora

- BSNL NotesDocumento14 pagineBSNL NotesmicrodotcdmNessuna valutazione finora

- 04 - Computer Memory SystemsDocumento91 pagine04 - Computer Memory SystemsAhmed Jama AdanNessuna valutazione finora

- Inside RAM: Two-Level AddressingDocumento12 pagineInside RAM: Two-Level AddressingdoomachaleyNessuna valutazione finora

- Main Memory: Computer Architecture COE 501Documento18 pagineMain Memory: Computer Architecture COE 501ah chongNessuna valutazione finora

- Verify2011 04Documento35 pagineVerify2011 04Wazir SinghNessuna valutazione finora

- Types of MemoryDocumento14 pagineTypes of MemorySriram RamakrishnanNessuna valutazione finora

- Introduction To Multicore Programming: University of Western Ontario, London, Ontario (Canada)Documento60 pagineIntroduction To Multicore Programming: University of Western Ontario, London, Ontario (Canada)John DeepNessuna valutazione finora

- 2.2 CU Memory system designDocumento75 pagine2.2 CU Memory system designprakuld04Nessuna valutazione finora

- SRAMDocumento36 pagineSRAMAbhijit KarthikNessuna valutazione finora

- IISc eDRAM Ravi 2014 PDFDocumento75 pagineIISc eDRAM Ravi 2014 PDFVenkateswararao MusalaNessuna valutazione finora

- DRAM Basics: Refresh, Organization, and Innovations to Overcome Latency and Power WallsDocumento14 pagineDRAM Basics: Refresh, Organization, and Innovations to Overcome Latency and Power Wallsahmedfhd1Nessuna valutazione finora

- Dynamic Random-Access Memory PDFDocumento17 pagineDynamic Random-Access Memory PDFBintang Kejora100% (1)

- Class Notes: Memory Technology and System-Level Memory DesignDocumento44 pagineClass Notes: Memory Technology and System-Level Memory DesignHarish ReddyNessuna valutazione finora

- Introduction To SDRAM and Memory ControllersDocumento31 pagineIntroduction To SDRAM and Memory ControllersHadley MagnoNessuna valutazione finora

- William Stallings Computer Organization and Architecture: Internal MemoryDocumento60 pagineWilliam Stallings Computer Organization and Architecture: Internal MemoryreinaldoopusNessuna valutazione finora

- Oracle 11g R1/R2 Real Application Clusters EssentialsDa EverandOracle 11g R1/R2 Real Application Clusters EssentialsValutazione: 5 su 5 stelle5/5 (1)

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipDa EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNessuna valutazione finora

- LG SKEMA 22lk310 - 22lk311Documento28 pagineLG SKEMA 22lk310 - 22lk311Aditya AdityaNessuna valutazione finora

- FAN6300A-or HDocumento15 pagineFAN6300A-or Hnesa.elektronNessuna valutazione finora

- 10BR60V2Documento2 pagine10BR60V2bk1313Nessuna valutazione finora

- Modelling of Telegraph Equations in Transmission Lines (Greeff2014)Documento11 pagineModelling of Telegraph Equations in Transmission Lines (Greeff2014)daegerteNessuna valutazione finora

- Bts CalibrationDocumento15 pagineBts CalibrationAhmed BouriNessuna valutazione finora

- Htc-1100e Cim enDocumento119 pagineHtc-1100e Cim enFerry KurniawanNessuna valutazione finora

- Integrated Circuits Guide - 74HC151 Multiplexer and MoreDocumento15 pagineIntegrated Circuits Guide - 74HC151 Multiplexer and MoreJ Luis G RendonNessuna valutazione finora

- PLCDocumento58 paginePLCR.Deepak KannaNessuna valutazione finora

- SemiconductorDocumento14 pagineSemiconductorAnnaya KhanNessuna valutazione finora

- Everything You Need to Know About Inverter BasicsDocumento4 pagineEverything You Need to Know About Inverter Basicsmuhaned190Nessuna valutazione finora

- Compal La-9063p r1.0 Schematics PDFDocumento63 pagineCompal La-9063p r1.0 Schematics PDFВиктор ГольченкоNessuna valutazione finora

- Coplanar Waveguide Fed Bow-Tie Slot AntennasDocumento7 pagineCoplanar Waveguide Fed Bow-Tie Slot AntennasNguyễn Trung PhongNessuna valutazione finora

- 74HC HCT4066 NXPDocumento27 pagine74HC HCT4066 NXPprpabst8514Nessuna valutazione finora

- EMC Components: ZJYS Series ZJYS51, ZJYS81 Types Common Mode Choke Coils For Signal Line SMDDocumento4 pagineEMC Components: ZJYS Series ZJYS51, ZJYS81 Types Common Mode Choke Coils For Signal Line SMDAngel VelasquezNessuna valutazione finora

- PC-2668 enDocumento2 paginePC-2668 enMahmudul Hasan TanuNessuna valutazione finora

- M8 Digital Carrier Line EncodingDocumento18 pagineM8 Digital Carrier Line EncodingcsfaciolanNessuna valutazione finora

- Smart Sensors: Vishwakarma Institute of Information TechnologyDocumento11 pagineSmart Sensors: Vishwakarma Institute of Information TechnologyL13 Krushna NemadeNessuna valutazione finora

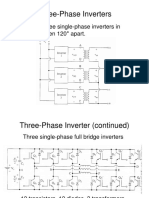

- Three-Phase Inverter 180° ConductionDocumento27 pagineThree-Phase Inverter 180° ConductionWana BilaNessuna valutazione finora

- Introduction to Computers: An Essential GuideDocumento97 pagineIntroduction to Computers: An Essential Guideta_1091100% (1)

- Experiment 3 Thyristor Speed Controllers With RegulationDocumento11 pagineExperiment 3 Thyristor Speed Controllers With RegulationMaria Blessie NavarreteNessuna valutazione finora

- DA6002D-DA10004D: Installation / Owner'S ManualDocumento14 pagineDA6002D-DA10004D: Installation / Owner'S ManualRicardo PeñaNessuna valutazione finora

- Fiber Optic splitter-PLC Splitters in ABS Box Type, Mini Tube and LGX Box Type - V2017Documento2 pagineFiber Optic splitter-PLC Splitters in ABS Box Type, Mini Tube and LGX Box Type - V2017AlanNessuna valutazione finora

- Aspire Es1-432 - Quanta ZQF - Da0zqfmb6f0Documento32 pagineAspire Es1-432 - Quanta ZQF - Da0zqfmb6f0Nico Saibort JuniorNessuna valutazione finora

- Dat-250w Ja2allsDocumento47 pagineDat-250w Ja2allskrandall23Nessuna valutazione finora

- AIM: To Determine Resistance Per CM of A Given Wire by Plotting A Graph of Potential Apparatus RequiredDocumento6 pagineAIM: To Determine Resistance Per CM of A Given Wire by Plotting A Graph of Potential Apparatus RequiredMayank KumarNessuna valutazione finora

- 64T64R Massive Mimo Remote Radio UnitDocumento2 pagine64T64R Massive Mimo Remote Radio UnitMahesh A BirariNessuna valutazione finora

- Digital Electronics On Seven Segment Display DecoderDocumento18 pagineDigital Electronics On Seven Segment Display DecodernikhilmalagiNessuna valutazione finora

- Manual ADW300Documento27 pagineManual ADW300Paulo BuosiNessuna valutazione finora

- A-800-85-15i-0-N Electrical and Mechanical SpecificationsDocumento1 paginaA-800-85-15i-0-N Electrical and Mechanical SpecificationsMelissa BroffordNessuna valutazione finora