Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Lecture 10

Caricato da

Ron JosephDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Lecture 10

Caricato da

Ron JosephCopyright:

Formati disponibili

AIM: Study various process- Slicing & polishing

Students, now you are familiar with the wafer preparation techniques i.e. CZ & FZ methods. Individual wafers must then be prepared for IC manufacturing. This involves a series of mechanical steps which result in wafers that are almost perfectly flat, polished to a mirror finish on the top side and free of any mechanical defect from the sawing and other operations. This lecture deals with above-mentioned techniques. After studying this lecture you will be able to understand the complete method of preparing wafer which is free from defects and that can be used for manufacturing ICs.

Silicon Shaping:

Silicon is a hard, brittle material. The most suitable material for shaping and cutting silicon is industrial- grade diamond, although SiC and Al2O3 have also been used. This section highlights the major shaping methods. Conversion of silicon ingots into polished wafers requires normally six machining operations, two chemical operations, and one or two polishing operations. Additionally, assorted inspections and evaluations are performed between the major process steps. A finished wafer is subject to a number of dimensional tolerances, dictated by the needs of the device fabrication technology. Many diverse materials are used in the fabrication of field effect transistors (MOSFETs, FETs), integrated circuits (ICs, ASICs), focal plane arrays, infrared detectors. These devices and new materials are constantly being developed. Silicon is common, but for many applications, alternatives have been found in a group of materials known as Compound Semiconductors, the most commonly used being Gallium Arsenide, Indium Phosphide, Mercury Cadmium Telluride, Cadmium Sulphide and Cadmium Telluride. Whatever the application or material, each wafer undergoes several common stages during manufacture, which include slicing the wafer from the crystal, preparing the surface prior to fabrication and thinning the device after fabrication. Slicing is carried out on an annular saw, and surface finishing and thinning are normally accomplished by a combination of lapping and polishing. The range of Semiconductor materials processing and preparation requirements encountered in this sector can be summarized as follows: - Wafer slicing - Wafer thinning and back lapping - Chemo-Mechanical Polishing - Chemical Polishing Shaping operations: The block diagram of various shaping operation is given below:

The first shaping operation removes the seed and tang ends from the ingot. Portions of the ingot that fail the resistivity and perfection evaluations previously mentioned are also cut away. The cuttings are sufficiently pure to be recycled, after cleaning in the growing operation. The rejected ingot pieces can also be sold as metallurgical- grade silicon. The cutting is conveniently done as a manual operation using circular saw. The next operation is a surface grinding, and is the step that defines the diameter of the material. Silicon ingots are grown slightly oversized because the automatic diameter control in crystal growing cannot maintain the needed diameter tolerance, and crystals cannot be grown perfectly round. Figure 1 shows schematically the lathe like machine tool used to grind the ingot to diameter. A rotating cutting tool makes multiple passes down a rotating ingot until the chosen diameter is attained. Precise diameter control is required for many kinds of processing equipment, and is consideration in the design of processing and furnace racks. Following diameter grinding, one or more flats are ground along the length of the ingot. Single crystal silicon ingots are characterized by the orientation of their silicon crystals. Before the ingot is cut into wafers one or two flats are ground into the diameter of the ingot to mark this orientation.

The largest flat, called the major or primary flat, is usually relative to a specific crystal direction. The flat is located by an X-ray technique. The primary flat serves several purposes. It is used as a mechanical locator in automated processing equipment to position the wafer, and also serves to orient the IC device relative to the crystal. Others smaller flats are called secondary flats, and serve to identify the orientation and conductivity type of the material (Fig. 2). Secondary flats provide a means of quickly sorting and identifying wafers should mixing occur.

Figure 1: Schematic of grinding process

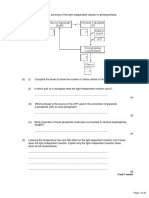

Figure 2: Identifying flats on silicon wafer Once these operations have been completed, the ingot is ready to be sliced into wafers. Slicing is important because it determines four wafer parameters: Surface orientation Thickness Taper Bow The surface orientation is determined by cutting several wafers, measuring the orientation by an X-ray method, and then resetting the saw until the correct orientation is achieved. Wafers of <100> orientation are usually cut on orientation(Table 1). The tolerances allowed for orientation do not adversely affect MOS device characteristics such as interface trap density. The other common orientation, <111>, is usually cut off orientation(by about 3), as required for epitaxial processing

Table-1

The wafer thickness is essentially fixed by slicing, although the final value depends on subsequent shaping operations. Thicker wafers are better able to withstand the stresses of subsequent thermal processes (epitaxy, oxidation, and diffusion), and as a result exhibit less tendency to deform plastically or elastically in such processing. A major concern in slicing is the blades continued ability to cut wafers from the crystal in very flat planes. If the blade deflects during slicing, this will not be achieved. By positioning a capacitive sensing device near the blade, the blade position and vibration in the blade can be monitored, and higher quality cutting achieved. If a wafer is sliced with excessive curvature (bow), subsequent lapping operations may not be able to correct it, and surface flatness requirements cannot be obtained by polishing. Inner diameter (ID) slicing is the most common mode of slicing. ID slicing uses a saw blade whose cutting edge is on the interior of an annulus. Figure 3 shows a schematic of this process.

Fig. 3 Schematic of ID slicing process The ingot is prepared for slicing by mounting it in wax or epoxy on a support, and then positioning the support on the saw. This procedure ensures that the ingot is held rigid for the slicing process. Some success has been obtained mounting ingots in a fixture using hydraulic pressure. The saw blade is a thin sheet of stainless steel, (325m) with diamond bonded on the inner rim. This blade is tensioned in a collar and then mounted on a drum that rotates at high speed (2000r/min) on the saw. Saw blades up to 58cm in diameter with a 20cm opening

are available. These blades have a slicing capability up to nearly the ID opening of 20cm. The blade is moved relative to the stationary ingot. The cutting process is water-cooled. The kerf loss (loss due to blade width) at slicing is 325m, which means that approximately one-third of crystal is lost as sawdust. Cutting speeds are normally 0.05cm/s, which, considering that wafers are sliced sequentially is a rather slow process. Another shortcoming is the drums finite depth, which limits the length of the ingot section that can be cut into wafers. Another style of ID saw has the blade mounted on an air bearing and is rotated by means of belt-drive, an arrangement allowing any length of ingot to be sliced. After the ingot is sliced, individual wafers are recovered opposite the feed side and placed in a cassette. This type of saw, which hydraulically mounts the ingot, represents a highly automatic approach to sawing. The wafer as cut varies enough in thickness to warrant an additional operation if the wafers are intended for VLSI application. A mechanical lapping operation (fig.4), performed under pressure using a mixture of Al2O3 and glycerine, produces a wafer with flatness uniform to within 2m. This process helps ensure that surface flatness requirements for photolithography can be achieved in the subsequent polishing steps. Approximately 20m per side is removed.

Fig.4 A final shaping step is edge contouring, where a radius is ground on the rim of the wafer (fig. 5). This process is usually done in cassette-fed, high-speed equipment. Edge-rounded wafers develop fewer edge chips during device fabrication and aid in controlling the buildup of photoresist at the wafer edge. Chipped edges act as places where dislocations can be introduced during thermal cycles and as places where wafer fracture can be initiated.

Fig.5 Schematic of edge- containing process

Etching:

The previously described shaping operations leave the surface and edges of the wafer damaged and contaminated, with the depth of work damage depending on the specifies of the machining operations. The damaged and contaminated regions are on the order of 10m deep and can be removed by chemical etching. Historically, mixtures of hydrofluoric, nitric, & acetic acids have been used but alkaline etching, using potassium & sodium hydroxide is also in common use. The process equipment includes an acid sink, which contains a tank to hold the etching solution, one or more positions for rinsing the wafers in water. The process is batch in nature, involving tens of wafers. The best process equipment provides a means of rotating the wafer during acid etching to maintain uniformity. Processing is usually performed with a substantial over etch to assure all damage is removed. Removing 20 m per side is typical. The etching process is checked frequently by gauging wafers for thickness before & after etching. Etch times are usually on the order of several minutes per batch.

The etching involves oxidation-reduction processes followed by dissolution of tan oxidation product. In the hydrofluoric, nitric, & acetic acid etching system 362.63 nitric acid is the oxidant & hydrofluoric acid dissolves the oxidized products according to the following reaction: 3Si + 4HNO3+ 18HF 3H2 SiF6 + 4NO +8H2O (1)

Acetic acid dilutes the system so that etching can be better controlled. Water can also be used, but acetic acid is preferable because water is a by-product of the reaction. The etching can be isotropic or anisotropic, according to the acid mixture or temperature. In HF rich solutions, the reaction is limited by the oxidation step. The regime of etching is anisotropic & the oxidation reaction is sensitive to doping, orientation, & defect structure of the crystal (where the oxidation occurs preferentially). The use of HNO3- rich mixtures produces a condition of isotropic etching, & the dissolution process is then rate limiting. Over the range 30 to 50C, the etching kinetics of an HNO3rich solution have been found to be diffusion controlled rather than reaction rate limited (fig 6). Thus transport diffusion of reactant products to the wafer surface across a stagnant boundary layer is the controlling mechanism. For these reasons, the HNO3rich solutions are preferred for removing work damage. Rotating the wafers in the solution controls the boundary layer thickness & thereby effects dimensional control of the wafer. The isotropic character of the etch produces a smooth, somewhat specular surface. A common etch formulation is a 4:1:3 mixture of HNO3 (79% by weight), HF (49% by weight) & CH3COOH acids.

Figure 6 Typical etch rate versus temperature for one mixture of HF, HNO3 and CH3COOH

Unfortunately the dimensional uniformity introduced by the lapping step is not maintained across larger diameter wafers (>75 mm 0 to a degree compatible with maintaining surface flatness in polishing. The hydrodynamics of rotating a large diameter wafer in solution do not allow for a uniform boundary layer, so a taper is introduced in the wafer. Projection lithography places demands on surface flatness that necessitate the use of alkaline etching. Alkaline etching is by nature anisotropic; thus, the etch rate depends on the surface orientation. The reaction is apparently dominated by the number of dangling bonds present on the surface. The reaction is generally reaction rate limited, & wafers do not have to be rotated in the solution. Since boundary layer transport is not a factor, excellent uniformity can be achieved. As in acid etching, the reaction is two fold when a mixture of KOH/ H2O or NAOH/H2O is used. A typical formulation uses KOH & H2O in a 45% by weight solution (i.e. 45% KOH & 55% H2O) at 90 to achieve an etch rate of 25 m/min for {100} surfaces An occasional problem with the damage removal process is insufficient etching, which can lead to generation of dislocations in subsequent treatments because of residual damage. Residual damage can be evaluated by measuring the fracture strength of the material after etching or by thermal wave mapping. Before etching a laser is commonly used to engrave an alphanumeric identification mark on each wafer. Laser marking will replace the secondary flat identification method for larger diameter wafers (>= 150mm).

Polishing

Polishing is the final step. Its purpose is to provide a smooth, specular surface on which device features can be photoengraved. A main VLSI concern is to produce a surface with a high degree of surface flatness & minimum local slope to meet the requirements of optical projection lithography. Values between 5 & 10m are typical surface flatness specifications. The surface is also required to be free from contamination & damage.

Fig 7 shows a typical polishing machine & schematic of the process. The process requires considerable operator attention for loading & unloading. It can be conducted as a single wafer or batch wafer process depending on the equipment. Economics decides the choice of single or batch processing: single wafer processing is preferred for large wafers. Single wafer processing also offers a better means of achieving surface flatness goals. In both single & batch processing the process involves a polishing pad made of artificial fabric, such as polyester felt, polyurethane laminate. Wafers are mounted on a fixture, pressed against the pad under high pressure, & rotated relative to the pad. A mixture of polishing slurry & water, dripped into the pad, does the polishing (which is both a chemical & mechanical process.)

The porosity of the pad is a factor in carrying slurry to the wafer for polishing. The slurry is a colloidal suspension of fine SiO2 particles (100 A diameter0 in an aqueous solution of sodium hydroxide. Under heat generated by friction, the sodium hydroxide oxidizes the silicon with the OH- radical. This is the chemical step. In the mechanical step the silica particles in the slurry abrade the oxidized silicon away. Polishing rate & surface finish are complex functions of pressure, pad properties, rotation speed, slurry composition & pH of the polishing solution. Typical processes remove 25m of silicon. In a batch process involving tens of wafers, silicon removal can take 30 to 60 min. Single wafer processing can be accomplished in 5 min. Single wafer processes use higher processes than the batch processes.

Figure7 Schematic of polishing process

The method of mounting wafers for polishing also deserves attention. Historically wafers were waxed to a metal plate. This method is costly & may not yield the bets surface flatness. An alternative is a wax less technique where wafers are applied to a conformal pad, typically a two-layer vinyl. This method is cost effective & eliminates the influence of rare surface particles on front surface flatness. After polishing the wafers are chemically cleaned with acid, base &/or solvent mixtures to remove slurry residue (& wax) & readied for inspection. Polished wafers are subjected to a number of measurements that are concerned with cosmetic, crystal perfection, mechanical, & electrical attributes.

Exercise: 1) State, why the wafer cannot be used for IC fabrication just after the crystal is grown. 2) List and explain the steps involved from the beginning to the end for preparing Si, wafer.

Potrebbero piacerti anche

- Manufacturing Process Btech MG University QP SolvedDocumento24 pagineManufacturing Process Btech MG University QP SolvedAnonymous f1UCK4100% (2)

- Wafer PreparationDocumento5 pagineWafer PreparationVimalNessuna valutazione finora

- Tools and Techniques For Plug and AbandonmentDocumento35 pagineTools and Techniques For Plug and Abandonmentchucks2117Nessuna valutazione finora

- Lapping, Honing and BroachingDocumento59 pagineLapping, Honing and Broachingsai leena100% (2)

- Milling With Waterjet: Flow InternationalDocumento4 pagineMilling With Waterjet: Flow InternationalAadithiyanNessuna valutazione finora

- 20119101surendra bareth-TERM PROJECT MFSCDocumento8 pagine20119101surendra bareth-TERM PROJECT MFSC9101 surendra BarethNessuna valutazione finora

- Manufacturing Processes: ME 335 432 Lecture #14Documento69 pagineManufacturing Processes: ME 335 432 Lecture #14abdullah sulimanNessuna valutazione finora

- Scribe and DiceDocumento5 pagineScribe and Diceprabhat1_16082Nessuna valutazione finora

- File 1696992905 GUSBAS202131582 L1 SemiconductorWafersDocumento5 pagineFile 1696992905 GUSBAS202131582 L1 SemiconductorWafersÃMĪT KUMAR SINGHNessuna valutazione finora

- GOS WP HardTurning F PDFDocumento26 pagineGOS WP HardTurning F PDFNhan LeNessuna valutazione finora

- 10 Abrasive Machining ProcessesDocumento0 pagine10 Abrasive Machining ProcessesAmmar KhanNessuna valutazione finora

- GC Column Cutting Mini Guide: Key WordsDocumento2 pagineGC Column Cutting Mini Guide: Key WordsLee WeatherillNessuna valutazione finora

- Pneumatic Circit For Cylinder IiDocumento12 paginePneumatic Circit For Cylinder IiAjay NishadNessuna valutazione finora

- Manufacturing Process - Module5.0Documento15 pagineManufacturing Process - Module5.0Fiza KamaNessuna valutazione finora

- Ductile or Partial Ductile Mode Machining of Brittle MaterialsDocumento7 pagineDuctile or Partial Ductile Mode Machining of Brittle MaterialsHangi TakimlisinNessuna valutazione finora

- Lab Manual - Mat Characterization (1) (1) - ExtractedDocumento9 pagineLab Manual - Mat Characterization (1) (1) - ExtractedAdvay Singh raizadaNessuna valutazione finora

- State State of The Art of Precision Abrasive Water Jet Cuttiof The Art of Precision Abrasive Water Jet CuttingDocumento22 pagineState State of The Art of Precision Abrasive Water Jet Cuttiof The Art of Precision Abrasive Water Jet CuttingJaveed A. KhanNessuna valutazione finora

- Manufacturing Technology (MEC - 205) : Unit - 1 Introduction To Manufacturing and Metal CastingDocumento74 pagineManufacturing Technology (MEC - 205) : Unit - 1 Introduction To Manufacturing and Metal CastingShridhar SavatNessuna valutazione finora

- Theory Application of Roll Forming (2010) - WebDocumento21 pagineTheory Application of Roll Forming (2010) - WebVenugopalan Manaladikalam100% (1)

- Metal Lo Graphic Sample Preparation - Cutting - Grinding - MountingDocumento12 pagineMetal Lo Graphic Sample Preparation - Cutting - Grinding - Mountingrmarsh21730100% (2)

- Mce516 Lecture Note 1Documento98 pagineMce516 Lecture Note 1Edward JNessuna valutazione finora

- Bab 2Documento73 pagineBab 2ezad2206Nessuna valutazione finora

- 111033256 莊仕愷 HW7Documento3 pagine111033256 莊仕愷 HW7林展宏Nessuna valutazione finora

- MSE311A - Set 1 Lab ManualDocumento16 pagineMSE311A - Set 1 Lab ManualHarshit RastogiNessuna valutazione finora

- InTech-Mechanical Micromachining by Drilling Milling and SlottingDocumento25 pagineInTech-Mechanical Micromachining by Drilling Milling and Slottingbalabmk9228Nessuna valutazione finora

- SR - NO. Chapter Name Page NoDocumento61 pagineSR - NO. Chapter Name Page Nodeep bahirshetNessuna valutazione finora

- Lab 3 Metallography and HardnessDocumento9 pagineLab 3 Metallography and HardnessTommy Miles100% (1)

- Manufacturing Processes: KKKM2833Documento4 pagineManufacturing Processes: KKKM2833SajjadNessuna valutazione finora

- Casting, Forming, and ForgingDocumento10 pagineCasting, Forming, and ForgingShe DilNessuna valutazione finora

- OC PultrusionDocumento29 pagineOC PultrusionalmakmenNessuna valutazione finora

- Lab Session 10Documento5 pagineLab Session 10Rahmat aliNessuna valutazione finora

- MP Unit 4 GrindingDocumento25 pagineMP Unit 4 GrindingJ S VAISHNAVNessuna valutazione finora

- Advanced Manufacturing Processes, Pune University, BEDocumento21 pagineAdvanced Manufacturing Processes, Pune University, BESachin KumbharNessuna valutazione finora

- Practical Metallography: Faculty of Production Engineering and ManagementDocumento18 paginePractical Metallography: Faculty of Production Engineering and ManagementMassimo FumarolaNessuna valutazione finora

- Bonded Abrasives Are Made by Incorporating Abrasives Grains Into A Matrix, Which CanDocumento7 pagineBonded Abrasives Are Made by Incorporating Abrasives Grains Into A Matrix, Which CanCynthia BerryNessuna valutazione finora

- Experiment No. To Study The Chip Breaker in Machining: Instructional ObjectivesDocumento2 pagineExperiment No. To Study The Chip Breaker in Machining: Instructional Objectivespurushottam prajapatiNessuna valutazione finora

- Abrasive Machining ProcessDocumento13 pagineAbrasive Machining ProcessAbdulRehman Ahmed SoomroNessuna valutazione finora

- Unit-2 Grinding & Super PDFDocumento10 pagineUnit-2 Grinding & Super PDFMehul MunshiNessuna valutazione finora

- Lab 5 Fareez (Grinding Operation)Documento12 pagineLab 5 Fareez (Grinding Operation)s231311024Nessuna valutazione finora

- Mechanical GalvDocumento11 pagineMechanical GalvMehman NasibovNessuna valutazione finora

- Question Paper Code: 21557: Expendable Mold Permanent MoldDocumento20 pagineQuestion Paper Code: 21557: Expendable Mold Permanent MoldAnson AntonyNessuna valutazione finora

- DV03PUB27 Study GuideDocumento5 pagineDV03PUB27 Study GuideJosep TanuNessuna valutazione finora

- Journal - Sumith Cool 3ma19srDocumento8 pagineJournal - Sumith Cool 3ma19srprasanth kumarNessuna valutazione finora

- Die Basics 101 - Part XIII - The FabricatorDocumento5 pagineDie Basics 101 - Part XIII - The FabricatorSIMONENessuna valutazione finora

- Grinding AssignmentDocumento4 pagineGrinding AssignmentSyed Ashmal Hashmi100% (1)

- UNit 3 Part A RevisedDocumento76 pagineUNit 3 Part A Revisedraymon sharmaNessuna valutazione finora

- 54 Lapping & Polishing Basics PDFDocumento7 pagine54 Lapping & Polishing Basics PDFNagi NayakNessuna valutazione finora

- Blanking and PiercingDocumento5 pagineBlanking and PiercingPratap VeerNessuna valutazione finora

- Bearing Car Processing TechnologyDocumento31 pagineBearing Car Processing Technologyamiel cadelinaNessuna valutazione finora

- Processes Involved in Production of Aluminium Sheets: Department of Mechanical EngineeringDocumento29 pagineProcesses Involved in Production of Aluminium Sheets: Department of Mechanical EngineeringSudeepHandikherkarNessuna valutazione finora

- Fact Sheet: METAL REMOVAL/CUTTINGDocumento4 pagineFact Sheet: METAL REMOVAL/CUTTINGAl EnggNessuna valutazione finora

- Best Metal Casting DesignDocumento71 pagineBest Metal Casting DesignVijay Pawar100% (2)

- Selecting A Tube Cutting ProcessDocumento13 pagineSelecting A Tube Cutting ProcessTomás BonelloNessuna valutazione finora

- ME 2252 MANUFACTURING TECHNOLOGY - II-Unit-IV. (B)Documento87 pagineME 2252 MANUFACTURING TECHNOLOGY - II-Unit-IV. (B)Tariq Aziz100% (2)

- AWJCDocumento29 pagineAWJCМарија МиловановићNessuna valutazione finora

- Advanced Manufacturing Process by K.ADocumento24 pagineAdvanced Manufacturing Process by K.AKamesh KPNessuna valutazione finora

- Stamping Design GuidelineDocumento13 pagineStamping Design GuidelineVikram Borkhediya100% (1)

- We Find The Way: Shipping InstructionsDocumento10 pagineWe Find The Way: Shipping InstructionsLuke WangNessuna valutazione finora

- Written Assignment Unit 4 Health ScienceDocumento6 pagineWritten Assignment Unit 4 Health SciencesafsdaNessuna valutazione finora

- Upper Limb OrthosesDocumento29 pagineUpper Limb OrthosesMaryam KhalidNessuna valutazione finora

- OphthalmoplegiaDocumento5 pagineOphthalmoplegiaPatricia Feliani SitohangNessuna valutazione finora

- The Mental MeltdownDocumento5 pagineThe Mental Meltdownapi-460020991Nessuna valutazione finora

- WCC PSV PDFDocumento40 pagineWCC PSV PDFAlejandro RamelaNessuna valutazione finora

- Nursing Care Plan: Assessment Diagnosis Planning Interventions Rationale EvaluationDocumento11 pagineNursing Care Plan: Assessment Diagnosis Planning Interventions Rationale EvaluationDa NicaNessuna valutazione finora

- Chef Basics Favorite RecipesDocumento58 pagineChef Basics Favorite Recipesbillymac303a100% (2)

- Method of Toxicity Test 1Documento59 pagineMethod of Toxicity Test 1Widya AnggrainiNessuna valutazione finora

- Solar Powered Water Pumping System PDFDocumento46 pagineSolar Powered Water Pumping System PDFVijay Nishad100% (1)

- Lesson Plan On Tuberculosis (Health Talk)Documento8 pagineLesson Plan On Tuberculosis (Health Talk)Priyanka Jangra100% (2)

- Cuts of BeefDocumento4 pagineCuts of BeefChristopher EnriquezNessuna valutazione finora

- Poverty and Children's Personal RelationshipsDocumento87 paginePoverty and Children's Personal RelationshipsJoe OgleNessuna valutazione finora

- Clinical Features, Evaluation, and Diagnosis of Sepsis in Term and Late Preterm Infants - UpToDateDocumento42 pagineClinical Features, Evaluation, and Diagnosis of Sepsis in Term and Late Preterm Infants - UpToDatedocjime9004Nessuna valutazione finora

- 8953-Specifications For Doosan Man 9l21 31Documento7 pagine8953-Specifications For Doosan Man 9l21 31Bae Juyeon100% (1)

- Fawad Hussain, Feedback On Industrial Visit To Sahiwal Coal Power PlantDocumento2 pagineFawad Hussain, Feedback On Industrial Visit To Sahiwal Coal Power PlantSyed Fawad MarwatNessuna valutazione finora

- BDC 6566Documento6 pagineBDC 6566jack.simpson.changNessuna valutazione finora

- Photosynthesis PastPaper QuestionsDocumento24 paginePhotosynthesis PastPaper QuestionsEva SugarNessuna valutazione finora

- Sampoong Department Store - A Literary Critique (Mimetic Theory)Documento2 pagineSampoong Department Store - A Literary Critique (Mimetic Theory)Ron Marc CaneteNessuna valutazione finora

- PYMS Is A Reliable Malnutrition Screening ToolsDocumento8 paginePYMS Is A Reliable Malnutrition Screening ToolsRika LedyNessuna valutazione finora

- Plastic Omnium 2015 RegistrationDocumento208 paginePlastic Omnium 2015 Registrationgsravan_23Nessuna valutazione finora

- Content of An Investigational New Drug Application (IND)Documento13 pagineContent of An Investigational New Drug Application (IND)Prathamesh MaliNessuna valutazione finora

- Airport - WikipediaDocumento109 pagineAirport - WikipediaAadarsh LamaNessuna valutazione finora

- Evidence-Based Strength & HypertrophyDocumento6 pagineEvidence-Based Strength & HypertrophyAnže BenkoNessuna valutazione finora

- Practice Test For Exam 3 Name: Miguel Vivas Score: - /10Documento2 paginePractice Test For Exam 3 Name: Miguel Vivas Score: - /10MIGUEL ANGELNessuna valutazione finora

- RIASEC Personality TestDocumento2 pagineRIASEC Personality TestSarah Jane NomoNessuna valutazione finora

- Product Term and ConditionsDocumento50 pagineProduct Term and Conditionsain2Nessuna valutazione finora

- Silage Sampling and AnalysisDocumento5 pagineSilage Sampling and AnalysisG_ASantosNessuna valutazione finora

- Epoxy Data - AF35LVE TDS - ED4 - 11.17Documento8 pagineEpoxy Data - AF35LVE TDS - ED4 - 11.17HARESH REDDYNessuna valutazione finora

- Natu Es Dsmepa 1ST - 2ND QuarterDocumento38 pagineNatu Es Dsmepa 1ST - 2ND QuarterSenen AtienzaNessuna valutazione finora