Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Compact Model Thermal Assited

Caricato da

ruq_mDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Compact Model Thermal Assited

Caricato da

ruq_mCopyright:

Formati disponibili

Zhao et al. Nanoscale Research Letters 2011, 6:368 http://www.nanoscalereslett.

com/content/6/1/368

NANO EXPRESS

Open Access

A compact model for magnetic tunnel junction (MTJ) switched by thermally assisted Spin transfer torque (TAS + STT)

Weisheng Zhao1,2*, Julien Duval1,2, Jacques-Olivier Klein1,2 and Claude Chappert1,2

Abstract Thermally assisted spin transfer torque [TAS + STT] is a new switching approach for magnetic tunnel junction [MTJ] nanopillars that represents the best trade-off between data reliability, power efficiency and density. In this paper, we present a compact model for MTJ switched by this approach, which integrates a number of physical models such as temperature evaluation and STT dynamic switching models. Many experimental parameters are included directly to improve the simulation accuracy. It is programmed in the Verilog-A language and compatible with the standard IC CAD tools, providing an easy parameter configuration interface and allowing high-speed co-simulation of hybrid MTJ/CMOS circuits. Background Spintronics is a very rapidly emerging area of R&D (Nobel Prize 2007) that has the potential to impact significantly on the future of all aspects of electronics beyond CMOS [1]. Magnetic tunnel junctions [MTJ] is one of the most promising spintronic devices for logic and memory applications, which combines magnetism and electronics and promises high write/read speed, non-volatility, infinite endurance etc. [2]. An MTJ is a nanopillar composed of two ferromagnetic [FM] layers and one oxide thin barrier. The Tunnel MagnetoResistance [TMR] phenomenon exists in MTJs [3], which describes the different resistance value RP and RAP corresponding to the parallel or antiparallel configuration of the relative magnetization orientations of the two FM layers, respectively. For practical applications, the magnetization direction of one FM layer is pinned as reference and that of the other FM layer is free to store the binary state (see Figure 1a). Recently, TMR = RAP-RP/RP ratio was found to be more than 604% by using the MgO oxide barrier [4] and this allows MTJ to present excellent sensing performance. Today, most of the R&D efforts in MTJ are focused on its switching approaches, which are expected to be scalable, energy efficient, reliable and fast. A number of

* Correspondence: weisheng.zhao@u-psud.fr 1 IEF, Universit Paris-Sud, 15 Rue Georges Clemenceau, Orsay, 91405, France Full list of author information is available at the end of the article

approaches have been investigated since 2002, such as thermally assisted switching [TAS] [5] and spin transfer torque [STT] [6,7]. However all of them suffer from either high power or stability issue and cannot meet the requirements for wide applications. Thermally assisted spin transfer torque [TAS + STT] is an emerging approach [8,9], which is based on the temperature dependence of exchange bias storage principle [10], as used in TAS [5]. This switching mechanism involves applying a low current through STT to raise the MTJ temperature above the blocking temperature (Tb) of the antiferromagnetic layer associated to the storage layer, resulting in a hysteresis loop centred about zero (see Figure 1). Tb depends mainly on the material composition (e.g. ~423K for IrMn and ~573K for PtMn). This method combines the advantages of both TAS and STT technologies, giving the best tradeoff among data reliability, power efficiency, speed and density. Unlike other nanodevices [11], MTJ can be easily integrated with CMOS circuits [12]. Based on hybrid MTJ/CMOS [13], innovative memory and logic circuits are expected to provide high performance or new functionalities beyond CMOS. A Spice-compatible efficient compact model for MTJ is an essential requirement for the hybrid MTJ/CMOS design and simulation.

Physical model integration This compact model is based on our previous STT MTJ model, which is composed of two sub-modules

2011 Zhao et al; licensee Springer. This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/2.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Zhao et al. Nanoscale Research Letters 2011, 6:368 http://www.nanoscalereslett.com/content/6/1/368

Page 2 of 4

Figure 1 TAS + STT switching approach. (a) The MTJ nanopillar with two antiferromagnetic layers. (b) Bidirectional current switches the MTJ between the parallel and anti-parallel state

representing respectively the sensing and switching operations [14]. For sensing, the MTJ resistance and TMR ratio are calculated to obtain respectively RP and RAP [15]. For switching, the STT critical current, IC, calculation model was implemented to obtain the hysteresis loop margin of storage layer [5]. The present model offers an improvement over the previous work [14-17] as it integrates the temperature evaluation and STT dynamic switching models to describe the TAS + STT switching approach. In order to optimise the simulation speed, one of the most important performances for logic and memory designs, some physical phenomena like the oscillating effects during switching are omitted.

Temperature evaluation model

to Equation 1 has been included to monitor the temperature evaluation of MTJ (see Figure 2a), which is based on a simple resistor/capacitor circuit. By adding a multiplier (M 0 ) and an adder (A 0 ), the temperature T can be observed in real time through the voltage node Vtemp (i.e. 1V = 1K). The values of R0 and C0 are set as constant to obtain th calculated by Equation 2,

Vj dT = (T TR ) + th 2/thick b dt th = Cv thick s 2/thick b

(1)

(2)

The temperature evaluation of MTJ depends on the form and duration of switching current according to Equations 1 and 2 [17,18]. As square current pulses are often used for logic and memory circuit design and simulation, Equation 1 can be then simplified to Equations 3 and 4 to describe respectively the heating and cooling operations driven by a current pulse. This model allows simulating the thermally assisted mechanism of TAS+STT approach. An equivalent electrical circuit corresponding

where V is the voltage across MTJ nanopillar, l is thermal conductivity of the thermal barrier, CV is heat capacity per unit volume, j is current density, T R is room temperature, thick_b is the thickness of thermal barrier, thick_s is the total thickness of MTJ nanopillar and th is the characteristic heating/cooling time. This leads to

Theat = TR + Dheat Vj 1 exp 2/thick b th

(3)

Figure 2 Circuit implementation for modelling and simulation. (a) Equivalent electrical RC circuit of temperature evaluation model. (b) MTJ switching circuit; either Vg1 or Vg2 is set to 1 to generate the current Iswitch. RC, resistor/capacitor

Zhao et al. Nanoscale Research Letters 2011, 6:368 http://www.nanoscalereslett.com/content/6/1/368

Page 3 of 4

Tcool = TR + (Theat TR ) exp

Dcool th

(4)

where Dheat is the heating current pulse duration, Dcool is the cooling duration, and T heat and T cool present respectively temperature of MTJ during heating/cooling operations.

Spin Transfer Torque (STT) dynamic switching model

where Hani is in-plane uniaxial magnetic anisotropy field, 0Ms is saturation field in the storage layer, a is Gilbert damping coefficient, g0 is the gyromagnetic constant, Vol is the volume of storage layer and kB is the Boltzmann constant.

Compact model simulation and validation

Co-simulation of Hybrid MTJ/CMOS circuit

STT dynamic switching behaviours are described by Equations 5 and 6, which are crucial to simulate the power and speed performances of hybrid MTJ/CMOS circuits. Thermal fluctuations induce an initial angle 0 between the magnetization of the storage layer and its easy axis [19], which is approximated by Equation 6. High temperature increases 0 and then reduces the STT switching duration, D switch . STT state reversal depends on switching current value, Iswitch, which should be higher than the critical current, IC. Dswitch can be linearly reduced down to according to nanosecond range with high I switch [20]. This property is useful for the design and simulation of hybrid MTJ/CMOS circuits dedicated to logic applications, which require very high speed (e.g. approximately gigahertz).

Dswitch = 1 IC ln 0 (0 MS ) Iswitch IC 20

(5)

0 =

kB T Hani (0 MS ) Vol

(6)

This compact model has been developed in Verilog-A language and implemented on Cadence Virtuoso CAD platform [21]. Its default parameters correspond to a MTJ nanopillar BiFe(10)/IrMn(6)/CoFeB(1)/MgO(0.85)/CoFeB (3)/PtMn(6). Thanks to the graphical parameter configuration of Verilog-A, MTJ can be set easily with different material and process parameters. By using CMOS 65 nm design-kit, a simple hybrid circuit (see Figure 2b) [22] has been successfully simulated (see Figure 3), which validates the functionalities and behaviours of this model. The voltage pulse Vg1 is activated at 40 ns and Iswitch begins to heat the MTJ from ambient temperature. As its temperature reaches up to Tb2 after ~11.22 ns, the model compares the Iswitch (approx 462.9 uA) with the STT critical current IC (~150 uA) and switches the state of MTJ from parallel [P] to anti-parallel [AP] state in about 6 ns according to the STT dynamic model. As Vg1 is deactivated, MTJ begins to cool down to ambient temperature. The state can be reversed from AP to P by activating the control signal Vg2, which generates Iswitch (approx-375.6uA). The Iswitch values are asymmetric as a constant voltage supply is used in the simulation (e.g. 1V) and the

Figure 3 Transient simulation of compact model. (a) and (b) Control signals activate the circuit to generate bidirectional currents. (c) MTJ is switched between the P and AP. (d) Temperature evaluation. (e) The state of MTJ. P, parallel; AP, anti-parallel.

Zhao et al. Nanoscale Research Letters 2011, 6:368 http://www.nanoscalereslett.com/content/6/1/368

Page 4 of 4

resistance of MTJ changes between two states (RP and RAP). It is important to note that the voltage pulse width should be longer than Dheat+Dswitch to ensure the reliable switching operation [5].

Power and die area estimation

8. 9.

10.

2

The silicon area of this hybrid circuit is ~9.8 um as the width of NMOS transistors is set to 1 m to provide I switch much higher than I C and reduce the duration down to some nanoseconds. The whole switching operation of TAS + STT between the P and AP states dissipates ~2.7pJ of energy.

11.

12.

13.

Conclusions In this paper, we present the first compact model for MTJ nanopillar switching using the TAS+STT approach. Transient simulations of a hybrid MTJ/CMOS circuit validate its functionalities and demonstrate that it can be useful to calculate the critical circuit performances like speed, power and die area. The easy parameter interface of the Verilog-A language allows us to analyse the characteristics of MTJ with different materials, area and thin film thickness etc. By using this model, a number of hybrid MTJ/CMOS complex circuits are under investigation in our laboratory.

Acknowledgements The authors wish to acknowledge support from the French national projects CILOMAG, ANR-SPIN and NANO2012 project with STMicroelectronics. Author details 1 IEF, Universit Paris-Sud, 15 Rue Georges Clemenceau, Orsay, 91405, France 2 UMR8622, CNRS, Batiment 220, Campus dOrsay, 91405, France Authors contributions ZWS, KJO and CC designed the modelling. DJ programmed the model. ZWS and DJ performed the simulation and wrote the manuscript. Competing interests The authors declare that they have no competing interests. Received: 2 November 2010 Accepted: 28 April 2011 Published: 28 April 2011 References 1. Chappert C, Fert A, Nguyen Van Dau F: The emergence of spin electronics in data storage. Nat Mater 2007, 6:813-823. 2. Zhao WS, Belhaire E, Chappert C, Mazoyer P: Spin transfer torque (STT)MRAM-based runtime reconfiguration FPGA circuit. ACM Trans Embedded Computing 2009, 9, article 14. 3. Julliere M: Tunnelling between ferromagnetic films. Phys Lett 1975, 54A:225-226. 4. Ikeda S, Hayakawa J, Ashizawa Y, Lee YM, Miura K, Hasegawa H, Tsunoda M, Matsukura F, Ohno H: Tunnel magnetoresistance of 604% at 300 K by suppression of Ta diffusion in CoFeB/MgO/CoFeB pseudo-spin-valves annealed at high temperature. Appl Phys Lett 2008, 93:082508. 5. Prejbeanu IL, Kerekes M, Sousa RC, Sibuet H, Redon O, Dieny B, Nozire JP: Thermally assisted MRAM. J Phys Condensed Matter 2007, 19:165218. 6. Slonczewski JC: Current-drivern excitation of magnetic multilayers. J Magnetism Magnetic Mater 1996, 159:L1-L7. 7. Hayakawa J, Ikeda S, Lee YM, Sasaki R, Meguro T, Matsukara F, Takahashi H, Ohno H: Jpn J Appl Phys 2005, 44:L1267-L1270.

14.

15.

16. 17.

18.

19. 20.

21. 22.

Xi HW, Stricklin J, Li H, Chen YR, Wang XB, Zheng YK, Gao Z, Tang MX: IEEE Trans Magn 2010, 46:860-866. Dieny B, Sousa RC, Herault J, Papusoi C, Prenat G, Ebels U, Houssameddine D, Rodmacq B, Auffret S, Buda-Prejbeanu LD, Cyrille MC, Delaet B, Redon O, Ducruet C, Nozires JP: Spin-transfer effect and its use in spintronic components. Int J Nanotechnol 2010, 7:591-614. Chen YT: The Effect of Interface Texture on Exchange Biasing in Ni(80) Fe(20)/Ir(20)Mn(80) System. Nanoscale Res Lett 2009, 4:90-93. Navi K, Rashtian M, Khatir A, Keshavarzian P, Hashemipour O: High Speed Capacitor-Inverter Based Carbon Nanotube Full Adder. Nanoscale Res Lett 2010, 5:859-862. Matsunaga S, Hayakawa J, Ikeda S, Miura K, Hasegawa H, Endoh T, Ohno H, Hanyu T: Fabrication of a Nonvolatile Full Adder Based on Logic-inMemory Architecture Using Magnetic Tunnel Junctions. Appl Phys Exp 2008, 1:091301. Zhao WS, Chappert C, Javerliac V, Nozire J-P: High Speed, High Stability and Low Power Sensing Amplifier for MTJ/CMOS Hybrid Logic Circuits. IEEE Trans Magn 2009, 45:3784-3787. Zhao WS, Belhaire E, Mistral Q, Chappert C, Javerliac V, Dieny B, Nicolle E: Macro-model of Spin-Transfer Torque based Magnetic Tunnel Junction device for hybrid Magneti-CMOS design. Procedings of the 2006 IEEE International Behavioral Modeling and simulation Workshop San Jose CA; 2006, 40-43. Elbaraji M, Javerliac V, Guo W, Prenat G, Dieny B: Dynamic compact model of thermally assisted switching magnetic tunnel junctions. J Appl Phys 2010, 106:123906. Das B, Black WC Jr, Pohm AV: Universal HSPICE macromodel for giant magnetoresistance memory bits. IEEE Trans Magn 2000, 36:2062-2072. Roldan AM, Roldan JB, Reig C, Cubells-Beltran MD, Ramirez D, Cardoso S, Freitas PP: A DC behavioral electical model for quasi-linear spin-valve devices including thermal effects for circuit simulation. Microelectron J 2011, 42:365-370. Sousa RC, Prejbeanu IL, Stanescu D, Rodmacq B, Redon O, Dieny B, Wang JG, Freitas PP: Tunneling hot spots and heating in magnetic tunnel junctions. J Appl Phys 2004, 95:6783-6785. Koch RH, Katine JA, Sun JZ: Time-Resolved Reversal of Spin-Transfer Switching in a Nanomagnet. Phys Rev Lett 2004, 92:088302. Devolder T, Hayakawa J, Ito K, Takahashi H, Ikeda S, Crozat P, Zerounian N, Kim JV, Chappert C, Ohno H: Single-Shot Time-Resolved Measurements of Nanosecond-Scale Spin-Transfer Induced Switching: Stochastic Versus Deterministic Aspects. Phys Rev Lett 2008, 100:057206. Virtuoso Spectre Circuit Simulator User Guide: 2006. Zhao WS, Belhaire E, Chappert C, Mazoyer P: Power and Area Optimization for Run-Time Reconfiguration System On Programmable Chip Based on Magnetic Random Access memory. IEEE Trans Magn 2009, 45:776-780.

doi:10.1186/1556-276X-6-368 Cite this article as: Zhao et al.: A compact model for magnetic tunnel junction (MTJ) switched by thermally assisted Spin transfer torque (TAS + STT). Nanoscale Research Letters 2011 6:368.

Submit your manuscript to a journal and benet from:

7 Convenient online submission 7 Rigorous peer review 7 Immediate publication on acceptance 7 Open access: articles freely available online 7 High visibility within the eld 7 Retaining the copyright to your article

Submit your next manuscript at 7 springeropen.com

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5795)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1091)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- IVQM说明书(20220312) PDFDocumento15 pagineIVQM说明书(20220312) PDFGatheru Kamanja StephenNessuna valutazione finora

- Energy Audit Report PPUMDocumento39 pagineEnergy Audit Report PPUMMuhammad Faiz bin Ahmad ShafiNessuna valutazione finora

- Luxreal Malaysia Membership FormDocumento1 paginaLuxreal Malaysia Membership Formkalai arasanNessuna valutazione finora

- About Me: Chaitanya PatilDocumento2 pagineAbout Me: Chaitanya PatilRushi PatilNessuna valutazione finora

- Literature Review For Hris ProjectDocumento7 pagineLiterature Review For Hris Projecte9xy1xsv100% (1)

- Proofreader ResumeDocumento4 pagineProofreader Resumef5dct2q8100% (2)

- BGP QuestionsDocumento8 pagineBGP Questionsstorm2010Nessuna valutazione finora

- Study On Blockchain Visualization: VOL 1 (2017) NO 3 e-ISSN: 2549-9904 ISSN: 2549-9610Documento7 pagineStudy On Blockchain Visualization: VOL 1 (2017) NO 3 e-ISSN: 2549-9904 ISSN: 2549-9610Adnan WahabNessuna valutazione finora

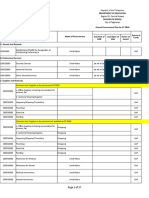

- Annual Procurement PlanDocumento27 pagineAnnual Procurement PlanLiezl Bachicha RaquizaNessuna valutazione finora

- EJ1098600Documento7 pagineEJ1098600Che Mohammad Fattihi Ekhmal Bin Che MutNessuna valutazione finora

- CompTIA Security Certification Practice Test 2 Exam SY0 601Documento5 pagineCompTIA Security Certification Practice Test 2 Exam SY0 601Allondra Lado-anNessuna valutazione finora

- Excel Formulae and FunDocumento8 pagineExcel Formulae and FunYeeXuan TenNessuna valutazione finora

- Office-Administration Certificate ProgrammeDocumento21 pagineOffice-Administration Certificate ProgrammeZakia AikazNessuna valutazione finora

- FALCO - Spesifikasi PC Server VAULT-2019Documento1 paginaFALCO - Spesifikasi PC Server VAULT-2019Sales AdministratorNessuna valutazione finora

- MSeries Model MC420Documento6 pagineMSeries Model MC420galih santosoNessuna valutazione finora

- ITSC Seminar - 27001 27002 Update Philip SyDocumento30 pagineITSC Seminar - 27001 27002 Update Philip SySyed ZiaNessuna valutazione finora

- Training and Placement Cell: Instructions & CV GuidelinesDocumento6 pagineTraining and Placement Cell: Instructions & CV GuidelinesakjsdfbaNessuna valutazione finora

- DS ANT TNA770A00Rx 190801 ENDocumento3 pagineDS ANT TNA770A00Rx 190801 ENakiselNessuna valutazione finora

- Verilog Cheat Sheet: S Winberg and J TaylorDocumento2 pagineVerilog Cheat Sheet: S Winberg and J TaylorMohamed ElsahatNessuna valutazione finora

- Understanding Cryptography SOLUTIONSDocumento26 pagineUnderstanding Cryptography SOLUTIONSzumri82% (17)

- 59th Annual Fuze ConferenceDocumento5 pagine59th Annual Fuze ConferenceedweeryNessuna valutazione finora

- OpenQuake Manual 3.6Documento193 pagineOpenQuake Manual 3.6anon_897435228Nessuna valutazione finora

- LSP All ExperimentsDocumento60 pagineLSP All Experimentsaishwaryapradeep03Nessuna valutazione finora

- Aveva Intouch Access Anywhere Server Administrator ManualDocumento47 pagineAveva Intouch Access Anywhere Server Administrator Manualel misNessuna valutazione finora

- PracticalsDocumento31 paginePracticalsprogrammerNessuna valutazione finora

- Thesis Presentation Slides UNIBGDocumento33 pagineThesis Presentation Slides UNIBGRomeo DanielsNessuna valutazione finora

- Object Oriented Programming 1Documento14 pagineObject Oriented Programming 1rahul rastogiNessuna valutazione finora

- Quick Reference Guide PDFDocumento4 pagineQuick Reference Guide PDFCarlos QuispeNessuna valutazione finora

- CSE2045Y Web Application Development: XSD (XML Schema Definition)Documento22 pagineCSE2045Y Web Application Development: XSD (XML Schema Definition)splokbovNessuna valutazione finora

- Cache Ques BDocumento1 paginaCache Ques BNishant BhartiNessuna valutazione finora