Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Exp.1 FET Amp

Caricato da

Loryliza M DeiparineDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Exp.1 FET Amp

Caricato da

Loryliza M DeiparineCopyright:

Formati disponibili

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

ECE 434: Electronics II Laboratory Department of Electronics/VocTech, College of Engineering Liceo de Cagayan University DESCRIPTION: This course presents laboratory experiments for electronic circuits analysis and design. Experiments in detail will provide output on High frequency transistor models; analysis of transistor circuits; multi-stage amplifier, feedback, differential amplifiers and operational amplifiers. Lory Liza D. Bulay-og, PECE, MOE Email: lmd_bulayog@yahoo.com 1 Units (3 Hours per week) ECE 314L At the end of the semester the students will be able to: GRADING SYSTEM: PASSING PERCENTAGE: 60% LABORATORY POLICIES: Illustrate through graphs and waveforms the frequency response of transistor models. Explain in the detail the concept of different transistor circuit base on actual results. Design amplifier circuits using operational amplifiers.

INSTRUCTOR:

CREDIT UNITS: CO-REQUISITE: OBJECTIVES:

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

NAME: ___________________________ GROUP NUMBER:___________________ LABORATORY SCHEDULE OF ACTIVITIES Experiment No. 1 2 Experiment Title JFET Voltage Amplifier Characteristics JFET Frequency Response Target Date June 29 July 6

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

JFET Voltage Amplifier Characteristics

Experiment No. 1 Objectives 1. Construct and test a voltage amplifier using N-channel JFET device in a common source configuration 2. Apply the voltage divider biasing method to set the DC operating point (VGSq , IDSq) 3. Verify the estimated DC operating point with the measured data. 4. Determine the voltage gain of the N-channel JFET common source configuration.

Materials: Equipment required Power Supply Oscilloscope Digital Multimeter Breadboard Function Generator 1 1 1 1 1 Components required N-channel JFET 2N5457 Resistor 10k (1/4W) Resistor 3.3k (1/4W) Resistor 3.9k (1/4W) Resistor 22k (1/4W) Mylar Capacitor 0.47 F Mylar Capacitor 0.1F Mylar Capacitor 0.01F 50 k potentiometer 1 2 1 1 1 2 1 1 - 1

Important Notes All related calculation questions that does not require experimental data must be answered before coming to the lab. You are required to show all the calculation steps when requested by the lab instructor. During the evaluation session, your lab instructor may request you to demonstrate how the measurement data is obtained and explain your experimental results. You are advised to attempt the theoretical questions asked in the lab sheet before coming to the lab. The lab session is only 3 hours and will be mostly spend on collecting experiment data, analyzing result and comparing the data with the calculated value. Before coming to the lab, you will also need to study the related theory. In order to answer the questions in the labsheet, you also need to make reading preparation.

Background Theory An amplifier is a circuit that increases/decrease the input signal value and in this experiment the signal to be amplified is the voltage. In this experiment you are going to investigate the voltage gain and impedance characteristics of a voltage amplifier circuit using the N-channel JFET device

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

Figure/Schematic Diagram:

+VDD=12V 0.1F CH1 (vin) R1=22k RD=3.3k D G CG=0.47F Vgen R2 =10k RS=3.9k S RL=10k CS=0.47F CD=0.01F CH2 (vL)

Function Generator 50

Figure 1: A common source JFET amplifier

Procedures:

1.

2.

3.

4.

5.

6.

7.

Before connecting the circuit of Figure 1, measure the actual resistance of R1, R2, RD, RS and RL as accurate as possible with a digital multimeter (set it to the best resistance range) and record the measured values. Connect the common source JFET amplifier circuit as shown in Figure 1 using a breadboard. Do not connect the power supply and the function generator to the circuit yet. Keep the connecting wires on the breadboard as short as possible (< 3 cm) to reduce unwanted inductance and capacitance in your circuit. Set the power supply output to +12V. Connect its output to the circuit and measure its voltage VDD(meas) as accurate as possible with the multimeter. Calculate the gate DC voltage VG(cal) using the voltage-divider rule. Measure the DC voltages VG, VD and VS at G, D, and S pins of the transistor as accurate as possible. Note that the measured VG should be closed to the calculated VG(cal), and VS should be > VG since VGS must be < 0 V for N-channel JFET. Before connecting the function generator to the circuit, use an oscilloscope to measure the output voltage of the generator and set it to 200 kHz sine-wave with a peak-to-peak voltage of 0.1V. Press the attenuation button (ATT) of the generator for easy adjustment of its output voltage. Record it as voltage input. Connect the generator output to the circuit. Using Channel 1 (CH1) of the oscilloscope (set at AC input coupling), probe the input voltage vin. Using Channel 2 (CH2) of the oscilloscope, probe the load resistor RL, as shown in Figure 1. Set the trigger source of the oscilloscope to CH2. Adjust the trigger level on the oscilloscope to obtain stable waveforms. Make sure the variable (VAR) knobs of the oscilloscope are set at the calibrated (CALD) positions. Adjust the Volts/div and Time/div to display the waveforms on the oscilloscope screen as big as possible with one to two cycles. Sketch the input AC voltage (vin) and the load voltage (vL) waveforms on the graph. Record the Time/div and Volts/div used. Note that the

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

input and output waveforms should be approximately 180o out of phase. 8. From your graph, determine VL(pp) and Vin(pp) which are the peak-to-peak voltages of vL and vin, respectively. Calculate the voltage gain (Av) of the JFET amplifier circuit at 200 kHz. Ask the instructor to check all of your results. You must show the oscilloscope waveforms to the instructor. Preliminary Data/Results/Computation:

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

Date Performed: ___________

Faculty Signature: _________________

JFET Amplifier Frequency Response

Experiment No. 2 Objectives 1. Investigate the effect of frequency changes on the voltage gain of the amplifier, measure its frequency response and obtain its operating bandwidth. 2. Investigate the capacitance effect on the frequency response of the common source JFET amplifier

Materials: Equipment required Power Supply Oscilloscope Digital Multimeter Breadboard Function Generator 1 1 1 1 1 Components required N-channel JFET 2N5457 Resistor 10k (1/4W) Resistor 3.3k (1/4W) Resistor 3.9k (1/4W) Resistor 22k (1/4W) Mylar Capacitor 0.47F Mylar Capacitor 0.1F Mylar Capacitor 0.01F 50 k potentiometer 1 2 1 1 1 2 1 1 - 1

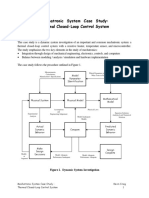

Background Theory Most amplifiers have relatively constant gain over a certain range of frequencies. This range of frequencies is called the bandwidth of the amplifier. The bandwidth for a given amplifier depends on the circuit component values, the type of active components and the dc operating point of the active component. When an amplifier is operated within its bandwidth, the current gain ( Ai ) , voltage gain ( Av ) , and power gain A p values are referred to as midband gain values. A simplified frequency-response curve that represents the relationship between amplifier gain and operating frequency is shown in Figure 1.

( )

Power Gain

Ap drops at lower frequencies Mid-band

Ap drops at higher frequencies

Ap(mid)

0.5Ap(mid)

Bandwidth

fc1

Frequency

fc2

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

Figure 1: A simplified frequency response curve

As the frequency-response curve shows, the power gain of an amplifier remains relatively constant across a band of frequencies. When the operating frequency starts to go outside this frequency range, the gain begins to drop. Two frequencies of interest, f c1 and

f c 2 , are the frequencies at which power gain decreases to approximately 50% of A p (mid ) . The frequencies labeled f c1 and f c 2 are called the lower and upper cutoff frequencies of

an amplifier, respectively. These frequencies are considered to be the bandwidth limits for the amplifier and thus bandwidth BW is given by

The geometric average of f c1 amplifier, given by

BW = f c 2 f c1 . and f c 2 is called the geometric center frequency fo of an f0 = f c1 f c 2 .

When the operating frequency is equal to f 0 , the power gain of the amplifier is at its maximum value. Frequency response curves and specification sheets often list gain values that are measured in decibels (dB). The dB power gain of an amplifier is given by

A p ( dB ) = 10 log A p = 10 log

Pout . Pin

Positive and negative decibels of equal magnitude represent reciprocal gains and losses. A +3dB gain caused power to double while a 3dB gain caused power to be cut in half. Using the basic power relationships, Pout rewritten as

2 2 v out vin = and Pin = , the power gain may be RL Rin

A p ( dB ) = 10 log

v R Pout v2 R = 10 log out L = 20 log out + 10 log in 2 vin RL Pin v in Rin

The voltage component of the equation is referred to as dB voltage gain. When the amplifier input and out resistances are equal

A p ( dB ) = 20 log

vout = Av ( dB ) . vin

( Rin = RL )

Thus, when the voltage gain of an amplifier changes by 3dB, the power gain of the amplifier also changes by 3dB.

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

Figure/Schematic Diagram:

+VDD=12V 0.1F CH1 (vin) R1=22k RD=3.3k D G CG=0.47F Vgen R2 =10k RS=3.9k S RL=10k CS=0.47F CD=0.01F CH2 (vL)

Function Generator 50

Figure 1: A common source JFET amplifier

Pre-Experiment Procedure: Do the procedure in experiment No.1 (or refer to the data gathered in experiment No.1) Procedures: 1. Sweep the frequency of the function generator from 1 kHz to 550 kHz (use smaller frequency steps near the half-power point while larger steps can be used at mid-band frequencies). Record the peak-to-peak voltages of vin (CH1) and vL (CH2) and calculate the dB magnitude of the voltage gain Av. Use both coarse and fine adjustment knobs of the function generator for frequency adjustment. 2. Plot a curve of Av versus frequency. 3. Calculate the lower cutoff frequency fLD(cal) (use the measured RD and RL values). Set the frequency to 20 kHz. To measure the lower cutoff frequency (fLD), decrease the generator frequency until VL(pp) decreases to 0.707VL,mid-band(pp), where VL,mid-band(pp) is the VL(pp) value in the mid-band. 4. Set the frequency to 300 kHz. To measure the upper cutoff frequency (fHD), increase the generator frequency until VL(pp) decreases to 0.707VL,mid-band(pp). 5. Determine the bandwidth (BW) and the geometric center frequency (fo) of the amplifier from the above measurements. Ask the instructor to check all of your results. You must show the oscilloscope waveforms at 550 kHz to the instructor. 6. Design or modify the circuit in Figure 5 in order to measure the parameter of the device, namely Gate-Source Cutoff Voltage (VGS(off) or Vp ) and Zero-Gate Voltage Current (IDSS) . These two values can be used in the Shockley equation ID = IDSS ( 1 VGS/Vp)2 . Hint: You can use a potentiometer and/or negative power source in the circuit. By solving the simultaneous equation of the Shockley equation and the load line equation, you can

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

obtain the calculated value for the Q point VGSQ, VDSQ, IDQ. . Compare this with the measured value.

Preliminary Data/Results/Computation:

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

10

Date Performed: ___________ Name: _______________________ Submitted:_____ Group No.: ____________________

Faculty Signature: _________________ Date Rating: ___________

JFET Voltage Amplifier Characteristics

Experiment No. 1 Objectives 1. Construct and test a voltage amplifier using N-channel JFET device in a common source configuration. 2. Apply the voltage divider biasing method to set the DC operating point (VGSq , IDSq) 3. Verify the estimated DC operating point with the measured data. 4. Determine the voltage gain of the N-channel JFET common source configuration.

Materials: Equipment required Power Supply Oscilloscope Digital Multimeter Breadboard Function Generator 1 1 1 1 1 Components required N-channel JFET 2N5457 Resistor 10k (1/4W) Resistor 3.3k (1/4W) Resistor 3.9k (1/4W) Resistor 22k (1/4W) Mylar Capacitor 0.47 F Mylar Capacitor 0.1F Mylar Capacitor 0.01F 50 k potentiometer 1 2 1 1 1 2 1 1 - 1

Data, Results, Calculation and Observation: Procedure No. 1

R1 R2 RD RS RL

= __________________ = __________________ = __________________ = __________________ =__________________

Procedure No. 3

VDD(meas) VG(cal)

Computation:

= ____________ = __________________

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

11

Procedure No. 4

VG VD VS

= _______________________ =_______________________ =_______________________

Procedure No. 7 Waveform:

i.

AC voltage (vin)

ii.

load voltage (vL)

Data:

i. Time/div (used) ii. Volts/div (used)

= ____________________ = ____________________

Procedure No. 8

VL(pp) Vin(pp) Av(comp) Computation:

= _______________________ =_______________________ =_______________________

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

12

JFET Amplifier Frequency Response

Experiment No. 2 Objectives 1. Investigate the effect of frequency changes on the voltage gain of the amplifier, measure its frequency response and obtain its operating bandwidth. 2. Investigate the capacitance effect on the frequency response of the common source JFET amplifier

Materials: Equipment required Power Supply Oscilloscope Digital Multimeter Breadboard Function Generator 1 1 1 1 1 Components required N-channel JFET 2N5457 Resistor 10k (1/4W) Resistor 3.3k (1/4W) Resistor 3.9k (1/4W) Resistor 22k (1/4W) Mylar Capacitor 0.47F Mylar Capacitor 0.1F Mylar Capacitor 0.01F 50 k potentiometer 1 2 1 1 1 2 1 1 - 1

Data, Results, Calculation and Observation: Procedure No. 1 vin (CH1) vL (CH2) Av = _____________________ = _____________________ = _____________________ (dB magnitude of the voltage gain)

Computation:

Procedure No. 2 (Plot Curve of Av versus frequency)

Liceo de Cagayan University College of Engineering Electronics II Laboratory Manual

13

Procedure No. 3 fLD(cal) = ________________ lower cutoff frequency (calculated) fLD(meas) = ________________ lower cutoff frequency (measured)

Computation:

Procedure No. 4 fHD

= _______________ upper cutoff frequency (measured)

Potrebbero piacerti anche

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- ECE 413quiz (FT)Documento2 pagineECE 413quiz (FT)Loryliza M DeiparineNessuna valutazione finora

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Quiz No1comm3Documento1 paginaQuiz No1comm3Loryliza M DeiparineNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (894)

- Take Home QuizDocumento1 paginaTake Home QuizLoryliza M DeiparineNessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- SymbolsDocumento28 pagineSymbolsLoryliza M DeiparineNessuna valutazione finora

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- ERKC PB Smart Cities PDFDocumento40 pagineERKC PB Smart Cities PDFLoryliza M DeiparineNessuna valutazione finora

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- STEM - Basic Calculus CG PDFDocumento5 pagineSTEM - Basic Calculus CG PDFReyVirgoReyes60% (5)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Wireless Communication TechnologyDocumento590 pagineWireless Communication TechnologyJeffrey Zhang100% (1)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- MCQ Son Power ElectronicsDocumento2 pagineMCQ Son Power ElectronicsNoor AhmedNessuna valutazione finora

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Chapter12 PDFDocumento10 pagineChapter12 PDFNarender SinghNessuna valutazione finora

- ECE 322ME - Summer05112018Documento2 pagineECE 322ME - Summer05112018Loryliza M DeiparineNessuna valutazione finora

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- PulsestuffingDocumento45 paginePulsestuffingvishalp6Nessuna valutazione finora

- Microwave Communication SystemDocumento93 pagineMicrowave Communication SystemMark Bryan Hermida Cruz100% (2)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Propagation of Radio WavesDocumento48 paginePropagation of Radio WavesLoryliza M DeiparineNessuna valutazione finora

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Thermal System Case StudyDocumento30 pagineThermal System Case StudyLoryliza M DeiparineNessuna valutazione finora

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- ICMP, ARP and DHCP protocols explainedDocumento48 pagineICMP, ARP and DHCP protocols explainedLoryliza M DeiparineNessuna valutazione finora

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- QB DC1Documento19 pagineQB DC1Loryliza M DeiparineNessuna valutazione finora

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Examination + answers: Mechatronic System Design Course ExamDocumento6 pagineExamination + answers: Mechatronic System Design Course ExamLoryliza M DeiparineNessuna valutazione finora

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- Ece 511final Exam - Oct2017printingDocumento3 pagineEce 511final Exam - Oct2017printingLoryliza M DeiparineNessuna valutazione finora

- Chapter 1Documento41 pagineChapter 1Loryliza M DeiparineNessuna valutazione finora

- Mobile Communication 2-MARK Questions and AnswersDocumento16 pagineMobile Communication 2-MARK Questions and Answersnoblelion92% (12)

- Serial Interface RS-449Documento17 pagineSerial Interface RS-449Loryliza M DeiparineNessuna valutazione finora

- Resistance Limit For Several Types of ExchangeDocumento1 paginaResistance Limit For Several Types of ExchangeLoryliza M DeiparineNessuna valutazione finora

- Introduction and Light Propagation in Optical Fibers 17.03.2011Documento63 pagineIntroduction and Light Propagation in Optical Fibers 17.03.2011Loryliza M DeiparineNessuna valutazione finora

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Lecture 17Documento13 pagineLecture 17Loryliza M DeiparineNessuna valutazione finora

- Lecture 2Documento9 pagineLecture 2Loryliza M DeiparineNessuna valutazione finora

- Lecture 3Documento4 pagineLecture 3Loryliza M DeiparineNessuna valutazione finora

- Lecture 1: Transmission MediaDocumento10 pagineLecture 1: Transmission MediaLoryliza M DeiparineNessuna valutazione finora

- Lecture 3Documento4 pagineLecture 3Loryliza M DeiparineNessuna valutazione finora

- Signal and Data Processing Circuit Assignment Od 014co: 1. ERICK KASHOMA 130222433439 2. MARSEL COSTANTINE 130222421203Documento11 pagineSignal and Data Processing Circuit Assignment Od 014co: 1. ERICK KASHOMA 130222433439 2. MARSEL COSTANTINE 130222421203Loryliza M DeiparineNessuna valutazione finora

- Lecture 2Documento9 pagineLecture 2Loryliza M DeiparineNessuna valutazione finora

- Coal Carbonization: Current and Future ApplicationsDocumento9 pagineCoal Carbonization: Current and Future ApplicationsVenkata Krishnan RamanujamNessuna valutazione finora

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Molecular Shapes and BondingDocumento24 pagineMolecular Shapes and BondingSandunil JayasingheNessuna valutazione finora

- Introduction To Chemical CleaningDocumento28 pagineIntroduction To Chemical Cleaningmordidomi0% (1)

- Boiler Performance Guarantee R0Documento3 pagineBoiler Performance Guarantee R0Prafitri KurniawanNessuna valutazione finora

- Raising New Generation Leaders Through Mechanics EducationDocumento88 pagineRaising New Generation Leaders Through Mechanics EducationOluwaferanmi OgunleyeNessuna valutazione finora

- Statistical and Thermal Physics Fundamentals and ApplicationsDocumento13 pagineStatistical and Thermal Physics Fundamentals and Applicationsgul jahanNessuna valutazione finora

- 2D Compressible Viscous-Flow Solver On Unstructured Meshes With Linear and Quadratic Reconstruction of Convective FluxesDocumento77 pagine2D Compressible Viscous-Flow Solver On Unstructured Meshes With Linear and Quadratic Reconstruction of Convective FluxeshityouNessuna valutazione finora

- Oct 2022 P4 Model AnswerDocumento25 pagineOct 2022 P4 Model AnswerabiyyaNessuna valutazione finora

- Chemistry Project XIIDocumento13 pagineChemistry Project XIIKanav MalhotraNessuna valutazione finora

- Recent Advancements in Aircraft Engine Health Management (EHM) Technologies and Recommendations For The Next StepDocumento13 pagineRecent Advancements in Aircraft Engine Health Management (EHM) Technologies and Recommendations For The Next StepDanu MamlukatNessuna valutazione finora

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Caustic Stress Corrosion Cracking of A Graphite Cast Iron ComponentDocumento8 pagineCaustic Stress Corrosion Cracking of A Graphite Cast Iron Componentriza9847Nessuna valutazione finora

- Simple Lifting Machines MyDocumento14 pagineSimple Lifting Machines MyAkash SinghNessuna valutazione finora

- 316 316l Data SheetDocumento2 pagine316 316l Data SheetDiman Aditya KardiNessuna valutazione finora

- L&T Project ReportDocumento48 pagineL&T Project Reportdeepakarora201188Nessuna valutazione finora

- Exploration Archaeology (John M. Stanley)Documento4 pagineExploration Archaeology (John M. Stanley)henarroNessuna valutazione finora

- Joint Probability Distributions and Random SamplesDocumento22 pagineJoint Probability Distributions and Random SamplesChandrahasa Reddy Thatimakula100% (1)

- Shirokov 2020 IOP Conf. Ser. Mater. Sci. Eng. 775 012148Documento8 pagineShirokov 2020 IOP Conf. Ser. Mater. Sci. Eng. 775 012148Tomás de AlmeidaNessuna valutazione finora

- LMG Polyurethane Resins For LPDocumento8 pagineLMG Polyurethane Resins For LPLeso Sasa DamljanovicNessuna valutazione finora

- Wind Loading of Industrial, Mining and Petrochemical StructuresDocumento16 pagineWind Loading of Industrial, Mining and Petrochemical StructuresapirakqNessuna valutazione finora

- Inductance Part 1 - MowryDocumento4 pagineInductance Part 1 - MowryJacky FanNessuna valutazione finora

- Cat To-4Documento65 pagineCat To-4srcattozziNessuna valutazione finora

- Trapezoidal Rule and Simpson's RuleDocumento5 pagineTrapezoidal Rule and Simpson's RuleSai VandanaNessuna valutazione finora

- 3se3 100-1caDocumento5 pagine3se3 100-1cadainheniNessuna valutazione finora

- Refractory Degradation in Glass Tank Melters. A Survey of Testing MethodsDocumento5 pagineRefractory Degradation in Glass Tank Melters. A Survey of Testing MethodsRizqi Ahmad FauzanNessuna valutazione finora

- GE6251 Basic Civil and Mechanical Engineering Regulation 2013 Lecture NotesDocumento112 pagineGE6251 Basic Civil and Mechanical Engineering Regulation 2013 Lecture NotesSasi Dharan100% (1)

- Polarization Index TestDocumento3 paginePolarization Index TestShahriar AhmedNessuna valutazione finora

- White-IntroductionToAtomicSpectra Text PDFDocumento472 pagineWhite-IntroductionToAtomicSpectra Text PDFShital SahareNessuna valutazione finora

- LV 2000LowVolumeDocumento2 pagineLV 2000LowVolumeDian MiauNessuna valutazione finora

- b3 g1 Gummy Bear Launcher Written UpDocumento6 pagineb3 g1 Gummy Bear Launcher Written Upapi-462982749Nessuna valutazione finora

- AkzoNobel EBS 481 FQ tcm54-30339Documento1 paginaAkzoNobel EBS 481 FQ tcm54-30339Nissim Hazar CasanovaNessuna valutazione finora

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeDa EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeValutazione: 5 su 5 stelle5/5 (8)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDa EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionValutazione: 4.5 su 5 stelle4.5/5 (542)

- High Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsDa EverandHigh Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsValutazione: 4 su 5 stelle4/5 (1)

- The Rare Metals War: the dark side of clean energy and digital technologiesDa EverandThe Rare Metals War: the dark side of clean energy and digital technologiesValutazione: 5 su 5 stelle5/5 (2)

- C++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingDa EverandC++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingValutazione: 4 su 5 stelle4/5 (1)

- Off-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemDa EverandOff-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemNessuna valutazione finora

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDa EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionValutazione: 4 su 5 stelle4/5 (331)

- Understanding Automotive Electronics: An Engineering PerspectiveDa EverandUnderstanding Automotive Electronics: An Engineering PerspectiveValutazione: 3.5 su 5 stelle3.5/5 (16)