Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Finite State Machine (FSM) : Example

Caricato da

Wei ZhangDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Finite State Machine (FSM) : Example

Caricato da

Wei ZhangCopyright:

Formati disponibili

27/03/2012

Finite State Machine (FSM) When the sequence of actions in your design depend on the state of sequential elements, a finite state machine (FSM) can be implemented FSMs are widely used in applications that require prescribed sequential activity

Example:

Sequence Detector Fancy counters Traffic Light Controller Data-path Controller Device Interface Controller etc.

Finite State Machine (FSM) (cont.) All state machines have the general feedback structure consisting of:

Combinational logic implements the next state logic

Next state (ns) of the machine is formed from the current state (cs) and the current inputs

State register holds the value of current state

Next State Inputs

Next-State Logic

Memory

Current State

27/03/2012

Types of State Machines Moore State Machine

Inputs

ns Next-State Logic State Register

cs Output Logic

Outputs

Next state depends on the current state and the inputs but the output depends only on the present state

next_state(t) = h(current_state(t), input(t)) output = g(current_state(t))

Types of State Machines (cont.) Mealy State Machine

Output Logic

Inputs

ns Next-State Logic State Register

cs

Outputs

Next state and the outputs depend on the current state and the inputs

next_state(t) = h(current_state(t), input(t)) output(t) = g(current_state(t), input(t))

27/03/2012

Typical Structure of a FSM

module mod_name ( ); input ; output ; parameter size = ; reg [size-1: 0] current_state; wire [size-1: 0] next_state; // State definitions `define state_0 2'b00 `define state_1 2b01 always @ (current_state or the_inputs) begin // Decode for next_state with case or if statement // Use blocked assignments for all register transfers to ensure // no race conditions with synchronous assignments end always @ (negedge reset or posedge clk) begin if (reset == 1'b0) current_state <= state_0; else current_state <= next_state; end //Output assignments endmodule

Next State Logic

State Register

Sequence Detector FSM

Functionality: Detect two successive 0s or 1s in the serial input bit stream

reset reset_state 0 1

out_bit = 0

1

FSM Flow-Chart

out_bit = 0 read_1_zero

0 0 0

read_1_one

out_bit = 0

read_2_zero

read_2_one

out_bit = 1

out_bit = 1

; et at s _t e s er = et at s _t x e n ; e n o _ 1 _ d a er = et at s _t x e n ) 1 = = ti b _ ni ( ; or e z _ 2 _ d a er = et at s _t x e n ) 0 = = ti b _ ni ( : ; et at s _t e s er = et at s _t x e n ; e n o _ 1 _ d a er = et at s _t x e n ) 1 = = ti b _ ni ( ; or e z _ 2 _ d a er = et at s _t x e n ) 0 = = ti b _ ni ( : ; et at s _t e s er = et at s _t x e n ; e n o _ 1 _ d a er = et at s _t x e n ) 1 = = ti b _ ni ( ; or e z _ 1 _ d a er = et at s _t x e n

)ti b _ ni

Sequence Detector FSM (cont.)

Sequence Detector FSM (cont.)

27/03/2012

4

; 0 : 1 ? ) ) e n o _ 2 _ d a e r = = g e r _ et at s ( || ) o r e z _ 2 _ d a e r = = g e r _ et at s ( ( = ti b _t u o

e udomdne e udomdne elllludomdne e udomdne ng ssa ngiissa

esacdne esacdne esacdne esacdne :::tttllluafffed ua ed ua ed es e es e eslllle es e

es es ffffiiii esllll es

ffffiiii eno_2_daer es e es e eslllle es e es e es e ffffiiii eslllle es e ffffiiii eno_1_daer

; et at s _t e s er = et at s _t x e n ; et at s _t e s er = et at s _t x e n ; e n o _ 2 _ d a er = et at s _t x e n ) 1 = = ti b _ ni ( e ; or e z _ 1 _ d a er = et at s _t x e n ) 0 = = ti b _ ni ( : ; et at s _t e s er = et at s _t x e n ; e n o _ 2 _ d a er = et at s _t x e n ) 1 = = ti b _ ni ( ; or e z _ 1 _ d a er = et at s _t x e n ) 0 = = ti b _ ni ( :

es e es e esllle

fi e sl e

ciiiigollll ettttatttts--ttttxen //////// c go e a s xen c go e a s-- xen c go e a s xen

; et at s _t x e n = < g er _ et at s ; et at s _t e s er = < g er _ et at s

fi orrez_2_daerr o ez_2_dae orrez_2_daerr o ez_2_dae e sl e fi e sl e fi orrez_1_daerr o ez_1_dae orrez_1_daerr o ez_1_dae e sl e fi e sl e

es e es e eslllle es e

)t e s er

) 1 = = t e s e r ( fi egdesop rro egdesop o egdesop @ syaw a egdesop @ syaw a egdesop rro kcolc egdesop( @ syawlllla egdesop o egdesop @ syaw a retsiger etats // ; 0 0 1 b' 3 ; 1 1 0 b' 3 ; 0 1 0 b' 3 ; 1 0 0 b' 3 ; 0 0 0 b' 3 = e n o _ 2 _ d a er = or e z _ 2 _ d a er = e n o _ 1 _ d a er = or e z _ 1 _ d a er = et at s _t e s er

rre emarrap e ema ap rrettttemarrap e ema ap re emarap e ema ap rretttemarrap retemarap rre emarrap e ema ap rrettttemarrap e ema ap rre emarrap e ema ap rrettttemarrap e ema ap noitaralced etatS // gerr ge gerr ge up uo up uo ttttupttttuo up uo upn upn ttttupniiii upn eludom

; et at s _t x e n , g er _ et at s ] 0: 2[ ;ti b _t u o ;ti b _ ni ,t e s e r , k c ol c ; )ti b _t u o ,ti b _ ni ,t e s e r , k c ol c ( t c et e d _ q e s

) 0 = = ti b _ ni ( fi etttattts_ttteserr e a s _ e s er :etats_teser e a s_ ese ) g er _ et at s( e s a c rro o @ syaw a @ syaw a rro ger_etats( @ syawlllla o @ syaw a

27/03/2012

First-in First-out Memory (FIFO)

A FIFO consists of block of memory and a controller that manages the traffic of data to and from the FIFO A FIFO provides access to only one register cell at a time (not the entire array of registers) A FIFO has two address pointers, one for writing to the next available cell, and another one for reading the next unread cell The pointers for reading and writing are relocated dynamically as commands to read or write are received A pointer is moved after each operation A FIFO can receive data until it is full and can be read until it is empty

FIFO Features (cont.)

A FIFO has:

Separate address pointers and datapaths for reading and writing data Status lines indicating the condition of the stack (full, almost full, empty etc.)

The input (write) and output (read) domains can be synchronized by two separate clocks, allowing the FIFO to act as a buffer between two clock domains (Dual Clock FIFOs) A FIFO can allow simultaneous reading and writing of data (however

synchronization is necessary if read/write parts are different clock domains)

The write signal is synchronized to the read clock using clock synchronizers FIFOs are usually implemented with dual-port RAMs with independent read- and write-address pointers and registered data ports (see www.idt.com)

27/03/2012

FIFO Structure

stack_height -1

data_in write_to_stack clk_write

stack_full stack_half stack_empty data_out read_from_stack

FIFO Buffer

rst

clk_read

Internal Signals

write_ptr

0 stack_width -1 0

Input-output Ports

read_ptr

Example: Synchronous FIFO with handshake PUSH Side POP Side

DATA_in VALID_in STALL_out

DATA_out

FIFO

{DEPTH, WIDTH}

clk rst

VALID_out stall_in

27/03/2012

FIFO SPECIFICATION Parametric WIDTH PARAMETRIC DEPT ( >= 2) Simple handshake based on stall-go flow control protocol

To push data in the fifo, the valid is must be 1 and stall_out must be 0 To pop data from the fifo, stall_in must be 0, and valid_out ust be 1. When the fifo is FULL the stall_out must be 1; When the fifo is empty, valid_out out must be 0.

The latency of the FIFO must be 1 clock cycle The FIFO must allow simultaneous reading and writing of data Use a FF based asynchronous read-synchronous write dual port RAM

Example: FIFO

VALID FULL - S TALL clk rs t FS M

VALID S TALL - ( ! REQUES T)

P US H P ointer EN 0 1 DATA 2 3 4

P OP P ointe r

DATA

n-1

27/03/2012

Validation: Functional Test

testbench. v Stimuli

Simple_Adder.v DATA VALID STALL DATA VALID STALL

FIFO

reset

clock

Potrebbero piacerti anche

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- Finite State Machine (FSM) : ExampleDocumento22 pagineFinite State Machine (FSM) : ExampleDanish WilsonNessuna valutazione finora

- Build Mamdani Systems (Code) - MATLAB & Simulink - MathWorks IndiaDocumento10 pagineBuild Mamdani Systems (Code) - MATLAB & Simulink - MathWorks IndiaArsheel KhanNessuna valutazione finora

- Log File: "Design Constraints" ChapterDocumento15 pagineLog File: "Design Constraints" Chapterbhaskar5705Nessuna valutazione finora

- A Is As: Local Deadlock and DeterminesDocumento8 pagineA Is As: Local Deadlock and Determinessd1802Nessuna valutazione finora

- Iris IssueDocumento5 pagineIris IssuenipetNessuna valutazione finora

- 248 Lab 11Documento10 pagine248 Lab 11Tyron BiggumsNessuna valutazione finora

- Assignment 3 LRDocumento3 pagineAssignment 3 LRapi-253978194Nessuna valutazione finora

- Attack Log 20220912143318Documento58 pagineAttack Log 20220912143318Cesar Augusto Jaramillo PossoNessuna valutazione finora

- System Programming and Operating Systems Lab: Assignment A2Documento8 pagineSystem Programming and Operating Systems Lab: Assignment A2Mayur DalalNessuna valutazione finora

- SVM Admin2Documento86 pagineSVM Admin2rajlvuNessuna valutazione finora

- Device Drivers, Part 13Documento10 pagineDevice Drivers, Part 13ksenthil77Nessuna valutazione finora

- FSM CoverageDocumento19 pagineFSM CoveragePMNessuna valutazione finora

- Servo - Cookbook - MbedDocumento6 pagineServo - Cookbook - MbedCảnh ManuNessuna valutazione finora

- A Simple Clock Using DS1307 + PIC16F877A - PIC Microcontroller NoteDocumento14 pagineA Simple Clock Using DS1307 + PIC16F877A - PIC Microcontroller Notelkemmerich100% (2)

- Mid Exam PDFDocumento4 pagineMid Exam PDFArife AbdulkerimNessuna valutazione finora

- Analysis of Super Password 1.0Documento16 pagineAnalysis of Super Password 1.0beefmantraNessuna valutazione finora

- Anup Das Gupta's Blog - Full Calendar With JSON Data Source Using ASPDocumento5 pagineAnup Das Gupta's Blog - Full Calendar With JSON Data Source Using ASPrithuik1598Nessuna valutazione finora

- Verilog For Finite State MachinesDocumento8 pagineVerilog For Finite State MachinesEr Pradip PatelNessuna valutazione finora

- Triggers - SQL Server - CodeProjectDocumento5 pagineTriggers - SQL Server - CodeProjectmasterpiecemanishNessuna valutazione finora

- Universal Asynchronous Receiver UAR - DoulosDocumento4 pagineUniversal Asynchronous Receiver UAR - DoulosMiguel BrunoNessuna valutazione finora

- 1) Convert The C Function Below To Ia-32 Assembly Language.: Compe 271 Mid-Term Exam #2 Fa16Documento4 pagine1) Convert The C Function Below To Ia-32 Assembly Language.: Compe 271 Mid-Term Exam #2 Fa16Giorgi TsibadzeNessuna valutazione finora

- Dba Important Linux CommandsDocumento97 pagineDba Important Linux Commandspankajsharma2302Nessuna valutazione finora

- USB - ModeSwitch - View Topic - Alcatel-Lucent T930SDocumento18 pagineUSB - ModeSwitch - View Topic - Alcatel-Lucent T930SMounir2105Nessuna valutazione finora

- Important Valeo QsDocumento7 pagineImportant Valeo QsMarwan Ahmed100% (1)

- Need Explanation of Unpredicted Output Even If Methods Are Synchronized (Threads Forum at JavaRanch)Documento5 pagineNeed Explanation of Unpredicted Output Even If Methods Are Synchronized (Threads Forum at JavaRanch)pavani21Nessuna valutazione finora

- (B) Class Monitor vs. Object Monitor (/B) : Big Moose SaloonDocumento6 pagine(B) Class Monitor vs. Object Monitor (/B) : Big Moose Saloonpavani21Nessuna valutazione finora

- MAE653 Sp10 Lesson06Documento9 pagineMAE653 Sp10 Lesson06Edwin MachacaNessuna valutazione finora

- Nguyen Ngoc ChienDocumento6 pagineNguyen Ngoc Chienchiennn.22gitNessuna valutazione finora

- Paper 6Documento9 paginePaper 6RakeshconclaveNessuna valutazione finora

- Device Drivers Part 8Documento5 pagineDevice Drivers Part 8ksenthil77Nessuna valutazione finora

- Device Drivers Part 16Documento4 pagineDevice Drivers Part 16ksenthil77Nessuna valutazione finora

- 新建 DOCX 文档Documento38 pagine新建 DOCX 文档刘嘉琦Nessuna valutazione finora

- Earthquake Response Spectrum Analysis of 4 Story Shear BuildingDocumento13 pagineEarthquake Response Spectrum Analysis of 4 Story Shear BuildingMani KumarNessuna valutazione finora

- 20 Linux System Monitoring Tools Every SysAdmin Should KnowDocumento69 pagine20 Linux System Monitoring Tools Every SysAdmin Should Knowrajan21india5986Nessuna valutazione finora

- HDL-Based Design Methodology of 16-Bit RISC Microprocessor PDFDocumento6 pagineHDL-Based Design Methodology of 16-Bit RISC Microprocessor PDFChen CYNessuna valutazione finora

- LogDocumento22 pagineLogagimNessuna valutazione finora

- IOI Training Week 7 Advanced Data Structures: 1.1 Square-Root (SQRT) DecompositionDocumento6 pagineIOI Training Week 7 Advanced Data Structures: 1.1 Square-Root (SQRT) DecompositionHimanshu RanjanNessuna valutazione finora

- Week7.pdf Sqrt+Segtree PDFDocumento6 pagineWeek7.pdf Sqrt+Segtree PDFMaruf KhanNessuna valutazione finora

- Servomechanism Controller - MATLAB & Simulink - MathWorks IndiaDocumento18 pagineServomechanism Controller - MATLAB & Simulink - MathWorks IndiaShin IgneelNessuna valutazione finora

- Appendix D - Mode S Signal Formats: 1. Operating GoalsDocumento22 pagineAppendix D - Mode S Signal Formats: 1. Operating GoalsLuca BianchiNessuna valutazione finora

- Manual TsoDocumento33 pagineManual TsoCarlos Alberto AbisculaNessuna valutazione finora

- Protection 80386 RNMDocumento1 paginaProtection 80386 RNMRajNessuna valutazione finora

- FFT Using VHDLDocumento22 pagineFFT Using VHDLMad Hatter MercuryNessuna valutazione finora

- Finite Volume MethodDocumento21 pagineFinite Volume MethodmekwonuNessuna valutazione finora

- Notes - Introduction To JavaDocumento16 pagineNotes - Introduction To JavaSiddharthShuklaNessuna valutazione finora

- Freertos ProjDocumento42 pagineFreertos ProjVittorioNessuna valutazione finora

- IBatis MyBatis Working With Stored Procedures - Loiane GronerDocumento12 pagineIBatis MyBatis Working With Stored Procedures - Loiane GronerWaldo Gómez AlvarezNessuna valutazione finora

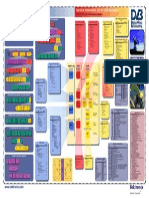

- DVB PosterDocumento1 paginaDVB PosterVinay KrNessuna valutazione finora

- Device Drivers Part 9Documento8 pagineDevice Drivers Part 9ksenthil77Nessuna valutazione finora

- Os MidTerm SolutionDocumento8 pagineOs MidTerm SolutionZiyad AhmedNessuna valutazione finora

- SQL (DML) Help - How To Delete Duplicate Rows With Primary KeyDocumento5 pagineSQL (DML) Help - How To Delete Duplicate Rows With Primary KeynagaNessuna valutazione finora

- SET-4 1) Case Histories of Network and Management ?: Scheme of Valuation Subject Name: Neteorkmanagment System (Documento17 pagineSET-4 1) Case Histories of Network and Management ?: Scheme of Valuation Subject Name: Neteorkmanagment System (Siri AjayNessuna valutazione finora

- Oslab Inhouse ManualDocumento37 pagineOslab Inhouse ManualTanisha MaheshwariNessuna valutazione finora

- Valeo QsDocumento7 pagineValeo QsNoha MustafaNessuna valutazione finora

- Rising Edge Detector, Debounce CKT, Testing CKT For ThatDocumento10 pagineRising Edge Detector, Debounce CKT, Testing CKT For ThataminhardNessuna valutazione finora

- PPTP Server Running On Your FirewallDocumento11 paginePPTP Server Running On Your FirewallHernanCossuNessuna valutazione finora

- Combinational and Sequential Circuits DesignDocumento25 pagineCombinational and Sequential Circuits DesignJadesh ChandaNessuna valutazione finora

- 04 CS StorageDocumento29 pagine04 CS StorageAnneNessuna valutazione finora

- Kd-lx30r Lx10r (SM)Documento72 pagineKd-lx30r Lx10r (SM)Roberd MihailovNessuna valutazione finora

- Soundtouch 30 Series I & Ii: ™ Wi-Fi Music SystemDocumento41 pagineSoundtouch 30 Series I & Ii: ™ Wi-Fi Music Systemjose luisNessuna valutazione finora

- Testign DigitalRF Receivers AN1314Documento38 pagineTestign DigitalRF Receivers AN1314ramoskurt28Nessuna valutazione finora

- Non-Invasive Glucose Estimation Using IR SpectrosDocumento4 pagineNon-Invasive Glucose Estimation Using IR SpectrosJASH MATHEWNessuna valutazione finora

- Capacitor-Based Backup Power Supply For PLC ModulesDocumento27 pagineCapacitor-Based Backup Power Supply For PLC ModulesMikel IglesiasNessuna valutazione finora

- LT3751 Demo Circuit 1322 Quick Start Guide LT3751 Capacitor Charger Controller With RegulationDocumento4 pagineLT3751 Demo Circuit 1322 Quick Start Guide LT3751 Capacitor Charger Controller With RegulationTiago FrisonNessuna valutazione finora

- Outdoor Ambient Temperature Sensor Open PDFDocumento16 pagineOutdoor Ambient Temperature Sensor Open PDFGustavo E. EspinosaNessuna valutazione finora

- DX DiagDocumento36 pagineDX Diagm ikhsanNessuna valutazione finora

- Panasonic Lumix Dmc-Fx01 Series Service Manual Repair GuideDocumento56 paginePanasonic Lumix Dmc-Fx01 Series Service Manual Repair GuideM8R-dcvrv01Nessuna valutazione finora

- MECH3660 5660 Quiz 1 Automation Solution 2014Documento5 pagineMECH3660 5660 Quiz 1 Automation Solution 2014Margaret AustenNessuna valutazione finora

- Module 4Documento91 pagineModule 4mahendra naikNessuna valutazione finora

- Electronic Communications PDFDocumento366 pagineElectronic Communications PDFcongquy nguyen100% (1)

- Mini Project Report 2 PDFDocumento8 pagineMini Project Report 2 PDFRahul KumarNessuna valutazione finora

- Voyager DVD ManualDocumento80 pagineVoyager DVD ManualGianniNessuna valutazione finora

- سلايدات م. سامر عبدالله صادق- تصميم المنطق الرقميDocumento287 pagineسلايدات م. سامر عبدالله صادق- تصميم المنطق الرقميAzzam SalehNessuna valutazione finora

- FRAX User's Manual: © 2009 Megger AB Released in 2008-12-10Documento10 pagineFRAX User's Manual: © 2009 Megger AB Released in 2008-12-10ryan940100% (1)

- CD294 DatasheetDocumento4 pagineCD294 DatasheetRobinson BangueroNessuna valutazione finora

- PDP-11/70 Processor Handbook (1977-1978)Documento284 paginePDP-11/70 Processor Handbook (1977-1978)TheAnonymousLugia100% (1)

- 6ES75501AA010AB0 Datasheet enDocumento4 pagine6ES75501AA010AB0 Datasheet enkphcmNessuna valutazione finora

- NCDC 2015Documento5 pagineNCDC 2015A Mohan BabuNessuna valutazione finora

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDocumento6 pagineCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavNessuna valutazione finora

- Product Data: 8 Channel MultiplexerDocumento4 pagineProduct Data: 8 Channel Multiplexerjhon vargasNessuna valutazione finora

- Waspmote Technical GuideDocumento133 pagineWaspmote Technical GuideThế DũngNessuna valutazione finora

- GST PS Alarm SystemDocumento2 pagineGST PS Alarm Systemculeros10% (1)

- f9222l 102 PDFDocumento10 paginef9222l 102 PDFfloriantudorNessuna valutazione finora

- Short Questions: (CHAPTER 18) ElectronicsDocumento9 pagineShort Questions: (CHAPTER 18) ElectronicsEhtesham Ali KhanNessuna valutazione finora

- EtherWAN EX95160-00B User ManualDocumento22 pagineEtherWAN EX95160-00B User ManualJMAC SupplyNessuna valutazione finora

- Price List of Computer ComponentsDocumento28 paginePrice List of Computer ComponentsRaja Mohammed ANessuna valutazione finora