Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Chapter 3 Solutions: For More Practice

Caricato da

Omar HayatDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Chapter 3 Solutions: For More Practice

Caricato da

Omar HayatCopyright:

Formati disponibili

Chapter 3 Solutions: For More Practice

Chapter 3 Solutions: For More Practice

3.8 You should be quite suspicious of both claims. A simple examination yields

6=2+4 12 = 4 + 8 18 = 2 + 16 24 = 8 + 16 30 = 2 + 4 + 8 + 16 (so we know Harry is wrong) 36 = 4 + 32 42 = 2 + 8 + 32 (so we know David is wrong).

3.11

subu sltu add sub $t3, $t2, $t2, $t2, $t5, $t5, $t6, $t4, $t7 $t7 $t2 $t2

unsigned

subu sltu addu subu $t3, $t2, $t2, $t2, $t5, $t5, $t6, $t4, $t7 $t7 $t2 $t2

3.14

<<This solution destroys the value of $s0>>

addu $s1, $s0, $zero sll $s0, $s0, 3 addu $s1, $s1, $s0

<<This solution preserves $s0>>

addu $s1, $s0, $zero sll $t0, $s0, 3 addu $s1, $s1, $t0

3.15 No solution provided. 3.16 No solution provided. 3.17 No solution provided.

Chapter 3 Solutions: For More Practice

3.18 C1 = c4, C2 = c8, C3 = c12, and C4 = c16.

c4 = G3,0 + (P3,0 c0). c8 is given in the exercise. c12 = G11,8 + (P11,8 G7,4) + (P11,8 P7,4 G3,0) + (P11,8 P7,4 P3,0 c0). c16 = G15,12 + (P15,12 G11,8) + (P15,12 P11,8 G7,4) + (P15,12 P11,8 P7,4 G3,0) + (P15,12 P11,8 P7,4 P3,0 c0).

3.19 The equations for c4, c8, and c12 are the same as those given in the solution

to Exercise 3.18. Using 16-bit adders means using another level of carry lookahead logic to construct the 64-bit adder. The second level generate, G0, and propagate, P0, are G0 = G15,0 = G15,12 + P15,12 G11,8 + P15,12 P11,8 G7,4 + P15,12 P11,8 P7,4 G3,0 and P0 = P15,0 = P15,12 P11,8 P7,4 P3,0 Using G0 and P0, we can write c16 more compactly as c16 = G15,0 + P15,0 c0 and c32 = G31,16 + P31,16 c16 c48 = G47,32 + P47, 32 c32 c64 = G63,48 + P63,48 c48

Chapter 3 Solutions: For More Practice

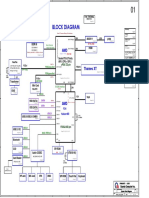

A 64-bit adder diagram in the style of the following gure would look like this:

CarryIn a0, 15 ALU0 b0, 15 P15, 0 G15, 0 Second-level carry-lookahead unit c16 CarryIn a16, 31 ALU1 b16, 31 c32 CarryIn a32, 47 ALU2 b32, 47 c48 CarryIn a48, 63 ALU3 b48, 63 P63, 48 G63, 48 Result4863 P47, 32 G47, 32 Result3247 P31, 16 G31, 16 Result1631 Result015

c64 CarryOut

3.20 No solution provided. 3.21 No solution provided. 3.22 No solution provided. 3.24 No solution provided.

Chapter 3 Solutions: For More Practice

3.32

#include <stdio.h> void main(void) { double d; scanf("%lf",&d); printf("%llx\n",d); }

3.33

import java.io.*; public class FloatingConvert { public static void main(String[] args) throws IOException { BufferedReader in = new BufferedReader(new InputStreamReader(System.in)); String line = in.readLine(); if(line != null) { double d = Double.parseDouble(line); System.out.println(Long.toHexString(Double.doubleToLongBits(d))); } } }

3.34

# multiply by four by adding 2 to the exponent; # ignores exp. overflow and special exp. values lw beq lui add sw Exit: $t0, $t0, $t1, $t0, $t0, X($zero) $zero, Exit 0x01000000 $t0, $t1 X(zero) # # # # # $t0 = single prec. fp value mp change if zero constant 2 in exp. field add to exponent replace

Chapter 3 Solutions: For More Practice

3.47 No solution provided. 3.48 The guard bit is present to preserve the full precision (number of significant

bits) of the significand during the operation. It can be shown that a single bit is sufficient for +, , , and / to preserve the precision of a result that can be expressed in the number of bits available in the significand. If the result has more bits of precision than available in the floating-point format, then rounding is used to yield an expressible approximation (fits in the available number of bits) of the result. The bits guard (g), round (r), and sticky (s) all participate in right shifts of the signicand to make the exponent of the smaller number match that of the larger number. Right shifting moves the LSB into g, g into r, and the OR of bit(s) shifted through r into s. During left shifts, s does not participate, zeros are shifted into r as needed, r shifts into g, and g shifts into the LSB. The following tables list the actions needed for each rounding mode. Round Toward Negative Innity:

g

0 X

r

0 X

s

0 1

Action

Exact result; significand correctly rounded Inexact result, correctly rounded if Sum is positive, round by adding 1 to LSB if Sum is negative (makes Sum more negative, moving toward negative infinity) Inexact result, correctly rounded if Sum is positive, round by adding 1 to LSB if Sum is negative (makes Sum more negative, moving toward negative infinity) Inexact result, correctly rounded if Sum is positive, round by adding 1 to LSB if Sum is negative (makes Sum more negative, moving toward negative infinity)

Round Toward Positive Innity:

g

0 X

r

0 X

s

0 1

Action

Exact result; significand correctly rounded Inexact result, correctly rounded if Sum is negative, round by adding 1 to LSB if Sum is positive (makes Sum more positive, moving toward positive infinity) Inexact result, correctly rounded if Sum is negative, round by adding 1 to LSB if Sum is positive (makes Sum more positive, moving toward positive infinity) Inexact result, correctly rounded if Sum is negative, round by adding 1 to LSB if Sum is positive (makes Sum more positive, moving toward positive infinity)

Chapter 3 Solutions: For More Practice

Truncate:

g

X

r

X

s

X

Action

Significand correctly rounded

(Unbiased) Round to Nearest:

Sump

X X X 0 1 X X

g

0 0 0 1 1 1 1

r

0 X 1 0 0 1 X

s

0 1 0 0 0 X 1

Action

Exact result; significand correctly rounded Inexact result, but significand is correctly rounded Inexact result, but significant is correctly rounded Tie case with even significand; significand correct Tie case with odd significand; round to nearest even by adding 1 to LSB Inexact result, round to nearest by adding 1 to LSB Inexact result, round to nearest by adding 1 to LSB

Note that unbiased round to nearest is the only mode that requires the value of the LSB. Neither unbiased round to nearest nor truncate predicate their action on the sign of the signicand. Round to plus and minus innity are the only modes that require the sign bit. Filling in the table given in the exercise:

Rounding mode

Toward Negative Infinity Toward Positive Infinity Truncate

Sum > = 0

blank OR(g,r,s) blank

Sum < 0

OR(g,r,s) blank blank g (Sump + r + s)

(Unbiased) Round to Nearest g (Sump + r + s)

3.49 No solution provided.

Chapter 3 Solutions: For More Practice

3.50

1 2 3 4 4 6 7 8 8 8

3.51

lw addiu sw addu or beq bne subu andi nor

24% 12% 9% 7% 7% 6% 5% 3% 3% 3% 21% 15% 15% 8% 8% 7% 5% 3% 2% 2% 2% 2% 2%

1 2 2 4 4 6 7 8 9 9 9 9 9

3.52

addu lw l.d add.d mul.d s.d lui sub.d addiu subu or sw beq

a. lw, addiu, sw, addu, or, beq, subu b. 68% c. 79% d. 46% e. 92%

Chapter 3 Solutions: For More Practice

3.53 lw, addiu, addu, l.d, sw

lw, addiu, addu, sw are tops with combined %. l.d is very important to FP benchmarks.

3.54 1.0 cycle ops (not in Figure 3.11.1) and their percentages:

addu addiu subu and andi or ori nor sll lui slt slti sltu sltiu sra misc

7 12 3 1 3 7 2 3 1 2 2 1 1 1 1 2

49% 1.3 cycle ops (loads and stores) and their percentages:

lw sw lbu sb lhu

24 9 1 1 1

36%

Chapter 3 Solutions: For More Practice

1.6 cycle ops (conditional branches) and their percentages:

beq bne bltz bgez

6 5 1 1

13% 1.2 cycle ops (jumps) and their percentages:

jal jr

1 1

2% Avg: .49 + 1.3 * .36 + 1.6 * .13 + 1.2 * .02 = 1.19 CPI

3.55 1 cycle ops (not in Figure 3.11.1) and their percentages:

addu addiu subu or

nor

sll lui misc

21 2 2 2 1 1 5 3

37% 1.3 cycle ops (loads and stores) and their percentages:

lw sw l.s s.s

15 2 15 7

39%

10

Chapter 3 Solutions: For More Practice

1.6 cycle ops (conditional branches) and their percentages:

beq bne blez

2 1 1

4% 1.0 cycle ops (FP add) and their percentages:

add.d sub.d

8 3

11% 3.0 FP mul 8% 5.0 Int mult 1% Avg: .37 + 1.3 * .39 + 1.6 * .04 +.11 + 3.0 * .08 + 5.0 * .01 = 1.341 CPI

Potrebbero piacerti anche

- A-level Maths Revision: Cheeky Revision ShortcutsDa EverandA-level Maths Revision: Cheeky Revision ShortcutsValutazione: 3.5 su 5 stelle3.5/5 (8)

- Bol ModelDocumento15 pagineBol ModelSuresh BabuNessuna valutazione finora

- ST MicroInverter SchemeticDocumento12 pagineST MicroInverter Schemeticpuspendu janaNessuna valutazione finora

- Let's Practise: Maths Workbook Coursebook 7Da EverandLet's Practise: Maths Workbook Coursebook 7Nessuna valutazione finora

- KalmanDocumento34 pagineKalmanbilal309Nessuna valutazione finora

- JavaScript JSON Cookbook - Sample ChapterDocumento24 pagineJavaScript JSON Cookbook - Sample ChapterPackt Publishing100% (3)

- GCSE Maths Revision: Cheeky Revision ShortcutsDa EverandGCSE Maths Revision: Cheeky Revision ShortcutsValutazione: 3.5 su 5 stelle3.5/5 (2)

- Lec 6: Gain, Phase Margin, Designing With Bode Plots, CompensatorsDocumento10 pagineLec 6: Gain, Phase Margin, Designing With Bode Plots, CompensatorszakiannuarNessuna valutazione finora

- Assignment R New 1Documento26 pagineAssignment R New 1Sohel RanaNessuna valutazione finora

- Mathematics Of: Cryptography-IDocumento59 pagineMathematics Of: Cryptography-Iritesh sinhaNessuna valutazione finora

- Sequences and Series: Example 4.1Documento16 pagineSequences and Series: Example 4.1sargent9914Nessuna valutazione finora

- CH 2 (CNS)Documento73 pagineCH 2 (CNS)Subhasish DhalNessuna valutazione finora

- Round-Off Error: IEEE 754 Double Precision Floating Point Data TypeDocumento5 pagineRound-Off Error: IEEE 754 Double Precision Floating Point Data TypeKESHAV TYAGINessuna valutazione finora

- Appendix Nonlinear RegressionDocumento5 pagineAppendix Nonlinear RegressionSanjay KumarNessuna valutazione finora

- Information SecurityDocumento45 pagineInformation SecurityAryan Akshay VerduNessuna valutazione finora

- Heizer10e Tut3Documento10 pagineHeizer10e Tut3Ralf SanderNessuna valutazione finora

- Comb CircDocumento63 pagineComb Circm.sangeethjaNessuna valutazione finora

- Stopping Criterion: RemarkDocumento11 pagineStopping Criterion: RemarkDl Al-azizNessuna valutazione finora

- OnlineTut03 PDFDocumento10 pagineOnlineTut03 PDFMohd Nazri SalimNessuna valutazione finora

- Modern Regression - Ridge RegressionDocumento21 pagineModern Regression - Ridge RegressionStanley Lan100% (1)

- Midterm 2016 CorrDocumento4 pagineMidterm 2016 Corrantoine demeireNessuna valutazione finora

- Crypto Maths - Part 1Documento21 pagineCrypto Maths - Part 1abhishek reddyNessuna valutazione finora

- Simplex MethodDocumento45 pagineSimplex MethodBilal AhmedNessuna valutazione finora

- Math NotesDocumento16 pagineMath Notescody.chen.154Nessuna valutazione finora

- SBR Tutorial 4 - Solution - UpdatedDocumento4 pagineSBR Tutorial 4 - Solution - UpdatedZoloft Zithromax ProzacNessuna valutazione finora

- IB Mathematics AI SL Notes For Number and AlgebraDocumento14 pagineIB Mathematics AI SL Notes For Number and Algebrated exNessuna valutazione finora

- Curve Fitting TechniquesDocumento14 pagineCurve Fitting TechniquesAveenNessuna valutazione finora

- Programming and Data StructuresDocumento22 pagineProgramming and Data StructuresHenintsoa RamorasataNessuna valutazione finora

- Operations On Floating Point NumbersDocumento16 pagineOperations On Floating Point NumbersAyush BajpaiNessuna valutazione finora

- MCSE-004 Solved Assignment 2012-13Documento13 pagineMCSE-004 Solved Assignment 2012-13Shailesh SoniNessuna valutazione finora

- Computer Science 37 Lecture 9Documento17 pagineComputer Science 37 Lecture 9Alexander TaylorNessuna valutazione finora

- LST Module 4 PDFDocumento16 pagineLST Module 4 PDFFinella Marie Yap CawalingNessuna valutazione finora

- Answer Key: Problem Set 4: Colgpa Hsgpa Act SkippedDocumento7 pagineAnswer Key: Problem Set 4: Colgpa Hsgpa Act SkippedJaime Andres Chica PNessuna valutazione finora

- Multifactorial Multiplication (Solving Problems That Contain Two or More Multipliers)Documento4 pagineMultifactorial Multiplication (Solving Problems That Contain Two or More Multipliers)iezalhaweNessuna valutazione finora

- Manonmaniam Sundaranar University: B.Sc. Mathematics - Iii YearDocumento76 pagineManonmaniam Sundaranar University: B.Sc. Mathematics - Iii YearNikk TirthNessuna valutazione finora

- CH 04Documento38 pagineCH 04Musarat NazirNessuna valutazione finora

- Lecture4 PDFDocumento33 pagineLecture4 PDFavi0341Nessuna valutazione finora

- Introduction To Numerical MethodesDocumento11 pagineIntroduction To Numerical MethodesMiljan TrivicNessuna valutazione finora

- Binary IntegerDocumento23 pagineBinary IntegerAung Zaw MoeNessuna valutazione finora

- L-4. Intger ArithmeticDocumento34 pagineL-4. Intger ArithmeticArghadeep GhoshNessuna valutazione finora

- 9 Chapter 4 Simplex MethodDocumento19 pagine9 Chapter 4 Simplex Methodtanmoy biswasNessuna valutazione finora

- Numerical Methods ECE Dept.: Uphsd - CalambaDocumento41 pagineNumerical Methods ECE Dept.: Uphsd - CalambaShantal MarieNessuna valutazione finora

- Logistic RegressionDocumento49 pagineLogistic Regressiontamim habybyNessuna valutazione finora

- Logistic RegressionDocumento49 pagineLogistic RegressionAkash M KNessuna valutazione finora

- Quicker Basic Calculation (WWW - Freeupscmaterials.wordpress - Com)Documento42 pagineQuicker Basic Calculation (WWW - Freeupscmaterials.wordpress - Com)k.palrajNessuna valutazione finora

- Number Theoretic AlgorithmsDocumento134 pagineNumber Theoretic AlgorithmsNetaji SagaramNessuna valutazione finora

- 4 Numbers and MatricesDocumento26 pagine4 Numbers and MatricesSara Quintana HornaNessuna valutazione finora

- Discussion 12 Fall 2019 SolutionsDocumento8 pagineDiscussion 12 Fall 2019 SolutionssamNessuna valutazione finora

- Module-1: Divisibility and The Divisibility AlgorithmDocumento21 pagineModule-1: Divisibility and The Divisibility Algorithmdigital loveNessuna valutazione finora

- LP ASolnDocumento5 pagineLP ASolnspectrum_480% (1)

- HW7 QuestionsDocumento3 pagineHW7 QuestionsOzan TokatlıNessuna valutazione finora

- AlgoDocumento28 pagineAlgomarylee_mlNessuna valutazione finora

- AlgorithmsDocumento28 pagineAlgorithmsmuhammad aliNessuna valutazione finora

- Object Oriented Programming in Java Binary and Hexadecimal Numeration and Logical OperationsDocumento12 pagineObject Oriented Programming in Java Binary and Hexadecimal Numeration and Logical Operationsaqil_shamsiNessuna valutazione finora

- PERTDocumento75 paginePERTJISHA PDNessuna valutazione finora

- Chapter 2 (Big M & Sensitivity)Documento25 pagineChapter 2 (Big M & Sensitivity)Yohannes BelaynehNessuna valutazione finora

- BOOTHDocumento3 pagineBOOTHBharath VijaiNessuna valutazione finora

- 3-Module - 1 Fundamentals of Number Theory-04-01-2024Documento35 pagine3-Module - 1 Fundamentals of Number Theory-04-01-2024utkarsh.tyagi2021Nessuna valutazione finora

- PDFDocumento4 paginePDFOmar HayatNessuna valutazione finora

- MatlabHelpReg PDFDocumento31 pagineMatlabHelpReg PDFOmar HayatNessuna valutazione finora

- Reseach ArticleDocumento5 pagineReseach ArticleOmar HayatNessuna valutazione finora

- Chan Report 8 18Documento16 pagineChan Report 8 18Omar HayatNessuna valutazione finora

- New TicketDocumento2 pagineNew TicketOmar HayatNessuna valutazione finora

- Transformer TestingDocumento10 pagineTransformer Testingdheerajkumar02527289100% (1)

- Transformer TestingDocumento10 pagineTransformer Testingdheerajkumar02527289100% (1)

- YL-195 Motor - Electric Traction & Electrical Control Trainer - YALONG (China) - Education Appliances - Office Supplies Products - DIYTradeDocumento3 pagineYL-195 Motor - Electric Traction & Electrical Control Trainer - YALONG (China) - Education Appliances - Office Supplies Products - DIYTradeOmar HayatNessuna valutazione finora

- EM-ITL-3000: Electrical Machine TrainerDocumento4 pagineEM-ITL-3000: Electrical Machine TrainerOmar HayatNessuna valutazione finora

- Basis PDFDocumento12 pagineBasis PDFMohammed Ahmad OsamaNessuna valutazione finora

- ACR For The Year 2011: Employee's Name: Designation: Faculty: Date of Joining: Contact No: Official AddressDocumento2 pagineACR For The Year 2011: Employee's Name: Designation: Faculty: Date of Joining: Contact No: Official AddressOmar HayatNessuna valutazione finora

- CAL ProgDocumento433 pagineCAL ProgAng'ila JuniorNessuna valutazione finora

- Proposal Template 22Documento9 pagineProposal Template 22Hypo GarageNessuna valutazione finora

- Microwave Solid State DeviceDocumento18 pagineMicrowave Solid State DeviceAmit Shankar Choudhary100% (1)

- Ieee Format SrsDocumento3 pagineIeee Format SrsAyaan MuhammadNessuna valutazione finora

- Automatic Stabilization of Zigbee Network: Guanghui Pan Jia HeDocumento4 pagineAutomatic Stabilization of Zigbee Network: Guanghui Pan Jia HeEdgar A.BNessuna valutazione finora

- SO65790Documento5 pagineSO65790Julius NkrumahNessuna valutazione finora

- Quanta LZ3C Rev 2a - Lenovo Ideapad z585Documento51 pagineQuanta LZ3C Rev 2a - Lenovo Ideapad z585Raj kishorNessuna valutazione finora

- Linux Filesystem Hierarchy: The Linux Documentation ProjectDocumento29 pagineLinux Filesystem Hierarchy: The Linux Documentation ProjectthewhiteeyeNessuna valutazione finora

- Eecs 151/251A Asic Lab 2: Simulation: Prof. John Wawrzynek Tas: Quincy Huynh, Tan NguyenDocumento12 pagineEecs 151/251A Asic Lab 2: Simulation: Prof. John Wawrzynek Tas: Quincy Huynh, Tan NguyenNguyen Van ToanNessuna valutazione finora

- Seed Sowing Robot-IJRASETDocumento8 pagineSeed Sowing Robot-IJRASETIJRASETPublicationsNessuna valutazione finora

- Streamline NX v3Documento8 pagineStreamline NX v3Datthanhtv NguyenNessuna valutazione finora

- Datasheet Cisco GS7000Documento7 pagineDatasheet Cisco GS7000jorwyonNessuna valutazione finora

- PBLJ Lab Worksheet 1.3Documento9 paginePBLJ Lab Worksheet 1.3Milan ThindNessuna valutazione finora

- Parity Release Notes - V7.0.0 General AvailabilityDocumento18 pagineParity Release Notes - V7.0.0 General AvailabilityHenry100% (1)

- ICT Summative Assessment 1Documento2 pagineICT Summative Assessment 1Zapirah Nirel LayloNessuna valutazione finora

- ODA E85592Documento278 pagineODA E85592Mohamed SamiNessuna valutazione finora

- SM M115FDocumento22 pagineSM M115FYoyokNessuna valutazione finora

- Start: Soldering - Solderen - Soudage - Löten - Soldadura - Lödning - Juottami Nen - Saldatura - SoldaDocumento1 paginaStart: Soldering - Solderen - Soudage - Löten - Soldadura - Lödning - Juottami Nen - Saldatura - SoldaGABRIEL MNessuna valutazione finora

- List Widget Odoo 14Documento9 pagineList Widget Odoo 14Idris AstriNessuna valutazione finora

- LIU-0832WN User ManualDocumento8 pagineLIU-0832WN User Manualmoustache237Nessuna valutazione finora

- Use of Social MediaDocumento61 pagineUse of Social MediaBaba HeadquaterNessuna valutazione finora

- Power Converters LabDocumento53 paginePower Converters LabK Kiran VishnuNessuna valutazione finora

- PSA3 1 Operators Calibration Manual EnglishDocumento90 paginePSA3 1 Operators Calibration Manual EnglishAyoub SimouNessuna valutazione finora

- BC - Namespaces and Naming Conventions (BC-CTS-NAM) : Release 4.6CDocumento26 pagineBC - Namespaces and Naming Conventions (BC-CTS-NAM) : Release 4.6CMythili DuraisamiNessuna valutazione finora

- Mid Sem ExamDocumento2 pagineMid Sem ExamPiyush MaheshwariNessuna valutazione finora

- Foshan Blue Rocket Elec 2N2222A - C358533Documento6 pagineFoshan Blue Rocket Elec 2N2222A - C358533mrahNessuna valutazione finora