Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

DTMF RD

Caricato da

Kattineni Chaitanya0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

66 visualizzazioni8 pagineDTMF-RD 2 is a reference design kit for the c8051f300 microcontroller. It includes a DTMF Decoder and DTMF Generator. The evaluation board can accept DTMF signals from three input sources.

Descrizione originale:

Titolo originale

DTMF-RD

Copyright

© Attribution Non-Commercial (BY-NC)

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoDTMF-RD 2 is a reference design kit for the c8051f300 microcontroller. It includes a DTMF Decoder and DTMF Generator. The evaluation board can accept DTMF signals from three input sources.

Copyright:

Attribution Non-Commercial (BY-NC)

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

66 visualizzazioni8 pagineDTMF RD

Caricato da

Kattineni ChaitanyaDTMF-RD 2 is a reference design kit for the c8051f300 microcontroller. It includes a DTMF Decoder and DTMF Generator. The evaluation board can accept DTMF signals from three input sources.

Copyright:

Attribution Non-Commercial (BY-NC)

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 8

Rev. 0.

1 11/05 Copyright 2005 by Silicon Laboratories DTMF-RD

DTMF- RD

DTMF DECODER KI T USERS GUI DE

1. Kit Contents

The DTMF Decoder Reference Design Kit includes the following items:

DTMF Decoder Evaluation Board.

Universal (100240 V, 5060 Hz) AC to DC Power Adapter.

DTMF Decoder Kit Users Guide (this document).

Reference Design CD containing the following items:

DTMF Decoder Reference Design (AN218) and associated software (AN218SW.zip).

Keil Software 8051 Development Tools (evaluation assembler, 2 kB limited compiler, and linker).

All DTMF Decoder related documentation in PDF format.

2. DTMF Decoder Overview

The DTMF Decoder Evaluation Board contains both a DTMF Decoder and DTMF Generator. The evaluation board

provides a hardware platform for evaluating the software provided in the DTMF Decoder Reference Design and

prototyping telephony applications using the C8051F300 MCU. The DTMF Decoder Evaluation board is shown in

Figure 1.

The DTMF Decoder Reference Design (available on the CD) includes the following:

Background and theory of DTMF decoding using the Goertzel Algorithm.

Description of a software implementation for the C8051F300 MCU.

Full C source code for the DTMF decoder and generator. The software is available on the Reference Design

Kit CD (AN218SW.zip) and on the Silicon Laboratories website.

Figure 1. DTMF Decoder Evaluation Board

DTMF Decoder

DTMF Generator

DTMF-RD

2 Rev. 0.1

2.1. DTMF Decoder

The DTMF decoder section of the evaluation board can accept DTMF signals from three input sources as shown in

Figure 2. The Audio Jack input source allows direct connection to a PC sound card and accepts bi-polar signals

from the sound card. This allows DTMF tones to be recorded and played back from a .WAV file or generated using

DTMF generation software. The bi-polar signal is converted to a uni-polar signal and conditioned before being

routed to the MCUs ADC input. The user should adjust the gain and offset potentiometers such that the

conditioned signal at the ADC input varies between 0 to 3 V.

The second input source, labeled DTMF_Gen, selects the output of the on-board DTMF Generator as the input to

the DTMF decoder. See "DTMF Generator" on page 2 for more details about the on-board DTMF Generator. The

third input source, Terminal Block, allows a stand-alone signal generator to be used for generating DTMF signals.

This input is fed directly to the ADC input; therefore, the signal levels on this uni-polar input must be between 0 and

3 V.

The selected input signal is routed to the MCUs ADC input and to an amplified speaker and audio jack for listening

to the input DTMF tones. Once a valid DTMF tone is detected by the decoder, the corresponding symbol is

displayed on the 7-Segment LED and printed to a UART terminal.

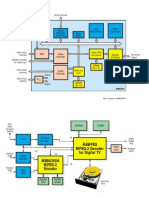

Figure 2. Demo Board (Decoder Section)

2.2. DTMF Generator

Figure 3 shows a block diagram of the DTMF Generator section of the demo board. As buttons on the keypad are

pressed, DTMF tones are generated by the C8051F300. A 100 ms tone is generated for each key press. The MCU

generates a digital signal corresponding to the DTMF code using the PCA. The digital signal is passed through a low

pass filter to remove the high-frequency components and allow only pure tones to be passed to the output.

Figure 3. Demo Board (Generator Section)

DTMF Decoder

DTMF_Gen

Terminal

Block

Audio Jack

Input

Selector

C8051F300

DTMF Decoder

Amplified

Speaker

RS-232

7-Segment

LED

Audio

Jack

DTMF Generator

1

*

2 3

4 5 6

7 8 9

c

KEYPAD

0

C8051F300

PCA Output

Low Pass

Filter

Analog

Amplifier

DTMF_Gen

DTMF-RD

Rev. 0.1 3

3. DTMF Demonstration

The DTMF Decoder Evaluation Board is factory pre-programmed with both the DTMF decoder and generator

firmware. For this demonstration, connect the output of the DTMF generator to the input of the DTMF decoder.

1. Verify that J10 (next to the red LED) is shorted. This supplies power to the decoder section of the board.

2. Verify that pins 3 and 4 (the middle pins) of J4 are shorted. The J4 header is near the RS-232 connector and

is labeled Source Selection.

3. Verify that J3 is shorted. The J3 header is located near the speaker and may be removed to disconnect the

speaker.

4. Power the DTMF Decoder Evaluation Board using the supplied 9 V ac adapter. You should hear the speaker

beep and the decimal point on the 7-segment LED should be displayed.

5. Press any key on the keypad. This generates a DTMF tone. When the DTMF tone is detected by the

decoder, it will be displayed on the 7-segment LED.

To view the decoded characters on a UART Terminal:

1. Verify that pins 1 and 2 of J6 are shorted. This enables UART transmission.

2. Connect a UART terminal to the RS-232 connector using a serial cable.

3. Configure the terminal for 9600 Baud 8-N-1.

4. The characters should be printed to the terminal as buttons on the keypad are pressed.

4. Updating Firmware

If the DTMF Decoder Evaluation Board is used to develop software for the C8051F300, the original firmware can

be restored by downloading the HEX files provided in the AN218.zip file. A USB Debug Adapter or Serial Debug

Adapter is required to download the hex files. A USB Debug Adapter is included in the C8051F300 Development

Kit. See the Silicon Laboratories website for more details.

Note: The evaluation compiler included on the Reference Design CD is limited to 2 kB object code generation. The evaluation

compiler included on the Development Kit CD is limited to 4 kB object code generation. The DTMF Decoder example

software has an object code size of 3866 bytes when compiled at optimization level 9. The Development Kit CD is

included in each Silicon Laboratories Development Kit and can also be ordered from the Silicon Laboratories website

as a separate item.

DTMF-RD

4 Rev. 0.1

5. Schematic

Figure 4. DTMF Decoder Evaluation Board (Schematic 1 of 4)

M1P05

M1CP0+

M1P07

M1P04

M1C2CLK

M1CP0+

3V3

M1ADC0

M1P04

M1nRST

TX

XTX

XRX

RX

M1CP0-

M1nRST

M1P07

M1P05

M1CP0-

M1P07

M1C2DAT

M1P05

GND

GND

VDD2

GND

VDD1

GND

VDD1

GND

VDD2

GND

GND

GND

GND

GND

VDD2

GND

VDD2

GND

GND

GND

GND

VDD1

M1ADC0

M1nRST

MCU1

Extension

DEBUG1

MCU1

DTMF

Decoder

RESET

RS232

Adapter

7-segment Display

R28 680R

R34 680R

U2

MAX3224

RDY

1

C1+

2

C1-

4

C2+

5

C2-

6

INVALID

11

GND

18

V+

3

V-

7

VCC

19

T1OUT

17

T2OUT

8

R1OUT

15

R2OUT

10

T1IN

13

T2IN

12

R1IN

16

R2IN

9

FORCEON

14

FORCEOFF

20

J1

DB9 Female Right Angle

5

9

4

8

3

7

2

6

1

R27 680R

TP23

M1P0.7

R30

470R

C7

0u1F

R33 680R

TP19

GND

R32 680R

TP16 P0.6

J6

HEADER 2X2

1 2

3 4

C31

0u1F

R29

10K

C2

0u1F

SW1

C23

4n7F

TP22

M1nRST

TP13 P0.7

TP1 XRX

Y1

32.768 KHz

1 2

3

C21

0u1F

C19

18pF

C32

1u0F

U6

7 SEGMENT DISPLAY

A

10

B

9

C

8

D

5

E

4

F

2

G

3

COM

1

DP

7

COM

6

R25 680R

C8

0u1F

TP11 P0.0

R22

10M

R31

1K

R24

1K

TP15 P0.5

TP21

M1C2D

C22

0u1F

J7

HEADER 5X2

1 2

3 4

5 6

7 8

9 10

TP17 GND

R35 680R

R43

1K

TP14 P0.1

U7

MM74HCT164

A

1

B

2

CLK

8

CLR

9

Q0

3

Q1

4

Q2

5

Q3

6

Q4

10

Q5

11

Q6

12

Q7

13

GND

7

Vcc

14

TP2 XTX

TP20

M1C2CLK

C6

0u1F

U5

C8051F300

P0.0

1

GND

11

P0.1

2

Vdd

3

P0.2

4

P0.3

5

P0.7

10

P0.6

9

RST

8

P0.5

7

P0.4

6

TP8 3V3

C1

0u1F

J8

Box 10pin

1

3

5

7

9

2

4

6

8

10

TP18 nRST

C15

18pF

C20

0u1F

TP12 P0.4

R26 680R

DTMF-RD

Rev. 0.1 5

Figure 5. DTMF Decoder Evaluation Board (Schematic 2 of 4)

DTMF_Source

Noise_Source

VDD3

GND

VDD2

GND

GND GND GND

GND

VDD2

VDD2

VDD2

GND

GND

GND

GND

VDD3

GND

GND

GND GND

VDD2

GND

GND

GND

M1ADC0

DTMF_Gen

Power_amp

SYTRON Technologies Ltd

127, Sos. Pacurari, Iasi, Romania, 6600

Phone: +40-232-244196

Fax: +40-232-244203

URL:www.sytron-tech.ro

DTMF Output

Buffer

DTMF Source

Selection

Soundcard signal

conditioning

From

soundcard

Speaker

Amplifier

R3

100R C4

2u2F

TP7

DTMF In

R17

680R

C5

0u68F

R21

10R

R6

100R

TP4

Soundcard

C18

5pF

R18

10R

C9

0u22F

R12

10K

R7

470R

C13

1uF

U3

TPA301

IN-

4

IN+

3

BYPASS

2

SHUTDOWN

1

VDD

6

VO+

5

VO-

8

GND

7

TP3

M1ADCD0

POT2

10K

1

3

2

R8

470R

R2

470R

C14

33uFT/25V

P1

AUDIO CON

2

3

1

PA1

N.C

2

3

1

TP10

Vin

+

C17

1000uF/16V

R16

1K8

TP9

VDD3

1

J4

HEADER 3X2

1 2

3 4

5 6

R20

51K

POT1

10K

1 3

2

C16

0u1F

J3

HED1x2

1

2

R11

1K2

C3

0u1F

TP6

DTMF_Out

U4

L4931CD33

IN

8

OUT

1

G

N

D

1

2

En

5

G

N

D

2

3

G

N

D

3

6

G

N

D

4

7

C11

2u2F

LS1

SPEAKER

D1

BAT54S

1

3

2

R5

100K

-

+

U1A

LMV324MT

3

2

1

4

1

1

-

+

U1B

LMV324MT

5

6

7

4

1

1

R19

10R

J2

Screw Terminal

1

2

3

4

J5

HED1x2

1

2

R13

10K

P2

AUDIO CON

2

3

1

R10

470R

R4

13K3

R1

2K

R23

10R

DTMF-RD

6 Rev. 0.1

Figure 6. DTMF Decoder Evaluation Board (Schematic 3 of 4)

Figure 7. DTMF Decoder Evaluation Board (Schematic 4 of 4)

M2C2CLK

M1nRST

M2C2DAT

ROW1

ROW3

ROW0

ROW2

COL2

COL0

COL1

GND

VDD2

GND

VDD2

GND

VDD2

VDD2

GND

GND

VDD2

GND

VDD2

GND

GND

DTMF_Gen

M1nRST

Title

P4 DTMF G t

SYTRON Technologies Ltd

127, Sos. Pacurari, Iasi, Romania, 6600

Phone: +40-232-244196

Fax: +40-232-244203

URL:www.sytron-tech.ro

E-mail: silabs.team@sytron-tech.ro

MCU2

DTMF

Generator

Keypad

2nd Order Low

Pass Filter

DEBUG2

A

E

G

D

F C B

1 2 3

4 5 6

7 9 8

*

0 C

KEYPAD KEY CONNECTl ON

CONNECTOR

R9

470R

R14

470R

J9

Box 10pin

1

3

5

7

9

2

4

6

8

10

R15

470R

D2

Green

R44

1K

C24

0u1F

R42

470R

R41

10K

J11

HEADER 4X2

E

F

N.C

G

A

B

C

D

TP27

C12

0u1F

-

+

U1D

LMV324MT

12

13

14

4

1

1

Q1

BSS138

3

1

2

U8

C8051F300

P0.0

1

GND

11

P0.1

2

Vdd

3

P0.2

4

P0.3

5

P0.7

10

P0.6

9

RST

8

P0.5

7

P0.4

6

TP29

M2P0.7

R39

200R

R38

22K

R36

10K

R40

1K

TP28

C10

0u1F

TP24

M2C2D

R37

10K

-

+

U1C

LMV324MT

10

9

8

4

1

1

TP5

DTMF_Gen

GND

VDD1

VDD2

Power_amp

Power Supply

Power

R48

470R

D4

S2M

TP32

GND

1

U9

L4931CD33

IN

8

OUT

1

G

N

D

1

2

En

5

G

N

D

2

3

G

N

D

3

6

G

N

D

4

7

C28

0u1F C30

0u1F

C29

33uFT/25V

R45

2R

R46

2R

C27

0u1F

TP25

3V3

1

J10

JUMPER1

1 2

TP26

GND

1

R47

100R

+

C33

1000uF/16V C25

0u1F

TP33

VIN

TP30

Vin

D3

Red

P3

PHONEJACK

2

3

1

C26

0u1F

TP31

3V3Reg

1

R49

100R

DTMF-RD

Rev. 0.1 7

NOTES:

DTMF-RD

8 Rev. 0.1

CONTACT INFORMATION

Silicon Laboratories Inc.

4635 Boston Lane

Austin, TX 78735

Email: MCUinfo@silabs.com

Internet: www.silabs.com

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice.

Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from

the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features

or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, rep-

resentation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation conse-

quential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to

support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where per-

sonal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized ap-

plication, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Potrebbero piacerti anche

- Digital Signal Processing Using the ARM Cortex M4Da EverandDigital Signal Processing Using the ARM Cortex M4Valutazione: 1 su 5 stelle1/5 (1)

- Mr8535 User ManualDocumento10 pagineMr8535 User Manualdinda_wandasariNessuna valutazione finora

- Home Automation: G Manihas Reddy - 08B81A1026 G.RAKESH REDDY - 08B81A1041 M.Srikanth - 08B81A1052Documento23 pagineHome Automation: G Manihas Reddy - 08B81A1026 G.RAKESH REDDY - 08B81A1041 M.Srikanth - 08B81A1052Nitin KumarNessuna valutazione finora

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Da EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Nessuna valutazione finora

- 1142 NEC DatfasheetDocumento8 pagine1142 NEC DatfasheetAjay Bhalerao100% (1)

- Exploring Arduino: Tools and Techniques for Engineering WizardryDa EverandExploring Arduino: Tools and Techniques for Engineering WizardryValutazione: 4.5 su 5 stelle4.5/5 (5)

- DVB-Manual EnV2Documento43 pagineDVB-Manual EnV2Mitic MilanNessuna valutazione finora

- Embedded SystemDocumento119 pagineEmbedded SystemVidushi DalelaNessuna valutazione finora

- TK 3107Documento28 pagineTK 3107Abe LimiNessuna valutazione finora

- TK-2107 SMDocumento30 pagineTK-2107 SMgpasztori2262Nessuna valutazione finora

- PIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsDa EverandPIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsValutazione: 5 su 5 stelle5/5 (1)

- Vestel dvd7500 Orion dvd-2705 5.1ch SMDocumento25 pagineVestel dvd7500 Orion dvd-2705 5.1ch SMgondifNessuna valutazione finora

- Service Manual: PDP TelevisionDocumento62 pagineService Manual: PDP TelevisionMiguel Hernandez GlezNessuna valutazione finora

- NP-PA600Xs Circuit PDFDocumento32 pagineNP-PA600Xs Circuit PDFImthiyas AhmedNessuna valutazione finora

- OBDII J1708/J1587 Simulator: FeaturesDocumento12 pagineOBDII J1708/J1587 Simulator: FeaturesRuberli de LimaNessuna valutazione finora

- Service Manual: DVD PlayerDocumento66 pagineService Manual: DVD PlayerJoel MarvalNessuna valutazione finora

- 1218 Datasheet PDFDocumento3 pagine1218 Datasheet PDFTarun PatelNessuna valutazione finora

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDa EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNessuna valutazione finora

- TVLCD201 261 (SM) PDFDocumento42 pagineTVLCD201 261 (SM) PDFViorel CioataNessuna valutazione finora

- DTMF Proj Report (Final)Documento31 pagineDTMF Proj Report (Final)Jason RamosNessuna valutazione finora

- Digital Signal Processing: Instant AccessDa EverandDigital Signal Processing: Instant AccessValutazione: 3.5 su 5 stelle3.5/5 (2)

- LS01 ServiceDocumento53 pagineLS01 ServicehutandreiNessuna valutazione finora

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxDa EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxValutazione: 4 su 5 stelle4/5 (2)

- Service Manual: DP-IF5100Documento34 pagineService Manual: DP-IF5100Kasi XswlNessuna valutazione finora

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Da EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Nessuna valutazione finora

- Cellphone Operated Robotic ArmDocumento55 pagineCellphone Operated Robotic ArmVinay ReddyNessuna valutazione finora

- LS21W Service ManualDocumento41 pagineLS21W Service ManualaldoNessuna valutazione finora

- Pioneer Pfp42a3hd Plasma TV Training ManualDocumento103 paginePioneer Pfp42a3hd Plasma TV Training Manualdann222Nessuna valutazione finora

- Casio CTK541 Service ManualDocumento25 pagineCasio CTK541 Service ManualAlex Hernández50% (2)

- DTM Software Operating ManualDocumento58 pagineDTM Software Operating ManualHiếu Khải Bạch MaiNessuna valutazione finora

- Service Manual: Model Dx-Ltdvd20Documento57 pagineService Manual: Model Dx-Ltdvd20Luis MorenoNessuna valutazione finora

- Mobile RobotDocumento3 pagineMobile Robotshaan0806Nessuna valutazione finora

- Shenzhen Noridc - BLE Sensor AppDocumento54 pagineShenzhen Noridc - BLE Sensor AppAlina AnaNessuna valutazione finora

- Chassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioDocumento16 pagineChassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioRobert Vicuña100% (1)

- Host/SDRAM Interface Controller Serial Interface Controller Boot ROM CPU (32bit RISC) DMA ControllerDocumento14 pagineHost/SDRAM Interface Controller Serial Interface Controller Boot ROM CPU (32bit RISC) DMA Controllerhuytran812Nessuna valutazione finora

- Encoder Board MACH3Documento12 pagineEncoder Board MACH3Minerva MartinezNessuna valutazione finora

- Hitachi LCD - Ls01 DVBT Service ManualDocumento65 pagineHitachi LCD - Ls01 DVBT Service ManualMauro MangialavoriNessuna valutazione finora

- Daewoo DPC 7900Documento39 pagineDaewoo DPC 7900dmst622Nessuna valutazione finora

- TFTV3225 Service Manual 102010 Coby 26-32Documento21 pagineTFTV3225 Service Manual 102010 Coby 26-32bigbrother4275% (4)

- TP6813 Data Sheet v1.0Documento10 pagineTP6813 Data Sheet v1.0Ljupco BozinovskiNessuna valutazione finora

- NHRC 2 Manual RevaDocumento34 pagineNHRC 2 Manual RevashubhamformeNessuna valutazione finora

- DTMF GenDocumento22 pagineDTMF GenMohammad R AssafNessuna valutazione finora

- Manual For Cycle 1Documento193 pagineManual For Cycle 1Seth GreeneNessuna valutazione finora

- Casio CTK530 ServiceDocumento18 pagineCasio CTK530 ServiceAdilson SouzaNessuna valutazione finora

- ECU-AIM Logger 110 EngDocumento56 pagineECU-AIM Logger 110 EngHabib GürbüzNessuna valutazione finora

- Mobile Operated Land RoverDocumento21 pagineMobile Operated Land RoverGirishprasanna MKNessuna valutazione finora

- TK3302 - Service Manual PDFDocumento40 pagineTK3302 - Service Manual PDFsil182Nessuna valutazione finora

- Repair Your Casio CPS7 Piano and MIDI KeyboardDocumento16 pagineRepair Your Casio CPS7 Piano and MIDI KeyboardAsimAli100% (2)

- Kenwood - TK-2160 - 3160 Service ManualDocumento42 pagineKenwood - TK-2160 - 3160 Service ManualcornelisjjNessuna valutazione finora

- Draft Review Technical Specification For Digital Terrestrial Set Top BoxDocumento13 pagineDraft Review Technical Specification For Digital Terrestrial Set Top Boxpeter mureithiNessuna valutazione finora

- Tender 2013-B-OVS - IGW Softswitch ExpansionDocumento4 pagineTender 2013-B-OVS - IGW Softswitch ExpansionTechne PhobosNessuna valutazione finora

- QwesdDocumento2 pagineQwesdRenz EbenNessuna valutazione finora

- Sony KDL-22-32BX325 22-32BX326 32-40BX425 Chassis AZ2-TK Level III Televisor LCD Manual de Servicio PDFDocumento46 pagineSony KDL-22-32BX325 22-32BX326 32-40BX425 Chassis AZ2-TK Level III Televisor LCD Manual de Servicio PDFhskv20025525Nessuna valutazione finora

- Touch Screen OmronDocumento6 pagineTouch Screen OmronCesar VicenteNessuna valutazione finora

- Simple Absolute Method For Current Transformer Calibration: Andrew C. CorneyDocumento4 pagineSimple Absolute Method For Current Transformer Calibration: Andrew C. CorneyJaiprasad ReddyNessuna valutazione finora

- A Complete Narrow-Band Power Line Communication Node For AMRDocumento6 pagineA Complete Narrow-Band Power Line Communication Node For AMRSudheer KakaniNessuna valutazione finora

- Pic101 User ManualDocumento2 paginePic101 User Manualசசி குமார்Nessuna valutazione finora

- 7 Segment Counter CircuitDocumento1 pagina7 Segment Counter CircuitManoj Kumar Thadigoppula NethaNessuna valutazione finora

- Buck Boost Converter ReportDocumento5 pagineBuck Boost Converter ReportMehedi HasanNessuna valutazione finora

- Practical: 1 Unit Impulse Response: Num (0 0 1) Den (1 0.2 1) Impulse (Num, Den) Grid TitleDocumento20 paginePractical: 1 Unit Impulse Response: Num (0 0 1) Den (1 0.2 1) Impulse (Num, Den) Grid TitlealwaysharshNessuna valutazione finora

- Chapter 2 - Bipolar Junction TransistorsDocumento70 pagineChapter 2 - Bipolar Junction TransistorsHoang Dung SonNessuna valutazione finora

- PCB Layout Recommendations For Bga PackagesDocumento81 paginePCB Layout Recommendations For Bga PackagesovmlcabreraNessuna valutazione finora

- TPItL10 CtLv10 Com ENDocumento2 pagineTPItL10 CtLv10 Com ENJose Yamid Jojoa GomezNessuna valutazione finora

- Chapter 6 LogicDocumento49 pagineChapter 6 LogicProspect Teaches MathematicsNessuna valutazione finora

- ITC CPU Structure& FunctionDocumento2 pagineITC CPU Structure& FunctionMuhammed YousafNessuna valutazione finora

- GERAN ZTE Basic Handover Feature GuideDocumento31 pagineGERAN ZTE Basic Handover Feature Guidemikepadilla82100% (1)

- Finisar Ftlx1413m3bcl 10g LR 10km XFP Optical Transceiver Productspecrevd1Documento11 pagineFinisar Ftlx1413m3bcl 10g LR 10km XFP Optical Transceiver Productspecrevd1Madd000Nessuna valutazione finora

- PHILIPS LC04 LCD TV Technical Training ManualDocumento44 paginePHILIPS LC04 LCD TV Technical Training Manualcentauro2013Nessuna valutazione finora

- AD83586BDocumento62 pagineAD83586BGreen froggy movie clipsNessuna valutazione finora

- DmesgDocumento19 pagineDmesgChee KKNessuna valutazione finora

- Digital VoltmeterDocumento20 pagineDigital VoltmeterAbhigyan PrakashNessuna valutazione finora

- Orthogonal Frequency Division Multiplexing: Presented byDocumento12 pagineOrthogonal Frequency Division Multiplexing: Presented byTHIRUCHANOORU SREENATHNessuna valutazione finora

- Service Manual For Acer Aspire 5943gDocumento119 pagineService Manual For Acer Aspire 5943gFabian SchiemenzNessuna valutazione finora

- Decimator Prorack G Stereo MOD Manual2Documento9 pagineDecimator Prorack G Stereo MOD Manual2Stefanos_D100% (1)

- Pump Station PLC ControlDocumento9 paginePump Station PLC ControldanderjNessuna valutazione finora

- Satellite Comm. McqsDocumento68 pagineSatellite Comm. McqsZephNessuna valutazione finora

- Module 4 - Antenna Arrays - Dipoles PDFDocumento52 pagineModule 4 - Antenna Arrays - Dipoles PDFChaithra LakshmiNessuna valutazione finora

- MachineProblem 1 SAMSONDocumento2 pagineMachineProblem 1 SAMSONJon MichaelNessuna valutazione finora

- Model 53 Compression Load CellDocumento3 pagineModel 53 Compression Load CellLi'sNessuna valutazione finora

- Assignment No 11 of Applied Physics TanzeelDocumento10 pagineAssignment No 11 of Applied Physics TanzeelAmeer JaanNessuna valutazione finora