Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Configuración Cascode

Caricato da

Sandra OchoaDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Configuración Cascode

Caricato da

Sandra OchoaCopyright:

Formati disponibili

Configuracin Cascode

Alta impedancia de entrada Gran ancho de banda Alta impedancia de entrada Gana en tensin y corriente

Introduccin

Cascode

From Wikipedia, the free encyclopedia

Jump to: navigation, search The cascode is a two-stage amplifier composed of a transconductance amplifier followed by a current buffer. Compared to a single amplifier stage, this combination may have one or more of the following characteristics: higher input-output isolation, higher input impedance, high output impedance, higher gain or higher bandwidth. In modern circuits, the cascode is often constructed from two transistors (BJTs or FETs), with one operating as a common emitter or common source and the other as a common base or common gate. The cascode improves input-output isolation (or reverse transmission) as there is no direct coupling from the output to input. This eliminates the Miller effect and thus contributes to a much higher bandwidth.

Contents

[hide]

1 History 2 Operation o 2.1 Stability o 2.2 Biasing o 2.3 Advantages o 2.4 Disadvantages o 2.5 Dual-gate version

3 Other applications 4 Two-port parameters o 4.1 Low frequency design o 4.2 High frequency design 5 Footnotes 6 References 7 See also

[edit] History

The cascode (sometimes verbified to cascoding) is a common technique for improving analog circuit performance, applicable to both vacuum tubes and transistors. The word "cascode" is a contraction of the phrase "cascade to cathode". It was first used in an article by F.V. Hunt and R.W. Hickman in 1939, in a discussion for application in low-voltage stabilizers.[1] They proposed a cascode of two triodes (first one with common cathode, the second one with common grid) as a replacement for a pentode.

[edit] Operation

Figure 1: N-channel cascode amplifier with resistive load (neglecting biasing details) Figure 1 shows an example of cascode amplifier with a common source amplifier as input stage driven by signal source Vin. This input stage drives a common gate amplifier as output stage, with output signal Vout. The major advantage of this circuit arrangement stems from the placement of the upper fieldeffect transistor (FET) as the load of the input (lower) FET's output terminal (drain). Because at operating frequencies the upper FET's gate is effectively grounded, the upper FET's source voltage (and therefore the input transistor's drain) is held at nearly constant voltage during operation. In other words, the upper FET exhibits a low input resistance to the lower FET,

making the voltage gain of the lower FET very small, which dramatically reduces the Miller feedback capacitance from the lower FET's drain to gate. This loss of voltage gain is recovered by the upper FET. Thus, the upper transistor permits the lower FET to operate with minimum negative (Miller) feedback, improving its bandwidth. The upper FET gate is electrically grounded, so charge and discharge of stray capacitance Cdg between drain and gate is simply through RD and the output load (say Rout), and the frequency response is affected only for frequencies above the associated RC time constant: = Cdg RD//Rout, namely f = 1/(2), a rather high frequency because Cdg is small. That is, the upper FET gate does not suffer from Miller amplification of Cdg. If the upper FET stage were operated alone using its source as input node (i.e. common-gate (CG) configuration), it would have good voltage gain and wide bandwidth. However, its low input impedance would limit its usefulness to very low impedance voltage drivers. Adding the lower FET results in a high input impedance, allowing the cascode stage to be driven by a high impedance source. If one were to replace the upper FET with a typical inductive/resistive load, and take the output from the input transistor's drain (i.e. a common-emitter (CE) configuration), the CE configuration would offer the same input impedance as the cascode, but the cascode configuration would offer a potentially greater gain and much greater bandwidth.

[edit] Stability

The cascode arrangement is also very stable. Its output is effectively isolated from the input both electrically and physically. The lower transistor has nearly constant voltage at both drain and source and thus there is essentially "nothing" to feed back into its gate. The upper transistor has nearly constant voltage at its gate and source. Thus, the only nodes with significant voltage on them are the input and output, and these are separated by the central connection of nearly constant voltage and by the physical distance of two transistors. Thus in practice there is little feedback from the output to the input. Metal shielding is both effective and easy to provide between the two transistors for even greater isolation when required. This would be difficult in one-transistor amplifier circuits, which at high frequencies would require neutralization.

[edit] Biasing

As shown, the cascode circuit using two "stacked" FET's imposes some restrictions on the two FET'snamely, the upper FET must be biased so its source voltage is high enough (the lower FET drain voltage may swing too low, causing it to make saturation). Insurance of this condition for FET's requires careful selection for the pair, or special biasing of the upper FET gate, increasing cost. The cascode circuit can also be built using bipolar transistors, or MOSFETs, or even one FET (or MOSFET) and one BJT. In the latter case, the BJT must be the upper transistor;

otherwise, the (lower) BJT will always saturate (unless extraordinary steps are taken to bias it).

[edit] Advantages

The cascode arrangement offers high gain, high slew rate, high stability, and high input impedance. The parts count is very low for a two-transistor circuit.

[edit] Disadvantages

The cascode circuit requires two transistors and requires a relatively high supply voltage. For the two-FET cascode, both transistors must be biased with ample VDS in operation, imposing a lower limit on the supply voltage.

[edit] Dual-gate version

A dual-gate MOSFET often functions as a "one-transistor" cascode. Common in the front ends of sensitive VHF receivers, a dual-gate MOSFET is operated as a common-source amplifier with the primary gate (usually designated "gate 1" by MOSFET manufacturers) connected to the input and the 2nd gate grounded (bypassed). Internally, there is one channel covered by the two adjacent gates; therefore, the resulting circuit is electrically a cascode composed of two FETs, the common lower-drain-to-upper-source connection merely being that portion of the single channel that lies physically adjacent to the border between the two gates.

[edit] Other applications

With the rise of integrated circuits, transistors have become cheap in terms of silicon die area. In MOSFET technology especially, cascoding can be used in current mirrors to increase the output impedance of the output current source. A modified version of the cascode can also be used as a modulator, particularly for amplitude modulation. The upper device supplies the audio signal, and the lower is the RF amplifier device.

[edit] Two-port parameters

The cascode configuration can be represented as a simple voltage amplifier (or more accurately as a g-parameter two-port network) by using its input impedance, output impedance, and voltage gain. These parameters are related to the corresponding g-parameters below.[2] Other useful properties not considered here are circuit bandwidth and dynamic range. BJT Cascode: low-frequency small-signal parameters[3]

Figure 2: BJT Cascode using ideal current sources for DC bias and large coupling capacitors to ground and to the AC signal source; capacitors are short circuits for AC The idealized small-signal equivalent circuit can be constructed for the circuit in figure 2 by replacing the current sources with open-circuits and the capacitors with short circuits, assuming they are large enough to act as short-circuits at the frequencies of interest. The BJTs can be represented in the small-signal circuit by the hybrid-pi model. Definition Voltage gain Input resistance Output resistance Expression

r2

MOSFET Cascode: low-frequency small-signal parameters[4]

Figure 3: MOSFET Cascode using ideal voltage sources for DC gate bias and a DC current source as active load Similarly the small-signal parameters can be derived for the MOSFET version, also replacing the MOSFET by its hybrid-pi model equivalent. This derivation can be simplified by noting that the MOSFET gate current is zero, so the small-signal model for the BJT becomes that of the MOSFET in the limit of zero base current: ,

where VT is the thermal voltage. Definition Voltage gain Input resistance Output resistance The combination of factors gmrO occurs often in the above formulas, inviting further examination. For the bipolar transistor this product is (see hybrid-pi model): . In a typical discrete bipolar device the Early voltage VA 100 V and the thermal voltage near room temperature is VT 25 mV, making gmrO 4000, a rather large number. From the article on hybrid-pi model, we find for the MOSFET in the active mode: Expression

(gm1rO1 + 1)gm2rO2

At the 65 nanometer technology node, ID 1.2 mA/ of width, supply voltage is VDD = 1.1 V; Vth 165 mV, and Vov = VGS-Vth 5%VDD 55 mV. Taking a typical length as twice the minimum, L = 2 Lmin = 0.130 m and a typical value of 1/(4 V/m L), we find 1/ 2 V, and gmrO 110, still a large value.[5] [6] The point is that because gmrO is large almost regardless of the technology, the tabulated gain and the output resistance for both the MOSFET and the bipolar cascode are very large. That fact has implications in the discussion that follows.

[edit] Low frequency design

Fig. 4 Top: Small-signal BJT cascode using hybrid-pi model Bottom: Equivalent circuit for BJT cascode using amplifier low-frequency parameters The g-parameters found in the above formulas can be used to construct a small-signal voltage amplifier with the same gain, input and output resistance as the original cascode (an equivalent circuit). This circuit applies only at frequencies low enough that the transistor parasitic capacitances do not matter. The figure shows the original cascode (Fig. 1) and the equivalent voltage amplifier or g-equivalent two-port (Fig. 4). The equivalent circuit allows easier calculations of the behavior of the circuit for different drivers and loads. In the figure a Thvenin equivalent voltage source with Thvenin resistance RS drives the amplifier, and at the output a simple load resistor RL is attached. Using the equivalent circuit, the input voltage to the amplifier is (see article on voltage division): , which shows the importance of using a driver with resistance RS << Rin to avoid attenuation of the signal entering the amplifier. From the above amplifier characteristics, we see that Rin is infinite for the MOSFET cascode, so no attenuation of input signal occurs in that case. The BJT cascode is more restrictive because Rin = r2. In a similar fashion, the output signal from the equivalent circuit is ,

In low frequency circuits, a high voltage gain typically is desired, hence the importance of using a load with resistance RL >> Rout to avoid attenuation of the signal reaching the load. The formulas for Rout can be used either to design an amplifier with a sufficiently small output resistance compared to the load or, if that cannot be done, to decide upon a modified circuit, for example, to add a voltage follower that matches the load better. The earlier estimate showed that the cascode output resistance is very large. The implication is that many load resistances will not satisfy the condition RL >> Rout. (An important exception is driving a MOSFET as load, which has infinite low frequency input impedance.) However, the failure to satisfy the condition RL >> Rout is not catastrophic because the cascode gain also is very large. If the designer is willing, the large gain can be sacrificed to allow a low load resistance; for RL << Rout the gain simplifies as follows: . This gain is the same as that for the input transistor acting alone. Thus, even sacrificing gain the cascode produces the same gain as the single-transistor transconductance amplifier, but with wider bandwidth. Because the amplifiers are wide bandwidth, the same approach can determine the bandwidth of the circuit when a load capacitor is attached (with or without a load resistor). The assumption needed is that the load capacitance is large enough that it controls the frequency dependence, and bandwidth is not controlled by the neglected parasitic capacitances of the transistors themselves.

[edit] High frequency design

At high frequencies, the parasitic capacitances of the transistors (gate-to-drain, gate-tosource, drain-to body, and bipolar equivalents) must be included in the hybrid pi models to obtain an accurate frequency response. The design goals also differ from the emphasis on overall high gain as described above for low-frequency design. In high frequency circuits, impedance matching at the input and output of the amplifier is typically desired in order to eliminate signal reflections and maximize power gain. In the cascode, the isolation between the input and output ports still is characterized by a small reverse transmission term g12, making it easier to design matching networks because the amplifier is approximately unilateral.

[edit] Footnotes

Darlington transistor

From Wikipedia, the free encyclopedia

Jump to: navigation, search

Circuit diagram of a Darlington pair using NPN transistors In electronics, the Darlington transistor (often called a Darlington pair) is a compound structure consisting of two bipolar transistors (either integrated or separated devices) connected in such a way that the current amplified by the first transistor is amplified further by the second one.'.'[1] This configuration gives a much higher current gain (written , hfe, or hFE) than each transistor taken separately and, in the case of integrated devices, can take less space than two individual transistors because they can use a shared collector. Integrated Darlington pairs come packaged singly in transistor-like packages or as an array of devices (usually eight) in an integrated circuit. The Darlington configuration was invented by Bell Laboratories engineer Sidney Darlington in 1953. He patented the idea of having two or three transistors on a single chip, sharing a collector.[2] A similar configuration but with transistors of opposite type (NPN and PNP) is the Sziklai pair, sometimes called the "complementary Darlington."

Contents

[hide]

1 Behaviour 2 Disadvantages 3 See also 4 References 5 External links

[edit] Behaviour

A Darlington pair behaves like a single transistor with a high current gain (approximately the product of the gains of the two transistors). In fact, integrated devices have three leads (B, C and E), broadly equivalent to those of a standard transistor. A general relation between the compound current gain and the individual gains is given by:

If 1 and 2 are high enough (hundreds), this relation can be approximated with:

A typical modern device has a current gain of 1000 or more, so that only a small base current is needed to make the pair switch on. However, this high current gain comes with several drawbacks.

[edit] Disadvantages

One drawback is an approximate doubling of base-emitter voltage. Since there are two junctions between the base and emitter of the Darlington transistor, the equivalent baseemitter voltage is the sum of both base-emitter voltages:

For silicon-based technology, where each VBEi is about 0.65 V when the device is operating in the active or saturated region, the necessary base-emitter voltage of the pair is 1.3 V. Another drawback of the Darlington pair is its increased "saturation" voltage. The output transistor is not allowed to saturate (i.e. its base-collector junction must remain reversebiased) because the first transistor, when saturated, establishes full (100%) parallel negative feedback between the collector and the base of the second transistor[3]. Since collector-emitter voltage is equal to the sum of its own base-emitter voltage and the collector-emitter voltage of the first transistor, both positive quantities in normal operation, it always exceeds the baseemitter voltage. (In symbols, VCE2 = VBE2 + VCE1, so VC2 > VB2 always.) Thus the "saturation" voltage of a Darlington transistor is one VBE (about 0.65 V in silicon) higher than a single transistor saturation voltage, which is typically 0.1 - 0.2 V in silicon. For equal collector currents, this drawback translates to an increase in the dissipated power for the Darlington transistor over a single transistor. The increased low output level can cause troubles when TTL logic circuits are driven. Another problem is a reduction in switching speed, because the first transistor cannot actively inhibit the base current of the second one, making the device slow to switch off. To alleviate this, the second transistor often has a resistor of a few hundred ohms connected between its base and emitter terminals.[1] This resistor provides a low impedance discharge path for the charge accumulated on the base-emitter junction, allowing a faster transistor turn-off.

The Darlington pair has more phase shift at high frequencies than a single transistor and hence can more easily become unstable with negative feedback (i.e., systems that use this configuration can have poor phase margin due to the extra transistor delay). Darlington pairs are available as integrated packages or can be made from two discrete transistors; Q1 (the left-hand transistor in the diagram) can be a low power type, but normally Q2 (on the right) will need to be high power. The maximum collector current IC(max) of the pair is that of Q2. A typical integrated power device is the 2N6282, which includes a switchoff resistor and has a current gain of 2400 at IC=10A. A Darlington pair can be sensitive enough to respond to the current passed by skin contact even at safe voltages. Thus it can form the input stage of a touch-sensitive switch

Potrebbero piacerti anche

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- 9618 Cambridge International As and A Level Computer ScienceDocumento576 pagine9618 Cambridge International As and A Level Computer Science陈湛明100% (29)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- Example SQL RPG400 ProgramsDocumento7 pagineExample SQL RPG400 ProgramsalovanaNessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Power Cloud For Technical Sales Part 2 - Private CloudDocumento4 paginePower Cloud For Technical Sales Part 2 - Private CloudAnon19023100% (3)

- React Native GuideDocumento31 pagineReact Native Guidedvirus2012Nessuna valutazione finora

- Billing Project PythonDocumento21 pagineBilling Project PythonSONAM SHRIVASTAV100% (5)

- Autosar NotesDocumento10 pagineAutosar NotesSri RamNessuna valutazione finora

- NIOS CLIGuide 8.2 PDFDocumento234 pagineNIOS CLIGuide 8.2 PDFrhideNessuna valutazione finora

- CATV Products BrochureDocumento56 pagineCATV Products BrochurePhilip SaundersNessuna valutazione finora

- Dyna 86l 8086 P Training Development System With LCD PDFDocumento1 paginaDyna 86l 8086 P Training Development System With LCD PDFSoluchanNessuna valutazione finora

- Dell Inspiron N5110 Service ManualDocumento45 pagineDell Inspiron N5110 Service ManualMichael Daniel Espinoza BetancoNessuna valutazione finora

- Nirma: UniversityDocumento3 pagineNirma: UniversityBHENSDADIYA KEVIN PRABHULALNessuna valutazione finora

- Ultrasonic Sensors Gloves For Blind People Using Lilypad ArduinoDocumento8 pagineUltrasonic Sensors Gloves For Blind People Using Lilypad ArduinoLois MoyanoNessuna valutazione finora

- Quiz 07Documento11 pagineQuiz 07sullivan583Nessuna valutazione finora

- H-Delay: Hybrid Delay User GuideDocumento12 pagineH-Delay: Hybrid Delay User GuideBTNessuna valutazione finora

- Professional Summary:: Ramana : +919677095107Documento4 pagineProfessional Summary:: Ramana : +919677095107raamanNessuna valutazione finora

- V Cloud Point Zero Client User ManualDocumento108 pagineV Cloud Point Zero Client User Manualkus satria dNessuna valutazione finora

- UMTS RNC Product Description v1 04Documento82 pagineUMTS RNC Product Description v1 04tquanglongNessuna valutazione finora

- DemoDocumento5 pagineDemoDouglas GodinhoNessuna valutazione finora

- Power Monitor (R3) - Data - Sheet - V1Documento2 paginePower Monitor (R3) - Data - Sheet - V1prekNessuna valutazione finora

- Veyon Admin Manual en - 4.2.4Documento67 pagineVeyon Admin Manual en - 4.2.4prototipadoNessuna valutazione finora

- ADE LAB UPDATED Manual-Draft 22 SCHEME - 23-24Documento87 pagineADE LAB UPDATED Manual-Draft 22 SCHEME - 23-24Harish G CNessuna valutazione finora

- UBD01 - FundamentalsDocumento3 pagineUBD01 - FundamentalsBerce Emanuel-ViniciusNessuna valutazione finora

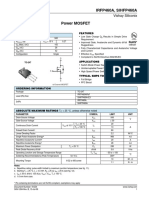

- Vishay IRFP460APBF Datasheet PDFDocumento8 pagineVishay IRFP460APBF Datasheet PDFkamel keddarNessuna valutazione finora

- Manua - eco-SPRAY Controller - INST-002834 - EN - ADocumento16 pagineManua - eco-SPRAY Controller - INST-002834 - EN - Asmith jackNessuna valutazione finora

- Things To Know : Instruction Format Instructions Can Have 1, 2 or No OperandsDocumento9 pagineThings To Know : Instruction Format Instructions Can Have 1, 2 or No OperandsMS. AYESHA SIDDIKA TONNYNessuna valutazione finora

- CCBoot Manual - TroubleshootsDocumento272 pagineCCBoot Manual - TroubleshootsHasnan IbrahimNessuna valutazione finora

- DIYfan - Adjustable Lab Power SupplyDocumento35 pagineDIYfan - Adjustable Lab Power SupplyDikerson CarlosNessuna valutazione finora

- Dynalink Telemetry System: Reliable Wireless Downhole Telemetry TechnologyDocumento2 pagineDynalink Telemetry System: Reliable Wireless Downhole Telemetry TechnologyRefisal BonnetNessuna valutazione finora

- Router Zte ZXHN H267NDocumento13 pagineRouter Zte ZXHN H267NFrancisco GonzalezNessuna valutazione finora

- PT070 WSTDocumento2 paginePT070 WSTMohammad kazem DehghaniNessuna valutazione finora