Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Wien Bridge Oscillator Documentation

Caricato da

Zahidur Ovi RahmanTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Wien Bridge Oscillator Documentation

Caricato da

Zahidur Ovi RahmanCopyright:

Formati disponibili

Tshwane University of Technology

Wien Bridge oscillator

Zahidur Rahman

Electronics III

Wien Bridge oscillator

Index Introduction Theoretical calculations Project specs General outcome Bibliography

Rahman Z

Page 2

Wien Bridge oscillator

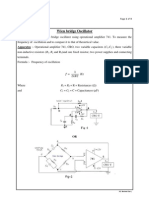

Introduction The Wien Bridge is one of the most common oscillators used in industry due to its simplicity and accuracy. The typical Wien Bridge consists of two parts, an RC circuit that causes a lead and lag property attribute to the output signal while a voltage divider similar to the op-amp non-inverting configuration. The lead and lag circuit is made from a RC combination in parallel with another RC combination in series. The lead and lag circuit causes a near perfect sine wave with a peak voltage 1/3rd of the input voltage.

Image extracted from internet PDF file (common lead-lag circuit) Above is the example of a lead and lag circuit, Vo is used at the positive input to the Op-Amp used for amplification. The RC combination causes a sine wave output. An example circuit of a Wien bridge is shown in the following figure

Image captured from Proteus simulation As shown above, the lead and lag circuit comprises of resistors R2 and R3 combined with capacitors C1 and C2. The lead and lag circuit is accompanied with a voltage divider circuit, the voltage gain of the lead lag circuit has an attenuating value of 1/3, this has to be balanced by the voltage divider circuit with a gain of 3 so that the combined gain will yield unity gain. By calculations, the default gain of the lead lag circuit will always lead to 1/3 regardless of resistor or capacitor values as long as the resistors and capacitors are identical. But the voltage divider circuit has to be physically made with resistors Rahman Z Page 3

Wien Bridge oscillator

In the above circuit, the voltage divider circuit is made with the combination of a 10k POT in parallel with resistor R1.

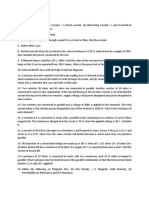

Theoretical calculations The following calculations are adapted from a power point slide and are relative to the following image:

Image taken from power point slide show

Formulas adapted from the circuit From the above formulas, the following general formulas can be found yielding calculations for frequency which is generated by the values in the lead lag circuit

Rahman Z

Page 4

Wien Bridge oscillator

General formula adapted from the lead and lag circuit Project specs In the design specs of the project, we are required to build a Wien Bridge oscillator with selectable frequencies, namely 20 Hz, 200Hz, 2 kHz and 20 kHz. These frequencies are attained by the use of the following values of resistors and a set value capacitor of 10 nF Resistor value 820 8.2 k 82 k 820 k Capacitor Value 10 nF 10 nF 10 nF 10 nF Output frequency 19.4 kHz 1.94 kHz 194 Hz 19.4 Hz

Selecting between these resistors in the circuit will ensure the selected frequencies. The output voltage has to be between 0.1Vp-p and 2Vp-p, in my circuit, the output voltage is controlled by a variable resistor in the voltage divider circuit which is not recommended under usual circumstances but since required voltages are so low compared to the input supply voltage of 18Vp-p by the use of a split supply, the controlling of the output voltage using the variable resistor at the voltage divider is also a usable method since the combination of two diodes in parallel with R1 in the circuit will cause a short circuit every time the gain is too high. What must be controlled on the other hand is that the closed loop gain does not go below 3, this will cause the signal to attenuate and eventually die out but it is an unlikely scenario.

Image captured from Proteus, actual circuit of vera-board Due to limitations, no Gerber file has been generated and the circuit has had to be adapted on veraboard for presentation. All values in the above circuit have been implemented on the actual circuit Rahman Z Page 5

Wien Bridge oscillator

and switches have been supplied to change the values of resistors R3 and R2 for the switching between frequencies. General outcomes Initially when simulating the circuit, no frequency could be read at the output since initially the output is equal to zero and both inputs are a result of the output. Due to further investigation into the circuit design, it had been discovered that a method was needed to jump start the circuit, if there was a output then the inputs would react, thus the switch had been implemented at the positive input to the Op-Amp, this would ensure there would be a change in comparison for the op amp to see and since the power inputs to the Op-Amp is positive and negative voltages, the output will switch between those two. Bibliography Google search: 48451550-wien-bridge-oscillator-shahkar-and-khaksaar.ppt http://www.circuitschematicdiagram.com/297-adjustable-frequency-sinewave-generator/ http://www.play-hookey.com/oscillators/wien_bridge_oscillator.html Gottlieb, Irving M., Practical Oscillator Handbook, Newnes, 1997. Kennedy, E. J., Operational Amplifier Circuits, Theory and Applications, Holt Rhienhart and Winston, 1988.

Rahman Z

Page 6

Potrebbero piacerti anche

- Signal Conditioning For Resistive, Rectance Varian and Self Generating SensorsDocumento74 pagineSignal Conditioning For Resistive, Rectance Varian and Self Generating SensorsYash BhattNessuna valutazione finora

- Operational Amplifier 741 As Wein Bridge Oscillator 1Documento4 pagineOperational Amplifier 741 As Wein Bridge Oscillator 1Deepak SharmaNessuna valutazione finora

- WaveletFiltering PDFDocumento96 pagineWaveletFiltering PDFÁron FehérNessuna valutazione finora

- Analog To Digital ConverterDocumento7 pagineAnalog To Digital ConverterRavi Patel100% (1)

- Analog Circuits-II Answer KeyDocumento30 pagineAnalog Circuits-II Answer KeyreneeshczNessuna valutazione finora

- Sine Wave Oscillator Circuits ExplainedDocumento11 pagineSine Wave Oscillator Circuits ExplainedDimas RioNessuna valutazione finora

- Chapter-4 Transient Circut Analysis Part 1Documento16 pagineChapter-4 Transient Circut Analysis Part 1temesgen adugnaNessuna valutazione finora

- Maxwell BridgeDocumento4 pagineMaxwell BridgeRohit Birnale0% (1)

- Wien Bridge Oscillator DesignDocumento16 pagineWien Bridge Oscillator DesignReece RevosaNessuna valutazione finora

- 15.RF Exp 15 HFSS Ring Hybrid DesignDocumento4 pagine15.RF Exp 15 HFSS Ring Hybrid DesignSolleti Suresh450% (2)

- Band Pass Filter Design Part 1. Band Pass Filters From First Principles Richard Harris G3OTKDocumento13 pagineBand Pass Filter Design Part 1. Band Pass Filters From First Principles Richard Harris G3OTKopachecoNessuna valutazione finora

- QPSKDocumento63 pagineQPSKNguyen Van Duong100% (1)

- Passive Low Pass FilterDocumento5 paginePassive Low Pass FilterAnonymous SOQFPWBNessuna valutazione finora

- Question Bank (ECE)Documento7 pagineQuestion Bank (ECE)Manav JainNessuna valutazione finora

- Unit-Ii Junction Diode Characteristics and Special Semi Conductor DiodesDocumento118 pagineUnit-Ii Junction Diode Characteristics and Special Semi Conductor DiodesradsradNessuna valutazione finora

- A.3 Additional Instrument Theory: A.3.1 Basic DC MetersDocumento10 pagineA.3 Additional Instrument Theory: A.3.1 Basic DC MetersadnaniaziNessuna valutazione finora

- شرح الكترونيات 1 AmplifiersDocumento43 pagineشرح الكترونيات 1 AmplifiersAboodA.KhraishiNessuna valutazione finora

- Basic Electronics Terms and DefinitionsDocumento26 pagineBasic Electronics Terms and Definitionspondu888Nessuna valutazione finora

- Voltmeter and Ammeter Loading EffectsDocumento30 pagineVoltmeter and Ammeter Loading EffectszsssxNessuna valutazione finora

- 7 Segment LED CounterDocumento7 pagine7 Segment LED CounterOPie UPieNessuna valutazione finora

- Solved Problems in Microwave EngineeringDocumento11 pagineSolved Problems in Microwave EngineeringTunde EmmanuelNessuna valutazione finora

- AC Voltmeter & OhmmeterDocumento17 pagineAC Voltmeter & OhmmeterBatch 3Nessuna valutazione finora

- Advanced Communication Lab ManualDocumento69 pagineAdvanced Communication Lab Manualbhavanimaddula50% (4)

- EE 442 Laboratory Experiment 2 Introduction To The Measurement of Voltage, Current, Resistance and Voltmeter LoadingDocumento12 pagineEE 442 Laboratory Experiment 2 Introduction To The Measurement of Voltage, Current, Resistance and Voltmeter LoadingAdrien MunyanezaNessuna valutazione finora

- Linear IC Applications: Active Filters ExplainedDocumento14 pagineLinear IC Applications: Active Filters Explainedeshwar_worldNessuna valutazione finora

- Laser Based Communication System PDFDocumento3 pagineLaser Based Communication System PDFPawan Kumar100% (1)

- Q) Explain Effect of Negative and Diagonal ClippingDocumento4 pagineQ) Explain Effect of Negative and Diagonal ClippingDivyanjaliNessuna valutazione finora

- Op-Amp MCQDocumento13 pagineOp-Amp MCQAbhisek Gautam BTNessuna valutazione finora

- RF Power Amplifier FundamentalsDocumento36 pagineRF Power Amplifier Fundamentalsi_spyder5388100% (1)

- First-Order Circuit ADocumento42 pagineFirst-Order Circuit ARay Ann RamonNessuna valutazione finora

- Module5 6 Imp QuestionsDocumento8 pagineModule5 6 Imp Questionsnikita SinghNessuna valutazione finora

- Time Domain AnalysisDocumento94 pagineTime Domain AnalysisAbhayNessuna valutazione finora

- Submitted By: Rameshkumar Lakshmi Prabha Abirami R LoganandhiniDocumento22 pagineSubmitted By: Rameshkumar Lakshmi Prabha Abirami R LoganandhiniAbirami RajaNessuna valutazione finora

- Time Responseof RL and RC NetworksDocumento5 pagineTime Responseof RL and RC Networkskudupudinagesh100% (1)

- Electronic Siren: October 3, 2013 by Engineeering Projects 0 CommentsDocumento5 pagineElectronic Siren: October 3, 2013 by Engineeering Projects 0 Commentssachin1391Nessuna valutazione finora

- Water Level Controller of Overhead Tanks Using Water Level Sense - Project ReportDocumento29 pagineWater Level Controller of Overhead Tanks Using Water Level Sense - Project ReportIrfan DanishNessuna valutazione finora

- Signal Conditioning CircuitsDocumento115 pagineSignal Conditioning CircuitsAmmad Ilyas100% (1)

- Electrical Symbols & Electronic SymbolsDocumento17 pagineElectrical Symbols & Electronic SymbolsMuhammad SajedNessuna valutazione finora

- Experiment02 PCM-EncodingDocumento13 pagineExperiment02 PCM-EncodingMary Rose P Delos SantosNessuna valutazione finora

- PLL FM Detector Using PLL IC 565Documento3 paginePLL FM Detector Using PLL IC 565Sagar MohanNessuna valutazione finora

- Loading Effects and Two-Port Networks Week 5 - 6Documento31 pagineLoading Effects and Two-Port Networks Week 5 - 6منتصر الجعبريNessuna valutazione finora

- EC2257-Lab Manual For Circuits and Simulation Integrated LaboratoryDocumento38 pagineEC2257-Lab Manual For Circuits and Simulation Integrated Laboratorygokila_dr9897Nessuna valutazione finora

- Boost DesignDocumento4 pagineBoost DesignmuthukumartharaniNessuna valutazione finora

- Chapter 4 - RF Oscillators and Frequency SynthesizersDocumento55 pagineChapter 4 - RF Oscillators and Frequency SynthesizersNhat Tran Xuan100% (1)

- Circuit Theory: First-Order CircuitsDocumento22 pagineCircuit Theory: First-Order Circuitsmalek992Nessuna valutazione finora

- Voltage and CurrentDocumento92 pagineVoltage and CurrentDominique Tuble EcleoNessuna valutazione finora

- Designing A Lock-In Amplifier With Analog To Digital ConversionDocumento27 pagineDesigning A Lock-In Amplifier With Analog To Digital Conversionessi12345Nessuna valutazione finora

- MCU Instruction Set ClassificationDocumento13 pagineMCU Instruction Set ClassificationKrapa Sai PraveenNessuna valutazione finora

- Laser Communication SystemDocumento4 pagineLaser Communication Systemjose273Nessuna valutazione finora

- Filter Low Pass Butterworth Design MultisimDocumento10 pagineFilter Low Pass Butterworth Design MultisimsanastasNessuna valutazione finora

- Transient of R.C. CircuitDocumento9 pagineTransient of R.C. CircuitArinder SinghNessuna valutazione finora

- FirDocumento35 pagineFirLiyana NasarudinNessuna valutazione finora

- RC Low Pass FilterDocumento8 pagineRC Low Pass FilterShaqer ZohaNessuna valutazione finora

- Electronics 3 Checkbook: The Checkbooks SeriesDa EverandElectronics 3 Checkbook: The Checkbooks SeriesValutazione: 5 su 5 stelle5/5 (1)

- The Fundamentals of Signal Transmission: Optical Fibre, Waveguides and Free SpaceDa EverandThe Fundamentals of Signal Transmission: Optical Fibre, Waveguides and Free SpaceNessuna valutazione finora

- The Wien Bridge OscillatorDocumento8 pagineThe Wien Bridge OscillatorSamuel ArthurNessuna valutazione finora

- Wien Bridge Oscillator:: RC Phase Shift Network (Lead Lag Network)Documento6 pagineWien Bridge Oscillator:: RC Phase Shift Network (Lead Lag Network)Rashid ManzoorNessuna valutazione finora

- Self Oscillating Class-D Audio Amplifier Circuit DesignDocumento29 pagineSelf Oscillating Class-D Audio Amplifier Circuit DesignnicchioNessuna valutazione finora

- Department of Home Affairs DH1738 Form 8Documento11 pagineDepartment of Home Affairs DH1738 Form 8Zahidur Ovi RahmanNessuna valutazione finora

- Opto Electronics Project - Fiber Optics TransmissionDocumento27 pagineOpto Electronics Project - Fiber Optics TransmissionZahidur Ovi RahmanNessuna valutazione finora

- State of Capture 14 October 2016Documento355 pagineState of Capture 14 October 2016eNCA.com85% (34)

- MBED With Nucleo F401REDocumento15 pagineMBED With Nucleo F401REZahidur Ovi RahmanNessuna valutazione finora

- P1 Matlab - Matlab in Control SystemsDocumento24 pagineP1 Matlab - Matlab in Control SystemsZahidur Ovi Rahman100% (1)

- TSE - VGA Final Project Report - Using Arduino and GameduinoDocumento65 pagineTSE - VGA Final Project Report - Using Arduino and GameduinoZahidur Ovi RahmanNessuna valutazione finora

- Safety in The WorkshopDocumento9 pagineSafety in The WorkshopZahidur Ovi RahmanNessuna valutazione finora

- The System of Safety Process PosterDocumento1 paginaThe System of Safety Process PosterZahidur Ovi RahmanNessuna valutazione finora

- Electrocommunications 3 - AssignmentDocumento7 pagineElectrocommunications 3 - AssignmentZahidur Ovi RahmanNessuna valutazione finora

- DC Choppers DocumentationDocumento20 pagineDC Choppers DocumentationZahidur Ovi RahmanNessuna valutazione finora

- HRM TechnicalDocumento25 pagineHRM TechnicalZahidur Ovi RahmanNessuna valutazione finora

- Chapter 14 - Transmission Lines DocumentationDocumento6 pagineChapter 14 - Transmission Lines DocumentationZahidur Ovi RahmanNessuna valutazione finora

- I 2CDocumento27 pagineI 2CZahidur Ovi RahmanNessuna valutazione finora

- Sweet Mika LullabyDocumento1 paginaSweet Mika LullabyZahidur Ovi RahmanNessuna valutazione finora

- Pointers in C++Documento1 paginaPointers in C++Zahidur Ovi RahmanNessuna valutazione finora

- Trickle Charger: Power Supplies in Depth TutorialDocumento13 pagineTrickle Charger: Power Supplies in Depth TutorialZahidur Ovi Rahman100% (1)

- BJT Frequency Responce PDFDocumento57 pagineBJT Frequency Responce PDFAlpha RomeoNessuna valutazione finora

- VoltageDocumento7 pagineVoltageRohini YejareNessuna valutazione finora

- Square Wave GeneratorDocumento7 pagineSquare Wave GeneratorswathiNessuna valutazione finora

- 50W DIY Hi-Fi Audio AmplifierDocumento7 pagine50W DIY Hi-Fi Audio AmplifierGoran ŠtetinNessuna valutazione finora

- VCO, PLL Principles and ApplicationsDocumento9 pagineVCO, PLL Principles and ApplicationsPrasitNessuna valutazione finora

- CKT08 PDFDocumento46 pagineCKT08 PDFShivam MishraNessuna valutazione finora

- EDC Question Bank 3rd SemDocumento3 pagineEDC Question Bank 3rd SemTamil C RathinamNessuna valutazione finora

- AMPLIFIERSDocumento4 pagineAMPLIFIERStinNessuna valutazione finora

- Fender TransformersDocumento2 pagineFender TransformersVincenzo TabaccoNessuna valutazione finora

- Hi-Fi tone control circuit using low noise transistorsDocumento8 pagineHi-Fi tone control circuit using low noise transistorsMuhammad YousafNessuna valutazione finora

- Harmonic Oscillators: DefinitionDocumento36 pagineHarmonic Oscillators: DefinitionCatalin ApetreNessuna valutazione finora

- Ecen 607 CMFB-2011Documento44 pagineEcen 607 CMFB-2011Girish K NathNessuna valutazione finora

- Analog Electronic Circuits Group - A (Multiple Choice Type Questions)Documento2 pagineAnalog Electronic Circuits Group - A (Multiple Choice Type Questions)Sudip MondalNessuna valutazione finora

- Butterworth and Chebyshev Filter Design Tutorial QuestionsDocumento1 paginaButterworth and Chebyshev Filter Design Tutorial Questionsy shuangNessuna valutazione finora

- Design of CMOS Low Dropout Voltage RegulatorDocumento32 pagineDesign of CMOS Low Dropout Voltage RegulatorDr. Sampatrao L PinjareNessuna valutazione finora

- Op Amp DesignDocumento8 pagineOp Amp DesignSermalingam ChandrasekarNessuna valutazione finora

- Ce CB CC ConfigurationDocumento5 pagineCe CB CC Configurationsumee123100% (1)

- MCQS From CareerRide (Oscillators, Digital Circuits)Documento10 pagineMCQS From CareerRide (Oscillators, Digital Circuits)Qaisar_mastNessuna valutazione finora

- UBC ELEC 301 MP Report 4Documento7 pagineUBC ELEC 301 MP Report 4ednangiaNessuna valutazione finora

- Esc201: Introduction To Electronics: Amit Verma Dept. of Electrical Engineering Iit KanpurDocumento30 pagineEsc201: Introduction To Electronics: Amit Verma Dept. of Electrical Engineering Iit KanpurPrakhar chhalotreNessuna valutazione finora

- 15ee46 Opamp - LicDocumento7 pagine15ee46 Opamp - LicShankx ProductionsNessuna valutazione finora

- Digital To Analog ConverterDocumento4 pagineDigital To Analog ConverterWarNessuna valutazione finora

- Experiment 07-D2aDocumento4 pagineExperiment 07-D2aapi-277396867Nessuna valutazione finora

- ESC-EC 301 (New) - CSE - ITDocumento4 pagineESC-EC 301 (New) - CSE - ITred sparrowNessuna valutazione finora

- EC2257 Lab ManualDocumento48 pagineEC2257 Lab Manualmmrr24jesusNessuna valutazione finora

- Routh Criterion - Tutorial 7 - Co - 12Documento3 pagineRouth Criterion - Tutorial 7 - Co - 12Haelu KuNessuna valutazione finora

- Wien Bridge Oscillator DocumentationDocumento6 pagineWien Bridge Oscillator DocumentationZahidur Ovi Rahman100% (1)

- Find the Load Voltage vL for Circuit with Two Op-AmpsDocumento21 pagineFind the Load Voltage vL for Circuit with Two Op-AmpsSoulz Zampa100% (1)

- BM8411Documento142 pagineBM8411Gayathri M100% (1)

- EX. NO: 1 Inverting, Non-Inverting Amplifiers and Differential Amplifier DateDocumento125 pagineEX. NO: 1 Inverting, Non-Inverting Amplifiers and Differential Amplifier DateksrbalachandranNessuna valutazione finora