Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Lecture 18: Designing A Central Processor Unit 2: The Controller

Caricato da

Taqi ShahDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Lecture 18: Designing A Central Processor Unit 2: The Controller

Caricato da

Taqi ShahCopyright:

Formati disponibili

Lecture 18: Designing a Central Processor Unit 2: The Controller

In the last lecture we dened the format of the instructions and the register transfers that are required to execute them. We now turn to the question of building a synchronous machine that will be able to carry out each instruction. At rst this looks like a mammouth task, since we have so many possibilities. However with a bit of care, and a judicious use of Boolean algebra we will nd that we can manage the complexity quite easily.

The Fetch Cycle

Before we can execute an instruction we need to fetch it from memory. This will be the same for every instruction and will need the following register transfers: F1 MARPC; PCPC+1 F2 MDRMemory F3 IRMDR If only the memory were able to drive more than one register, we could shorten this to two cycles, but that is life. So, we now know that to execute one instruction we will need between three and seven clock cycles. We can now draw the nite state machine for our controller. At present we have not considered the outputs associated with each state. We will design the output logic later. At rst sight it looks remarkably simple, having only seven states. We scrapped the idle state in the manual processor, since the software department tells me that the processor will never be idle. If its not executing a program it will be interogating the input/output devices for new data.

The rst problem is to determine the conditions for the state changes. Clearly F1 to F2, F2 to F3 and E4 to F4 are unconditional, but for the others we will need to determine which instruction we are executing, and how many cycles it will need. This looks difcult, since the instruction is determined by an 8 bit opcode, and we dont really want 8 inputs to the state sequencing logic if we are to follow our established design method. Instead we will try to create a single input to the controller, called C, which will be 1 if we advance to the next state, and zero if we return to state F1. Our old friend the decoder (aka demultiplexer) will solve this problem for us. It takes a binary number as input and produces a unary output. We previously designed one functionally and it would be quite easy scale that design to 8 inputs and 256 outputs. If we connect the instruction register bits 31-24 to the input bits, then each of the 256 output lines indicates one particular instruction.

With this arrangement we know that if, for example, STORE=1 then we are executing a STORE instruction, and all other output lines from the decoder will be zero. We can therefore use the instruction names as Boolean

DOC112: Computer Hardware Lecture 18 1

variables when trying to determine our state sequences. We also noted that some instructions have exactly the same sequence of register transfers, so we can make this explicity by implementing simple disjunctions of the instructions, for example dened by the equations: ADDS= ADD + SUBTRACT + AND + OR + XOR SHIFTS = ASL + ASR + ROR Now suppose also that we do the state assignment, and we choose to use the table below, We can simply use another decoder to determine which state we are in. This time it is just a simple 3-8 decoder. State Q2 Q1 Q0 Minterm F1 0 0 0 Q2 Q1 Q0 F2 0 1 1 Q2 Q1 Q0 F3 0 0 1 Q2 Q1 Q0 E1 0 1 0 Q2 Q1 Q0 E2 1 0 0 Q2 Q1 Q0 E3 1 1 0 Q2 Q1 Q0 E4 1 1 1 Q2 Q1 Q0 Unused 1 0 1 Q2 Q1 Q0 This means we can use the state names as Boolean variables as well, and so we can now straightforwardly write equations expressing the conditions under which the processor will return to state F1, or advance to the next execute state. All we need to do is group our instructions according to how many execute states they take. For example, the instructions that need two execute cycles are RETURN, SHIFTS, MOVE, and JUMPINDIRECT, so the condition for returning from state E2 to state F1 is simply: (E2 (RETURN + SHIFTS + MOVE + STORE + JUMPINDIRECT)) Extending this to the other states we get a cumbersome, but easily comprehensible equation for the input to the controller (C): C= (F3.NOP) (E1 (SKIP+CLEAR+JUMP)) (E2 (RETURN + SHIFTS + MOVE + STORE + JUMPINDIRECT))) (E3 (COMP + DEC + INC + COMPARE + ADD + STOREINDIRECT + LOAD + CALL + CALLINDIRECT))

Now we have reduced our problem to a standard sequential design, which we can solve by the usual design method. The truth table that expresses the sequencing logic is as follows: C 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 This State F1 F2 F3 E1 E2 E3 E4 Unused F1 F2 F3 E1 E2 E3 E4 Unused Q2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Q1 0 1 0 1 0 1 1 0 0 1 0 1 0 1 1 0 Q0 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 Next State F2 F3 F1 F1 F1 F1 F1 F2 F3 E1 E2 E3 E4 F1 D2 0 0 0 0 0 0 0 0 0 0 1 1 1 0 D1 1 0 0 0 0 0 0 1 0 1 0 1 1 0 D0 1 1 0 0 0 0 0 1 1 0 0 0 1 0

2

DOC112: Computer Hardware Lecture 18

This yields the following Karnaugh Maps, and equations for the state sequencing logic:

D2 = CQ2Q1 + CQ1Q0 D1 = CQ1 + CQ2Q0 + Q2 Q1 Q0 D0 = Q2 Q1 Q0 + Q2 Q1Q0 + CQ2Q1Q0 The equation for D0 can be simplied further by use the exclusive or simplication rule D0 = Q2 (Q1Q0) + CQ2Q1Q0 . In practice this will not help since we have had to decode the states to generate the C signal. Given that we have already done this we can write: D1 = CQ1 + CQ2Q0 + F1 D0 = F1 + F2 + CE3 The nal circuit for the state sequencing logic is:

We need to back check the dont care states to see that the machine will not get trapped. It turns out that for C=0, the unused state will jump to F0 (000), and if C=1 it will jump to E2 (110). This is probably acceptable. In any case it should not be a problem as we will denitely need to add some extra hardware to force the processor to do a particular operation at start up. In practice this will be a jump to the start of a stored program in ROM, which will load a minimal operating system.

DOC112: Computer Hardware Lecture 18 3

The Output Logic

The nal step in designing the processor is to design the output logic for the controller. This is the logic that determines the values of the clock gates (c0-c14), the arithmetic functions (f0-f4) and the multiplexer settings (s0-s8). These values will depend on both the state of the processor and the instruction being executed. We will again make use of the Boolean variables: F1, F2, F3, E1, E2, E3, E4, LOAD, STORE, JUMP, etc. that we implemented with decoders when designing the state sequenceing logic.

The Clock Gates

During any state of the processor, certain registers are loaded, but not all registers. The clock gates control which registers are loaded by gating the system clock. For example, if we choose the MAR register, the circuit will be:

Thus, assuming that the controller changes its state on the falling edge of the clock, and the variable CMAR becomes 1 indicating that the MAR is to be loaded, then it will receive a clock pulse from the system clock on its next rising edge. If, on the other hand, CMAR=0 during any controller state then the MAR register cannot change. To determine the equation for CMAR, and the other clock gates, we need to go back to the register transfers and determine which cycles each register receives a clock pulse and for which instructions. Looking through the instructions we nd that: CMAR = F1 + E1(LOAD + STORE) + E2(LOADINDIRECT + STOREINDIRECT) In other words the MAR changes state always in state F1, and in E1, but only when the LOAD or STORE instructions are being executed, and lastly in state E2 when the LOADINDIRECT and STOREINDIRECT instructions are being executed. This is a simple Boolean equation for which we can construct a direct implementation. However, we can simplify it considerably if we note that during certain cycles it doesnt matter if we load the MAR, since we are not using the memory. Looking at the register transfers we do not need its value to be retained further than the next cycle, so we can write: CMAR = F1 + E1 + E2 Thus the circuit for determining the output c11 is:

The equation for the MDR is found similarly CMDR = F2 + E2LOAD + E3LOADINDIRECT and again we can simplify this since we usually only load the MDR on the cycle before we use it. However, we need to preserve its value between E1 and E3, during the LOADINDIRECT instruction, and so:

DOC112: Computer Hardware Lecture 18 4

CMDR = F2 + E2LOAD + E3 The instruction register IR c12 is even simpler since it always receives a clock edge in F2 and at no other time, thus CIR = F2 The memory clock, c13, receives a pulse only when a store instruction is executed. Hence we have: CMemory = E2STORE + E3STOREINDIRECT We cant simplify this for fear of corrupting the memory. The program counter has rather a nasty equation: CPC=F1+E1(CALL + CALLINDIRECT + JUMP + SKIP + SKIPPOSITIVEC + SKIPNEGATIVEC) + E2(JUMPINDIRECT+RETURN) + E3(CALLINDIRECT+CALL) Unfortunately it does not seem likely that we can simplify this further, since we need to maintain the value in the program counter from one instruction to the next. For the A register, (c7) we can always load it in cycle E1, and in some cases we need the value preserved through cycle E2. Hence we can use: CA = E1 + E2STOREINDIRECT The B register (c8) can always be loaded in the E2 state CB = E2 The C register records the result of an arithmetic operation for the next instruction. Since all arithmetic operations reach the result in E3 we could take the easy option and write: CC = E3 though this would mean that if a skip instruction were used after a non arithmetic operation (say a LOAD instruction) its result would be unpredictable, since the ALU carry would have been loaded during the E3 state of the LOAD instruction. A safer implementation would be to load it during E3, but only for one or two register instructions. Rather than write these out in full we could express this as: CC= E3(ONE+TWO) Where ONE and TWO are Boolean variables which become 1 when the instruction being executed uses, respectively, one or two registers. We can derive the equations for these from the register transfer tables, and implement them straightforwardly. We will see later that it will be helpful to use the Boolean variables ONE and TWO in other cases. We have now determined all the clock gates except for those of the seven general purpose registers. remember that we have been careful in dening the instruction bits to ensure that if a register is to be loaded its number will be stored in the instruction register at bits 20-23. Going through our register transfer denitions we can write that there should be a clock pulse on Rdest in the following conditions: CRdest = E4+ E3(ONE + LOAD ) + E2(SHIFT + MOVE + CALL+CALLINDIRECT) + E1CLEAR Where ONE, as above, means all the one register instructions, and SHIFT means any shift instruction, or, as a Boolean equation, SHIFT=ASL+ASR+LSR. This equation cannot be easily simplied, since the general purpose registers are used by the programmers and we cannot arbitrarily change their values. We need to decode bits 20 to 23. In the instruction we have allowed four bits for the register indicators, and so we will be able to incorporate up to sixteen registers if we choose to expand the processor. However, in the present design we have only seven, so a 3bit decoder will serve the purpose.

DOC112: Computer Hardware Lecture 18

Output Logic 2: The arithmetic function selectors.

The shifter function can be easily determined, since most of the time it is used it is in the unchanged mode (passing data from A to the internal bus). The shifts only occur in the shift instructions. The shifter function is described by the following table: Instruction Default ASL ASR ROR Function No Action Arithmetic Shift Left Arithmetic Shift Right Rotate Right f4 0 0 1 1 f3 0 1 0 1

From this table we can see that we can implement these function lines using: f4 = ASR+ROR f3 = ASL+ROR The default is then 00 and need not be explicitly set. The use of the ALU is as follows: Instruction Default Unused E3(SUBTRACT + COMPARE) E3(DEC + INC + ADD) E3COMP E3OR E3AND E2(DEC + COMP) Function Zero B-A A-B AplusB AB A+B AB -1 f2 0 0 0 0 1 1 1 1 f1 0 0 1 1 0 0 1 1 f0 0 1 0 1 0 1 0 1

As with the shifter we need look at the table columns to determine the equations for the function bits, so: f2 = E3(COMP+OR+AND) + E2(COMP+DEC) f1 = E3(SUBTRACT+COMPARE+DEC+INC+ADD+AND) + E2(COMP+DEC) f0 =E3(DEC + INC + ADD + OR) +E2(COMP+DEC) The carry input is required to be a 1 in only 1 place, which is INCE3. For all other cases it must be set to zero. Hence we have: f4 = INCE3

Output Logic 3: The Select Inputs

The selection inputs are dened by the following three tables.

DOC112: Computer Hardware Lecture 18 6

Selection R0 R1 R2 R3 R4 R5 R6 Bus

s2 0 0 0 0 1 1 1 1

s1 0 0 1 1 0 0 1 1

s0 0 1 0 1 0 1 0 1

Selection Shifter ALU PC Mask MDR

s6 0 0 0 0 1 1 1 1

s5 0 0 1 1 0 0 1 1

s4 0 1 0 1 0 1 0 1

Selection Bus Incrementer

s3 0 1

In most cases the register select, s2,s1,s0 can be taken directly from the Rsrc or the Rdest elds of the instructions. Examining the register transfers we nd that A and B are loaded from the bus (as opposed to the registers) during E2INC, E2COMP and E2DEC. In fact we note that if we are executing a one register instruction we can always set the selector for A and B to the bus (1,1,1). So we can write this condition as SBus = E2ONE At other times A and B can be loaded from the registers. Going through the register transfers we see that A and B need to be connected to Rsrc, (which will be the instruction register bits 16-19) during state E1 for all the indirect instructions and all the two register instructions. At all other times it can be connected to Rdest, which is IR bits 20-23. This is required for the STORE instructions. We can therefore write another select condition as: SRsrc = E1(INDIRECT + TWO) With these two functions implemented we see that the selection bits s0,s1 and s2 can be provided by the following circuit.

The internal bus selector has three spare inputs, which we could use to add further functionality to the processor. The most common usage is to loop A back to the registers via the shifter, so we will set this as default, and look at the conditions where we need to select the other inputs. SPC = E2(CALL+CALLINDIRECT) SALU = E1CLEAR + (E2+E3)(INC+DEC+COMP) + TWOE3 SMask = E1LOAD+JUMP + STORE) + E3CALL SMDR = LOADE3 + E4 Looking again at the table dening the selection bits we can see that: S4 = SALU + SMAR S5 = SPC S6 = SMask + SMDR

DOC112: Computer Hardware Lecture 18

With thought we could probably simplify these equations by looking at the times when the internal bus is and isnt used, but for the moment we will press on. The PC selector has the default to be BUS (0) and we set it to the incrementer (1) with the following conditions: S3 = F1 + E1(CALL+CALLINDIRECT)

The Mark 2 version

This completes the design of the output logic, so we can now make a wiring list, simulate test and build the circuits. If we use components from maplin, it will only cost about twice as much as an Intel Core processor, and we can probably run it as fast as 100KHz (yes K not M). So, if we want to sell any we will need to think about a mark 2 version. Our aim in designing the mark one processor was to keep everything simple, but several of our choices would result in the speed being slower. So here are one or two suggestions as to how to make the mark 2 version of the processor go faster. Firstly, we used 32 bits for each instruction, but only four of our instruction set use those 32 bits. The rest are at most 16 bits. This means that for most of our fetch cycles we are fetching redundant bits from memory. In order to keep the speed up we still should fetch 32 bits at a time, but we could reduce the number of fetches if we could pack all instructions, other than the memory reference ones into 16 bits. This would reduce the number of fetch cycles by nearly half, and thus increase the speed by more than one quarter. There are many possible strategies we could adopt for this. The simplest would be to arrange some multiplexers so that we can switch either the top or the bottom sixteen bits of the IR to the controller inputs. The memory reference instructions could be forced to start on a 32 bit boundary by inserting a NOP instruction where necessary. There are more complex, and more efcient ways of packing up the program instructions. Secondly, we could introduce more arithmetic hardware. For example, we could introduce a 16 bit multiplier that multiplies the bottom bits 16 of A and B to produce a 32 bit result. Other hardware additions could include a register to record when the result of an arithmetic operation was zero. By adding in a multiplexer to select register B independently from A we could almost certainly reduce the number of execution cycles for a large number of instructions. Lastly, we could consider ways in which we could speed up the clock. This would mean looking at the combinational logic (multiplexers and arithmetic circuits and the state sequencing and output logic) to see if we can optimise its speed.

DOC112: Computer Hardware Lecture 18

Potrebbero piacerti anche

- Projects With Microcontrollers And PICCDa EverandProjects With Microcontrollers And PICCValutazione: 5 su 5 stelle5/5 (1)

- Lecture 18: Designing A Central Processor Unit 2: The ControllerDocumento8 pagineLecture 18: Designing A Central Processor Unit 2: The ControllerrinobiNessuna valutazione finora

- Conceptual Programming: Conceptual Programming: Learn Programming the old way!Da EverandConceptual Programming: Conceptual Programming: Learn Programming the old way!Nessuna valutazione finora

- Finite State Machine Representation of Sequential CircuitsDocumento38 pagineFinite State Machine Representation of Sequential CircuitsTaqi ShahNessuna valutazione finora

- Micro Controller Lab 3Documento11 pagineMicro Controller Lab 3Talk Shows CentreNessuna valutazione finora

- Lecture 9: Finite State Representation of Digital Circuits: DOC112: Computer Hardware Lecture 9 1Documento4 pagineLecture 9: Finite State Representation of Digital Circuits: DOC112: Computer Hardware Lecture 9 1Debashish PalNessuna valutazione finora

- Cool Muscle Frequently Asked QuestionDocumento5 pagineCool Muscle Frequently Asked QuestionsaileikNessuna valutazione finora

- Network with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationDa EverandNetwork with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationNessuna valutazione finora

- Control ReportDocumento15 pagineControl ReportKenshow Large50% (2)

- Interview Questions for IBM Mainframe DevelopersDa EverandInterview Questions for IBM Mainframe DevelopersValutazione: 1 su 5 stelle1/5 (1)

- Counter 163Documento7 pagineCounter 163Carla BarbosaNessuna valutazione finora

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDa EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNessuna valutazione finora

- Ca Assignment: Syeda Haima Batool Naqvi CS-18022Documento11 pagineCa Assignment: Syeda Haima Batool Naqvi CS-18022Haima NaqviNessuna valutazione finora

- Cc1110 Cc2510 Basic Software Examples OverviewDocumento9 pagineCc1110 Cc2510 Basic Software Examples Overviewalongdayx3Nessuna valutazione finora

- A Instrument Landing System AccountingDocumento13 pagineA Instrument Landing System AccountingvasudhaaaaaNessuna valutazione finora

- Capstone ResearchProject Moore Mealy MachineDocumento9 pagineCapstone ResearchProject Moore Mealy MachineAnish ChatterjeeNessuna valutazione finora

- Bai 15 - ADC and DAC On Spartan 3E Starter BoardDocumento6 pagineBai 15 - ADC and DAC On Spartan 3E Starter BoardNguyễn Hữu DuyNessuna valutazione finora

- Multiplication of Signed Numbers: CSE 430 - Assignment 3Documento15 pagineMultiplication of Signed Numbers: CSE 430 - Assignment 3alam sifatNessuna valutazione finora

- Unit 4Documento17 pagineUnit 4pranaykumarghosh41Nessuna valutazione finora

- Digital PID Controllers: Different Forms of PIDDocumento11 pagineDigital PID Controllers: Different Forms of PIDสหายดิว ลูกพระอาทิตย์Nessuna valutazione finora

- SCHNEIDER SMART LINK TO LORAWAN v1Documento31 pagineSCHNEIDER SMART LINK TO LORAWAN v1Sergio Latorre OlaveNessuna valutazione finora

- DC Motor LabviewDocumento23 pagineDC Motor Labviewsara_ogl7Nessuna valutazione finora

- Registers: DOC112: Computer Hardware Lecture 11 Slide 1Documento33 pagineRegisters: DOC112: Computer Hardware Lecture 11 Slide 1Taqi ShahNessuna valutazione finora

- Lab7 VerilogDocumento7 pagineLab7 Veriloghanhtinhkila76017Nessuna valutazione finora

- Lectures Section 3 ModifiedDocumento73 pagineLectures Section 3 ModifiedcoventryUkNessuna valutazione finora

- Must Also Perform The Necessary Arithmetic Using Signed 2's Complement Notation and Show The Results Indicating Overflow, If AnyDocumento18 pagineMust Also Perform The Necessary Arithmetic Using Signed 2's Complement Notation and Show The Results Indicating Overflow, If AnyramkumarNessuna valutazione finora

- Quiz 1 Solutions CS252 Graduate Computer ArchitectureDocumento12 pagineQuiz 1 Solutions CS252 Graduate Computer Architectureadchy7Nessuna valutazione finora

- Fakultas Teknik Universitas Negeri Yogyakarta Digital Control SystemDocumento9 pagineFakultas Teknik Universitas Negeri Yogyakarta Digital Control SystemErmin HamidovicNessuna valutazione finora

- Introduction: PID Controller Design: SystemDocumento14 pagineIntroduction: PID Controller Design: SystemRantharu AttanayakeNessuna valutazione finora

- D-Type Latch IIDocumento19 pagineD-Type Latch IIjames-lawsonNessuna valutazione finora

- BER MeterDocumento8 pagineBER Metersakti prasad nandaNessuna valutazione finora

- Project Underdamped SystemDocumento6 pagineProject Underdamped SystemPablo HenriqueNessuna valutazione finora

- Lab 06Documento7 pagineLab 06Andy MeyerNessuna valutazione finora

- Assignment 3 (HA16025)Documento7 pagineAssignment 3 (HA16025)Zakwan WanNessuna valutazione finora

- DPSD 2 MarksDocumento23 pagineDPSD 2 Marksbanthika3937Nessuna valutazione finora

- Files 3 Homework Solutions A5 Solution 081Documento5 pagineFiles 3 Homework Solutions A5 Solution 081Ivanildo GomesNessuna valutazione finora

- Finite State MachinesDocumento8 pagineFinite State MachinesHnd FinalNessuna valutazione finora

- Lab 14Documento11 pagineLab 14amalkatribNessuna valutazione finora

- Sequential Circuit Design: Slides ForDocumento23 pagineSequential Circuit Design: Slides ForRamarao ChNessuna valutazione finora

- Exp - 08 Flight86Documento6 pagineExp - 08 Flight86Muhammad SaqibNessuna valutazione finora

- Logic ControlDocumento75 pagineLogic ControljoeytorioNessuna valutazione finora

- Programmable Logic Controller (PLC) and Automation: SBO/ PMM/ EJ501/ Jun2011Documento31 pagineProgrammable Logic Controller (PLC) and Automation: SBO/ PMM/ EJ501/ Jun2011Jeeva RajNessuna valutazione finora

- NEW333Documento9 pagineNEW333Amish SuchakNessuna valutazione finora

- معمارية 2Documento13 pagineمعمارية 2firasvtNessuna valutazione finora

- 8 Digital Controller Realization: e (T) ADC G (Z) DAC P Lant U (KT) e (KT) U (T)Documento4 pagine8 Digital Controller Realization: e (T) ADC G (Z) DAC P Lant U (KT) e (KT) U (T)Yassine DjillaliNessuna valutazione finora

- C Microcontroller Bit Manipulations ExplainedDocumento4 pagineC Microcontroller Bit Manipulations Explainedheruye mulugetaNessuna valutazione finora

- Tutorial 9: The Manual Processor: DOC112: Computer Hardware Tutorial 9 1Documento2 pagineTutorial 9: The Manual Processor: DOC112: Computer Hardware Tutorial 9 1Taqi ShahNessuna valutazione finora

- Hardware Slides 08Documento30 pagineHardware Slides 08Taqi ShahNessuna valutazione finora

- Basic C AVRDocumento30 pagineBasic C AVRroberto-edmone-4957Nessuna valutazione finora

- Advanced PID Controller ImplementationDocumento13 pagineAdvanced PID Controller Implementationlizhi0007100% (1)

- Tutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Documento12 pagineTutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Chiquita WhiteNessuna valutazione finora

- Design Contest 2010 MentorDocumento27 pagineDesign Contest 2010 MentorUjjwal KantNessuna valutazione finora

- Sliding Mode Brushless DC Motor Current Torque Control AlgorithmsDocumento6 pagineSliding Mode Brushless DC Motor Current Torque Control Algorithmscarolain_msNessuna valutazione finora

- 4 - Design of Control UnitDocumento8 pagine4 - Design of Control UnitPradyumna YambarNessuna valutazione finora

- Lecture 10: A Design Example - Traffic Lights: The ProblemDocumento6 pagineLecture 10: A Design Example - Traffic Lights: The ProblemKapil_Kaushik_8847Nessuna valutazione finora

- Lecture 11: Registers: DOC112: Computer Hardware Lecture 11 1Documento4 pagineLecture 11: Registers: DOC112: Computer Hardware Lecture 11 1Jagdeep ArryNessuna valutazione finora

- Antenna Azimuth Controller DesignDocumento17 pagineAntenna Azimuth Controller DesignNisa Ien100% (5)

- Software Cost and Effort Estimation in Software Engineering ProcessDocumento16 pagineSoftware Cost and Effort Estimation in Software Engineering ProcessTaqi ShahNessuna valutazione finora

- Lect 4 Cost EstimationDocumento16 pagineLect 4 Cost EstimationTaqi ShahNessuna valutazione finora

- Software Testing StrategiesDocumento16 pagineSoftware Testing StrategiesTaqi ShahNessuna valutazione finora

- Software Testing TechniquesDocumento17 pagineSoftware Testing TechniquesTaqi Shah0% (1)

- Software Cost and Effort EstimationDocumento16 pagineSoftware Cost and Effort EstimationTaqi ShahNessuna valutazione finora

- Well Meadows Hospital NormalizationDocumento3 pagineWell Meadows Hospital NormalizationTaqi Shah50% (2)

- Software Engineering 1 - Lec 5 Software Project ManagmentDocumento68 pagineSoftware Engineering 1 - Lec 5 Software Project ManagmentTaqi ShahNessuna valutazione finora

- CH 01Documento16 pagineCH 01Taqi ShahNessuna valutazione finora

- Lect 3 Project ManagementDocumento46 pagineLect 3 Project ManagementTaqi ShahNessuna valutazione finora

- Normalization Exercise AnswerDocumento8 pagineNormalization Exercise Answermanisgurlz100% (2)

- Normalization NotesDocumento20 pagineNormalization NotesShenna Kim CasinilloNessuna valutazione finora

- Entity Relationship DiagramsDocumento12 pagineEntity Relationship Diagramsbunty142001Nessuna valutazione finora

- ERD To Relational Model ExampleDocumento7 pagineERD To Relational Model ExampleTaqi ShahNessuna valutazione finora

- Practice: A Generic ViewDocumento18 paginePractice: A Generic ViewTaqi ShahNessuna valutazione finora

- ERD Database Modeling.Documento53 pagineERD Database Modeling.Taqi ShahNessuna valutazione finora

- Process: A Generic ViewDocumento14 pagineProcess: A Generic ViewTaqi ShahNessuna valutazione finora

- CH 03Documento76 pagineCH 03Taqi ShahNessuna valutazione finora

- S.E Chap ModelsDocumento41 pagineS.E Chap ModelsTaqi ShahNessuna valutazione finora

- Hardware Tutorial Solution 09Documento2 pagineHardware Tutorial Solution 09Taqi ShahNessuna valutazione finora

- Process: A Generic ViewDocumento14 pagineProcess: A Generic ViewTaqi ShahNessuna valutazione finora

- Hardware Tutorial Solution 05Documento1 paginaHardware Tutorial Solution 05Taqi ShahNessuna valutazione finora

- Tutorial 9: The Manual Processor: DOC112: Computer Hardware Tutorial 9 1Documento2 pagineTutorial 9: The Manual Processor: DOC112: Computer Hardware Tutorial 9 1Taqi ShahNessuna valutazione finora

- Hardware Tutorial Solution 08Documento1 paginaHardware Tutorial Solution 08Taqi ShahNessuna valutazione finora

- English Solution2 - Class 10 EnglishDocumento34 pagineEnglish Solution2 - Class 10 EnglishTaqi ShahNessuna valutazione finora

- English Solution - Class 10 EnglishDocumento77 pagineEnglish Solution - Class 10 EnglishTaqi ShahNessuna valutazione finora

- Hardware Tutorial Solution 01Documento1 paginaHardware Tutorial Solution 01Taqi ShahNessuna valutazione finora

- Hardware Tutorial Solution 02Documento1 paginaHardware Tutorial Solution 02Taqi ShahNessuna valutazione finora

- Hardware Tutorial Solution 06Documento1 paginaHardware Tutorial Solution 06Taqi ShahNessuna valutazione finora

- Hardware Tutorial Solution 07Documento1 paginaHardware Tutorial Solution 07Taqi ShahNessuna valutazione finora

- Hardware Tutorial 08Documento2 pagineHardware Tutorial 08Taqi ShahNessuna valutazione finora

- Diagbootx: // Public Release 1Documento4 pagineDiagbootx: // Public Release 1Tedy AdhinegoroNessuna valutazione finora

- Simulation of Congestion Control Algorithm AimDocumento4 pagineSimulation of Congestion Control Algorithm AimHaru HarshuNessuna valutazione finora

- 351 DatasheetDocumento14 pagine351 DatasheetRafael NavarroNessuna valutazione finora

- Oracle Database 11g Transparent Data EncryptionDocumento40 pagineOracle Database 11g Transparent Data EncryptionYelena BytenskayaNessuna valutazione finora

- Stacks - Quesues and DequesDocumento23 pagineStacks - Quesues and DequesAbdallateef ShohdyNessuna valutazione finora

- Free Computer Fundamentals and Programming in C by Reema TharejaDocumento5 pagineFree Computer Fundamentals and Programming in C by Reema TharejaGopi S0% (1)

- Atmos S 351 - Service ManualDocumento40 pagineAtmos S 351 - Service ManualcuetlaxochitlNessuna valutazione finora

- FPM 2004Documento257 pagineFPM 2004Srikant SuruNessuna valutazione finora

- AssociationBetweenBRAFV600EMutationand MortalityDocumento9 pagineAssociationBetweenBRAFV600EMutationand MortalityMade RusmanaNessuna valutazione finora

- Mole Concept - L1rr PDFDocumento27 pagineMole Concept - L1rr PDFLegend KillerNessuna valutazione finora

- QE and Complex Numbers DPPDocumento9 pagineQE and Complex Numbers DPPsatishmhbdNessuna valutazione finora

- Pediatric Appendicitis ScoreDocumento6 paginePediatric Appendicitis ScorePinandhito LatukolanNessuna valutazione finora

- Electric Power Applications, Engine & Generator SizingDocumento120 pagineElectric Power Applications, Engine & Generator SizingDIPPOSNessuna valutazione finora

- Standard Test Method For Density and Void Content of Freshly Mixed Pervious ConcreteDocumento4 pagineStandard Test Method For Density and Void Content of Freshly Mixed Pervious ConcreteManaswini VadlamaniNessuna valutazione finora

- Circuits in MatlabDocumento38 pagineCircuits in MatlabRana UsmanNessuna valutazione finora

- Question For Practice Oracle (11g) With AnswersDocumento32 pagineQuestion For Practice Oracle (11g) With AnswersAnonymous J8V2pZZ100% (4)

- Power Off Reset Reason BackupDocumento5 paginePower Off Reset Reason Backupmohamed ahmedNessuna valutazione finora

- Precima Frenos FDW ATEX Operating InstructionsDocumento6 paginePrecima Frenos FDW ATEX Operating InstructionsToni RenedoNessuna valutazione finora

- Theories and Methods of Two Way Slab Design-5-8-2017Documento3 pagineTheories and Methods of Two Way Slab Design-5-8-2017amerta 4320Nessuna valutazione finora

- Lecture 4: Expert Systems: What Is An Expert System?Documento5 pagineLecture 4: Expert Systems: What Is An Expert System?Zerihun BekeleNessuna valutazione finora

- Electrosurgical Text HandboockDocumento94 pagineElectrosurgical Text HandboockThéu Castro100% (1)

- Temporal BroadeningDocumento10 pagineTemporal BroadeningMohamed BouhaddaNessuna valutazione finora

- Pov Nori Apr2007Documento31 paginePov Nori Apr2007DMRNessuna valutazione finora

- Chapter Five Decision Theories and AnalysisDocumento47 pagineChapter Five Decision Theories and AnalysisAbdela AyalewNessuna valutazione finora

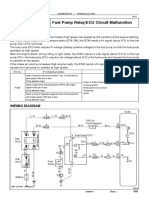

- DTC P1200 Fuel Pump Relay/ECU Circuit MalfunctionDocumento4 pagineDTC P1200 Fuel Pump Relay/ECU Circuit MalfunctiononealNessuna valutazione finora

- NDT VTL-3-3Documento2 pagineNDT VTL-3-3Priyesh MauryaNessuna valutazione finora

- SMS SRH-2D SedimentTransportDocumento19 pagineSMS SRH-2D SedimentTransportthendyNessuna valutazione finora

- Active Mathematics PDFDocumento22 pagineActive Mathematics PDFgoingforward77Nessuna valutazione finora

- Unit-III - EEFA - CostsDocumento70 pagineUnit-III - EEFA - CostsRamalingam ChandrasekharanNessuna valutazione finora

- Cells Bio-120-Exercise-4Documento7 pagineCells Bio-120-Exercise-4Paolo TenorioNessuna valutazione finora