Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Versatile Cmosttl Logic

Caricato da

bustandlukaDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Versatile Cmosttl Logic

Caricato da

bustandlukaCopyright:

Formati disponibili

circuit

ideas

92 February 2008 electroni cs for you www. e F y ma g . c o m

EFY Lab

VErsatiLE CMOs/ttL LOgiC

and CLOCk PrObE

S.C. DWIVEDI

F

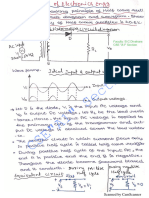

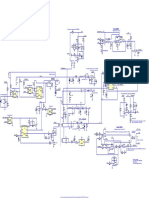

or fault diagnosis of any logic

circuit, you need a probe that can

test the logic level or existence of

clock activity. The circuit shown here

can be used to test CMOS and TTL

logic circuits for logic states and also

for the presence of clock activity from a

few hertz to more than 10 MHz, at any

point of the logic circuit.

Supply for the probe circuit is

taken from the circuit under test using

alligator clips. In the circuit, LM319

dual-comparator is connected as a

window detector. The non-invert-

ing pin of comparator N1 is biased

to nearly 2V when switch S1 is in

TTL position and 80 per cent of Vcc

in CMOS position. The output of N1

goes low only when logic input at the

probe tip exceeds the biasing voltage

and, as a result, the red LED lights up

to indicate logic 1 state at the probe

tip.

Similarly, the inverting pin of

comparator N2 is biased at nearly 0.8V

(in TTL position of switch S1) and 20

per cent of Vcc (in CMOS position of

switch S1). Only when the input volt-

Test Results

Test Specified Observed Red Green Yellow Buzzer

conditions level level LED LED LED sound

TTL (5V)

Low <0.8V <0.8V Off On Off Off

High >2V 2.1V On Off Off Off

Clock TTL 1Hzto10MHz Off Momentarily Onfor Onfor

compatible orevenmore on/off 3seconds 3seconds

CMOS (12V)

Low <2.5V 2.35V Off On Off Off

High >9.5V >9.5V On Off Off Off

Clock CMOS 1Hzto10MHz Off Momentarily Onfor Onfor

compatible orevenmore on/off 3seconds 3seconds

age at probe tip is less than the biasing

voltage, will its output drop low to

light up the green LED to indicate logic

0 state.

The probe tip is also connected to

the input of CD4049 (N3) via capacitor

C1 to pass AC/clock signals. It simply

acts as a buffer and couples only the

high-to-low going signals at the in-

put/output of the gate to the input of

next gate N4.

The output of gate N4 is further

coupled to gate N5, which is wired as a

monostable. A positive feedback from

circuit

ideas

electroni cs for you February 2008 93 www. e F y ma g . c o m

the output of gate N5 to the input of

gate N4 ensures that unless capacitor

C4 (0.47F) discharges suffciently via

4.7-mega-ohm resistor, further clock

pulses at the input of N4 will have no

effect.

Gate N6 is used for driving a yel-

low LED (indicating oscillatory input

at probe tip), which will be switched

on for a brief period. The output of

gate N6 is further used to inhibit/en-

able the oscillator formed by gates N7

and N8. It briefy activates the buzzer

to beep during mono period, indicat-

ing oscillatory input at the probe tip.

Thus we have audio-visual indication

during clock/oscillatory input at the

probe tip.

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Adv. Digital Circuit Design Clarkson UniversityDocumento30 pagineAdv. Digital Circuit Design Clarkson University1553Nessuna valutazione finora

- PICkit 2 64 - 80-Pin PIC18J - 51640aDocumento1 paginaPICkit 2 64 - 80-Pin PIC18J - 51640aPhilippe Diego DelasvegasNessuna valutazione finora

- chpt14 3Documento19 paginechpt14 3WESTLY JUCONessuna valutazione finora

- Warmly Welcome From My PresentationDocumento59 pagineWarmly Welcome From My PresentationPrinces Ofattacker100% (4)

- Eet 1240 OutlineDocumento2 pagineEet 1240 OutlinekhicomNessuna valutazione finora

- C8051F360 ShortDocumento2 pagineC8051F360 ShortMazlan Ab RahimNessuna valutazione finora

- Eel324: Physical Electronics: Metal Oxide Semiconductor Field Effect Transistors (Mosfets)Documento21 pagineEel324: Physical Electronics: Metal Oxide Semiconductor Field Effect Transistors (Mosfets)Vishal TomarNessuna valutazione finora

- 22ELN13Documento142 pagine22ELN13GAT LIBRARYNessuna valutazione finora

- 7 Segment LED CounterDocumento7 pagine7 Segment LED CounterOPie UPieNessuna valutazione finora

- IDT74FCT521AT/CT Fast Cmos 8-Bit Identity Comparator: Features: DescriptionDocumento6 pagineIDT74FCT521AT/CT Fast Cmos 8-Bit Identity Comparator: Features: DescriptionAnonymous T9HtUYccYANessuna valutazione finora

- Cascode MOS CircuitDocumento10 pagineCascode MOS CircuitAydin Mhysa AbetNessuna valutazione finora

- IOTADocumento3 pagineIOTAheri fauziNessuna valutazione finora

- Nte 4053Documento4 pagineNte 4053Codinasound CaNessuna valutazione finora

- ECE 3670 Electronics 3E 2013 FinalDocumento10 pagineECE 3670 Electronics 3E 2013 FinalrustyNessuna valutazione finora

- Audio Solution Guide For Analog TDADocumento12 pagineAudio Solution Guide For Analog TDAproctepNessuna valutazione finora

- Final EE 201 L VideoTaping Documentation With CaptioningDocumento3 pagineFinal EE 201 L VideoTaping Documentation With CaptioningBùi Khổng Thiên Thiên BùiNessuna valutazione finora

- Electronics Lab ManualDocumento246 pagineElectronics Lab ManualAji Vadakkedathu100% (1)

- 74HC HCT08Documento13 pagine74HC HCT08Adam SchwemleinNessuna valutazione finora

- ATX DPS-240EP v5 Blog1Documento1 paginaATX DPS-240EP v5 Blog1Maxi LopesNessuna valutazione finora

- 3 Phase Automatic ChangeoverDocumento25 pagine3 Phase Automatic ChangeoverDuhanNessuna valutazione finora

- Kendriya Vidyalaya Durg: CertificateDocumento18 pagineKendriya Vidyalaya Durg: Certificates praneetNessuna valutazione finora

- Innomed Medical: Top-X High Frequency X-Ray GeneratorsDocumento1 paginaInnomed Medical: Top-X High Frequency X-Ray GeneratorszNessuna valutazione finora

- 100 Watt Inverter Circuit: Circuit Diagram With Parts ListDocumento2 pagine100 Watt Inverter Circuit: Circuit Diagram With Parts ListCris DucusinNessuna valutazione finora

- Operational Amplifiers 2Documento55 pagineOperational Amplifiers 2Abdullah ShahNessuna valutazione finora

- Ece Comprehensive Exam-Answer Key-Ktunotes - inDocumento24 pagineEce Comprehensive Exam-Answer Key-Ktunotes - inArjun S Kumar0% (1)

- BJT Lecture 2Documento67 pagineBJT Lecture 2rktiwary256034Nessuna valutazione finora

- A Lowphasenoise Cmos Ring Oscillator With Differential Control ADocumento5 pagineA Lowphasenoise Cmos Ring Oscillator With Differential Control ABk201Nessuna valutazione finora

- Ele863 Lab ManualDocumento34 pagineEle863 Lab Manualnarayananmeera07Nessuna valutazione finora

- 1622 Service Manual Version BDocumento42 pagine1622 Service Manual Version BBIJUNessuna valutazione finora

- MCQ in Electronic Circuits Part 4Documento17 pagineMCQ in Electronic Circuits Part 4Palani C100% (2)