Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

HEF4017B

Caricato da

Homi PerezDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

HEF4017B

Caricato da

Homi PerezCopyright:

Formati disponibili

1.

General description

The HEF4017B is a 5-stage Johnson decade counter with ten spike-free decoded active

HIGH outputs (Q0 to Q9), an active LOW carry output from the most significant flip-flop

(Q5-9), active HIGH and active LOW clock inputs (CP0, CP1) and an overriding

asynchronous master reset input (MR).

The counter is advanced by either a LOW-to-HIGH transition at CP0 while CP1 is LOW or

a HIGH-to-LOW transition at CP1 while CP0 is HIGH (see Table 3).

When cascading counters, the Q5-9 output, which is LOW while the counter is in states 5,

6, 7, 8, and 9, can be used to drive the CP0 input of the next counter. A HIGH on MR

resets the counter to zero (Q0 = Q5-9 = HIGH; Q1 to Q9 = LOW) independent of the clock

inputs (CP0, CP1).

Automatic counter code correction is provided by an internal circuit: following any illegal

code the counter returns to a proper counting mode within 11 clock pulses.

Schmitt trigger action makes the clock inputs highly tolerant of slower rise and fall times.

It operates over a recommended V

DD

power supply range of 3 V to 15 V referenced to V

SS

(usually ground). Unused inputs must be connected to V

DD

, V

SS

, or another input.

2. Features and benefits

Automatic counter correction

Tolerant of slow clock rise and fall times

Fully static operation

5 V, 10 V, and 15 V parametric ratings

Standardized symmetrical output characteristics

Specified from 40 C to +125 C

Complies with JEDEC standard JESD 13-B

3. Ordering information

HEF4017B

5-stage Johnson decade counter

Rev. 8 18 November 2011 Product data sheet

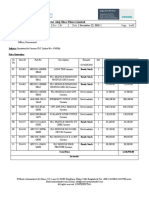

Table 1. Ordering information

All types operate from 40 C to +125 C

Type number Package

Name Description Version

HEF4017BP DIP16 plastic dual in-line package; 16 leads (300 mil) SOT38-4

HEF4017BT SO16 plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 2 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

4. Functional diagram

Fig 1. Functional diagram

Fig 2. Logic diagram

001aah242

DECODING AND OUTPUT CIRCUITRY

5-STAGE JOHNSON COUNTER

Q0

CP0

MR

15

14

13

CP1

3

Q1

2

Q2

4

Q3

7

Q4

10

Q5

1

Q6

5

Q7

6

Q8

9

Q9

Q5-9

11

12

001aah243

FF

1

D

CP

RD

Q

Q

FF

2

D

CP

RD

Q

Q

FF

3

D

CP

RD

Q

Q

FF

4

D

CP

RD

Q

Q

FF

5

D

CP

RD

Q

Q

Q0

CP1

CP0

MR

Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q5-9

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 3 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

5. Pinning information

5.1 Pinning

5.2 Pin description

Fig 3. Logic symbol Fig 4. IEE logic symbol

Q9

Q5-9

11

12

Q8 9

MR 15

14

13

CP0

CP1

Q7 6

Q6

Q5 1

5

Q4

Q3 7

10

Q2 4

Q1 2

Q0 3

001aah239

9

CT5

11

12

8

9

CT = 0

CTRDIV10/DEC

15

13

14

7

6

6

5

1

5

4

3

7

10

2

4

1

2

0

3

001aah240

&

Fig 5. Pin configuration

HEF4017B

Q5 V

DD

Q1 MR

Q0 CP0

Q2 CP1

Q6 Q5-9

Q7 Q9

Q3 Q4

V

SS

Q8

001aae574

1

2

3

4

5

6

7

8

10

9

12

11

14

13

16

15

Table 2. Pin description

Symbol Pin Description

Q0 to Q9 3, 2, 4, 7, 10, 1, 5, 6, 9, 11 decoded output

V

SS

8 ground supply voltage

Q5-9 12 carry output (active LOW)

CP1 13 clock input (HIGH-to-LOW edge-triggered)

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 4 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

6. Functional description

[1] H = HIGH voltage level; L = LOW voltage level; X = dont care;

| = positive-going transition; + = negative-going transition.

CP0 14 clock input (LOW-to-HIGH edge-triggered)

MR 15 master reset input

V

DD

16 supply voltage

Table 2. Pin description continued

Symbol Pin Description

Table 3. Function table

[1]

MR CP0 CP1 Operation

H X X Q0 = Q5-9 = H; Q1 to Q9 = L

L H + counter advances

L | L counter advances

L L X no change

L X H no change

L H | no change

L + L no change

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 5 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

7. Limiting values

Fig 6. Timing diagram

001aah244

CP0 INPUT

CP1 INPUT

MR INPUT

Q0 OUTPUT

Q1 OUTPUT

Q2 OUTPUT

Q3 OUTPUT

Q4 OUTPUT

Q5 OUTPUT

Q6 OUTPUT

Q7 OUTPUT

Q8 OUTPUT

Q9 OUTPUT

Q5-9 OUTPUT

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter Conditions Min Max Unit

V

DD

supply voltage 0.5 +18 V

I

IK

input clamping current V

I

< 0.5 V or V

I

> V

DD

+ 0.5 V - 10 mA

V

I

input voltage 0.5 V

DD

+ 0.5 V

I

OK

output clamping current V

O

< 0.5 V or V

O

> V

DD

+ 0.5 V - 10 mA

I

I/O

input/output current - 10 mA

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 6 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

[1] For DIP16 package: P

tot

derates linearly with 12 mW/K above 70 C.

[2] For SO16 package: P

tot

derates linearly with 8 mW/K above 70 C.

8. Recommended operating conditions

9. Static characteristics

I

DD

supply current - 50 mA

T

stg

storage temperature 65 +150 C

T

amb

ambient temperature 40 +125 C

P

tot

total power dissipation T

amb

= 40 C to +125 C

DIP16 package

[1]

- 750 mW

SO16 package

[2]

- 500 mW

P power dissipation per output - 100 mW

Table 4. Limiting values continued

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter Conditions Min Max Unit

Table 5. Recommended operating conditions

Symbol Parameter Conditions Min Typ Max Unit

V

DD

supply voltage 3 - 15 V

V

I

input voltage 0 - V

DD

V

T

amb

ambient temperature in free air 40 - +125 C

At/AV input transition rise and fall rate V

DD

= 5 V - - 3.75 s/V

V

DD

= 10 V - - 0.5 s/V

V

DD

= 15 V - - 0.08 s/V

Table 6. Static characteristics

V

SS

= 0 V; V

I

= V

SS

or V

DD

unless otherwise specified.

Symbol Parameter Conditions V

DD

T

amb

= 40 C T

amb

= 25 C T

amb

= 85 C T

amb

= 125 C Unit

Min Max Min Max Min Max Min Max

V

IH

HIGH-level

input voltage

,I

O

, < 1 A 5 V 3.5 - 3.5 - 3.5 - 3.5 - V

10 V 7.0 - 7.0 - 7.0 - 7.0 - V

15 V 11.0 - 11.0 - 11.0 - 11.0 - V

V

IL

LOW-level

input voltage

,I

O

, < 1 A 5 V - 1.5 - 1.5 - 1.5 - 1.5 V

10 V - 3.0 - 3.0 - 3.0 - 3.0 V

15 V - 4.0 - 4.0 - 4.0 - 4.0 V

V

OH

HIGH-level

output voltage

,I

O

, < 1 A;

V

I

= V

SS

or V

DD

5 V 4.95 - 4.95 - 4.95 - 4.95 - V

10 V 9.95 - 9.95 - 9.95 - 9.95 - V

15 V 14.95 - 14.95 - 14.95 - 14.95 - V

V

OL

LOW-level

output voltage

,I

O

, < 1 A;

V

I

= V

SS

or V

DD

5 V - 0.05 - 0.05 - 0.05 - 0.05 V

10 V - 0.05 - 0.05 - 0.05 - 0.05 V

15 V - 0.05 - 0.05 - 0.05 - 0.05 V

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 7 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

10. Dynamic characteristics

I

OH

HIGH-level

output current

V

O

= 2.5 V 5 V - 1.7 - 1.4 - 1.1 - 1.1 mA

V

O

= 4.6 V 5 V - 0.64 - 0.5 - 0.36 - 0.36 mA

V

O

= 9.5 V 10 V - 1.6 - 1.3 - 0.9 - 0.9 mA

V

O

= 13.5 V 15 V - 4.2 - 3.4 - 2.4 - 2.4 mA

I

OL

LOW-level

output current

V

O

= 0.4 V 5 V 0.64 - 0.5 - 0.36 - 0.36 - mA

V

O

= 0.5 V 10 V 1.6 - 1.3 - 0.9 - 0.9 - mA

V

O

= 1.5 V 15 V 4.2 - 3.4 - 2.4 - 2.4 - mA

I

I

input leakage

current

15 V - 0.1 - 0.1 - 1.0 - 1.0 A

I

DD

supply current I

O

= 0 A;

V

I

= V

SS

or V

DD

5 V - 5 - 5 - 150 - 150 A

10 V - 10 - 10 - 300 - 300 A

15 V - 20 - 20 - 600 - 600 A

C

I

input

capacitance

- - - - 7.5 - - - - pF

Table 6. Static characteristics continued

V

SS

= 0 V; V

I

= V

SS

or V

DD

unless otherwise specified.

Symbol Parameter Conditions V

DD

T

amb

= 40 C T

amb

= 25 C T

amb

= 85 C T

amb

= 125 C Unit

Min Max Min Max Min Max Min Max

Table 7. Dynamic characteristics

T

amb

= 25 C; V

SS

= 0 V; for test circuit see Figure 10

Symbol Parameter Conditions V

DD

Extrapolation formula

[1]

Min Typ Max Unit

t

PHL

HIGH to LOW

propagation delay

CP0, CP1 Q0 to Q9;

see Figure 7

5 V 113 ns + (0.55 ns/pF)C

L

- 140 280 ns

10 V 44 ns + (0.23 ns/pF)C

L

- 55 110 ns

15 V 32 ns + (0.16 ns/pF)C

L

- 40 80 ns

CP0, CP1 Q5-9;

see Figure 7

5 V 118 ns + (0.55 ns/pF)C

L

- 145 290 ns

10 V 44 ns + (0.23 ns/pF)C

L

- 55 110 ns

15 V 32 ns + (0.16 ns/pF)C

L

- 40 80 ns

MR Q1 to Q9;

see Figure 8

5 V 88 ns + (0.55 ns/pF)C

L

- 115 230 ns

10 V 39 ns + (0.23 ns/pF)C

L

- 50 100 ns

15 V 27 ns + (0.16 ns/pF)C

L

- 35 70 ns

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 8 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

[1] The typical values of the propagation delay and transition times are calculated from the extrapolation formulas shown (C

L

in pF).

[2] t

t

is the same as t

THL

and t

TLH

.

t

PLH

LOW to HIGH

propagation delay

CP0, CP1 Q0 to Q9;

see Figure 7

5 V 98 ns + (0.55 ns/pF)C

L

- 125 250 ns

10 V 39 ns + (0.23 ns/pF)C

L

- 50 100 ns

15 V 32 ns + (0.16 ns/pF)C

L

- 40 80 ns

CP0, CP1 Q5-9;

see Figure 7

5 V 98 ns + (0.55 ns/pF)C

L

- 125 250 ns

10 V 39 ns + (0.23 ns/pF)C

L

- 50 100 ns

15 V 32 ns + (0.16 ns/pF)C

L

- 40 80 ns

MR Q5-9;

see Figure 8

5 V 83 ns + (0.55 ns/pF)C

L

- 110 220 ns

10 V 34 ns + (0.23 ns/pF)C

L

- 45 90 ns

15 V 27 ns + (0.16 ns/pF)C

L

- 35 70 ns

MR Q0;

see Figure 8

5 V 103 ns + (0.55 ns/pF)C

L

- 130 260 ns

10 V 44 ns + (0.23 ns/pF)C

L

- 55 105 ns

15 V 32 ns + (0.16 ns/pF)C

L

- 40 75 ns

t

t

transition time see Figure 7 5 V

[2]

10 ns + (1.00 ns/pF)C

L

- 60 120 ns

10 V 9 ns + (0.42 ns/pF)C

L

- 30 60 ns

15 V 6 ns + (0.28 ns/pF)C

L

- 20 40 ns

t

h

hold time CP0 CP1;

see Figure 9

5 V 90 45 - ns

10 V 40 20 - ns

15 V 20 10 - ns

CP1 CP0;

see Figure 9

5 V 80 40 - ns

10 V 40 20 - ns

15 V 30 10 - ns

t

W

pulse width CP0 input LOW;

minimum width;

see Figure 8

5 V 80 40 - ns

10 V 40 20 - ns

15 V 30 15 - ns

CP1 input HIGH;

minimum width;

see Figure 8

5 V 80 40 - ns

10 V 40 20 - ns

15 V 30 15 - ns

MR input HIGH;

minimum width;

see Figure 8

5 V 50 25 - ns

10 V 30 15 - ns

15 V 20 10 - ns

t

rec

recovery time MR input;

see Figure 8

5 V 60 30 - ns

10 V 30 15 - ns

15 V 20 10 - ns

f

max

maximum

frequency

see Figure 8 5 V 6 12 - MHz

10 V 12 30 - MHz

15 V 15 30 - MHz

Table 7. Dynamic characteristics continued

T

amb

= 25 C; V

SS

= 0 V; for test circuit see Figure 10

Symbol Parameter Conditions V

DD

Extrapolation formula

[1]

Min Typ Max Unit

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 9 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

11. Waveforms

Table 8. Dynamic power dissipation P

D

P

D

can be calculated from the formulas shown. V

SS

= 0 V; t

r

= t

f

s 20 ns; T

amb

= 25 C.

Symbol Parameter V

DD

Typical formula for P

D

(W) where:

P

D

dynamic power

dissipation

5 V P

D

= 500 f

i

+ E(f

o

C

L

) V

DD

2

f

i

= input frequency in MHz;

f

o

= output frequency in MHz;

C

L

= output load capacitance in pF;

V

DD

= supply voltage in V;

E(C

L

f

o

) = sum of the outputs.

10 V P

D

= 2200 f

i

+ E(f

o

C

L

) V

DD

2

15 V P

D

= 6000 f

i

+ E(f

o

C

L

) V

DD

2

Conditions: CP1 = LOW, while CP0 triggers on a LOW-to-HIGH transition. CP1 triggers on a HIGH-to-LOW transition;

The shaded areas indicate where the output state is set by the input count.

Measurement points given in Table 9.

Fig 7. Waveforms showing the propagation delays for CP0, CP1 to Qn, Q5-9 outputs and the output transition

times

CP0 input

V

I

V

SS

V

I

V

SS

V

OH

V

OL

V

OH

V

OL

Q1 - Q9

output

CP1 input

V

M

V

M

t

PLH

t

PHL

t

PLH

t

PHL

V

M

t

TLH

t

THL

V

M

001aaj305

Q0, Q5 - Q9

output

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 10 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

Conditions: CP1 = LOW, while CP0 triggers on a LOW-to-HIGH transition, t

W

and t

rec

are measured when CP0 = HIGH and

CP1 triggers on a HIGH-to-LOW transition.

The shaded areas indicate where the output state is set by the input count.

Measurement points given in Table 9.

Fig 8. Waveforms showing the minimum pulse width for CP0, CP1 and MR input; the maximum frequency for

CP0 and CP1 input; the recovery time for MR and the MR input to Qn and Q5-9 output propagation delays

CP0 input

V

I

V

SS

V

I

V

SS

V

I

V

SS

V

OH

V

OL

V

OH

V

OL

Q1 - Q9

output

MR input

CP1 input

V

M

V

M

1/f

max

t

W

t

W

t

rec

V

M

1/f

max

t

W

t

PLH

t

PHL

V

M

V

M

001aaj306

Q0, Q5 - Q9

output

Hold times are shown as positive values, but may be specified as negative values;

Measurement points given in Table 9.

Fig 9. Waveforms showing hold times for CP0 to CP1 and CP1 to CP0

001aae578

CP0 input

V

I

V

SS

V

I

V

SS

CP1 input

t

h

V

M

V

M

V

M

t

h

V

M

Table 9. Measurement points

Supply voltage Input Output

V

DD

V

M

V

M

5 V to 15 V 0.5V

DD

0.5V

DD

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 11 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

12. Application information

Some examples of applications for the HEF4017B are:

Decade counter with decimal decoding

1 out of n decoding counter (when cascaded)

Sequential controller

Timer

Figure 11 shows a technique for extending the number of decoded output states for the

HEF4017B. Decoded outputs are sequential within each stage and from stage to stage,

with no dead time (except propagation delay).

a. Input waveforms

b. Test circuit

Test data is given in Table 10.

Definitions for test circuit:

DUT = Device Under Test;

C

L

= load capacitance including jig and probe capacitance;

R

T

= termination resistance should be equal to the output impedance Z

o

of the pulse generator.

Fig 10. Test circuit for measuring switching times

V

M

V

M

t

W

t

W

10 %

90 %

10 %

90 %

0 V

V

I

V

I

negative

pulse

positive

pulse

0 V

V

M

V

M

90 %

10 %

90 %

10 %

t

f

t

r

t

r

t

f

001aaj781

V

DD

V

I

V

O

001aag182

DUT

C

L R

T

G

Table 10. Test data

Supply voltage Input Load

V

DD

V

I

t

r

, t

f

C

L

5 V to 15 V V

SS

or V

DD

s 20 ns 50 pF

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 12 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

Enabling the counter on CP1 when CP0 is HIGH, or on CP0 when CP1 is LOW, causes an extra count.

Fig 11. Counter expansion

001aae577

8 decoded

outputs

8 decoded

outputs

CP0

CP1

Q0 Q1 Q8 Q9

HEF4017B

- - - -

CP0

CP1

Q0 Q1 Q8 Q9

HEF4017B

- - - -

CP0

CP1

Q1 Q8 Q9

HEF4017B

- - - - - -

MR

clock

first stage last stage intermediate stages

MR MR

9 decoded

outputs

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 13 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

13. Package outline

Fig 12. Package outline SOT38-4 (DIP16)

REFERENCES

OUTLINE

VERSION

EUROPEAN

PROJECTION

ISSUE DATE

IEC JEDEC JEITA

SOT38-4

95-01-14

03-02-13

M

H

c

(e )

1

M

E

A

L

s

e

a

t

i

n

g

p

l

a

n

e

A

1

w M

b

1

b

2

e

D

A

2

Z

16

1

9

8

E

pin 1 index

b

0 5 10 mm

scale

Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

UNIT

A

max.

1 2

b

1

(1) (1)

(1)

b

2

c D E e M

Z

H

L

mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

A

min.

A

max.

b

max.

w M

E

e

1

1.73

1.30

0.53

0.38

0.36

0.23

19.50

18.55

6.48

6.20

3.60

3.05

0.254 2.54 7.62

8.25

7.80

10.0

8.3

0.76 4.2 0.51 3.2

inches

0.068

0.051

0.021

0.015

0.014

0.009

1.25

0.85

0.049

0.033

0.77

0.73

0.26

0.24

0.14

0.12

0.01 0.1 0.3

0.32

0.31

0.39

0.33

0.03 0.17 0.02 0.13

DIP16: plastic dual in-line package; 16 leads (300 mil) SOT38-4

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 14 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

Fig 13. Package outline SOT109-1 (SO16)

X

w M

A

A

1

A

2

b

p

D

H

E

L

p

Q

detail X

E

Z

e

c

L

v M A

(A )

3

A

8

9

1

16

y

pin 1 index

UNIT

A

max.

A

1

A

2

A

3

b

p

c D

(1)

E

(1) (1)

e H

E

L L

p

Q Z y w v

REFERENCES

OUTLINE

VERSION

EUROPEAN

PROJECTION

ISSUE DATE

IEC JEDEC JEITA

mm

inches

1.75

0.25

0.10

1.45

1.25

0.25

0.49

0.36

0.25

0.19

10.0

9.8

4.0

3.8

1.27

6.2

5.8

0.7

0.6

0.7

0.3

8

0

o

o

0.25 0.1

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

1.0

0.4

SOT109-1

99-12-27

03-02-19

076E07 MS-012

0.069

0.010

0.004

0.057

0.049

0.01

0.019

0.014

0.0100

0.0075

0.39

0.38

0.16

0.15

0.05

1.05

0.041

0.244

0.228

0.028

0.020

0.028

0.012

0.01

0.25

0.01 0.004

0.039

0.016

0 2.5 5 mm

scale

SO16: plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 15 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

14. Revision history

Table 11. Revision history

Document ID Release date Data sheet status Change notice Supersedes

HEF4017B v.8 20111118 Product data sheet - HEF4017B v.7

Modifications: Legal pages updated.

Changes in General description and Features and benefits.

Section Applications removed.

HEF4017B v.7 20110914 Product data sheet - HEF4017B v.6

HEF4017B v.6 20091105 Product data sheet - HEF4017B v.5

HEF4017B v.5 20090709 Product data sheet - HEF4017B v.4

HEF4017B v.4 20081209 Product data sheet - HEF4017B_CNV v.3

HEF4017B_CNV v.3 19950101 Product specification - HEF4017B_CNV v.2

HEF4017B_CNV v.2 19950101 Product specification - -

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 16 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

15. Legal information

15.1 Data sheet status

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term short data sheet is explained in section Definitions.

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

15.2 Definitions

Draft The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences of

use of such information.

Short data sheet A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended

for quick reference only and should not be relied upon to contain detailed and

full information. For detailed and full information see the relevant full data

sheet, which is available on request via the local NXP Semiconductors sales

office. In case of any inconsistency or conflict with the short data sheet, the

full data sheet shall prevail.

Product specification The information and data provided in a Product

data sheet shall define the specification of the product as agreed between

NXP Semiconductors and its customer, unless NXP Semiconductors and

customer have explicitly agreed otherwise in writing. In no event however,

shall an agreement be valid in which the NXP Semiconductors product is

deemed to offer functions and qualities beyond those described in the

Product data sheet.

15.3 Disclaimers

Limited warranty and liability Information in this document is believed to

be accurate and reliable. However, NXP Semiconductors does not give any

representations or warranties, expressed or implied, as to the accuracy or

completeness of such information and shall have no liability for the

consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental,

punitive, special or consequential damages (including - without limitation - lost

profits, lost savings, business interruption, costs related to the removal or

replacement of any products or rework charges) whether or not such

damages are based on tort (including negligence), warranty, breach of

contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason

whatsoever, NXP Semiconductors aggregate and cumulative liability towards

customer for the products described herein shall be limited in accordance

with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

Suitability for use NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in life support, life-critical or

safety-critical systems or equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of

NXP Semiconductors products in such equipment or applications and

therefore such inclusion and/or use is at the customers own risk.

Applications Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Customers are responsible for the design and operation of their applications

and products using NXP Semiconductors products, and NXP Semiconductors

accepts no liability for any assistance with applications or customer product

design. It is customers sole responsibility to determine whether the NXP

Semiconductors product is suitable and fit for the customers applications and

products planned, as well as for the planned application and use of

customers third party customer(s). Customers should provide appropriate

design and operating safeguards to minimize the risks associated with their

applications and products.

NXP Semiconductors does not accept any liability related to any default,

damage, costs or problem which is based on any weakness or default in the

customers applications or products, or the application or use by customers

third party customer(s). Customer is responsible for doing all necessary

testing for the customers applications and products using NXP

Semiconductors products in order to avoid a default of the applications and

the products or of the application or use by customers third party

customer(s). NXP does not accept any liability in this respect.

Limiting values Stress above one or more limiting values (as defined in

the Absolute Maximum Ratings System of IEC 60134) will cause permanent

damage to the device. Limiting values are stress ratings only and (proper)

operation of the device at these or any other conditions above those given in

the Recommended operating conditions section (if present) or the

Characteristics sections of this document is not warranted. Constant or

repeated exposure to limiting values will permanently and irreversibly affect

the quality and reliability of the device.

Terms and conditions of commercial sale NXP Semiconductors

products are sold subject to the general terms and conditions of commercial

sale, as published at http://www.nxp.com/profile/terms, unless otherwise

agreed in a valid written individual agreement. In case an individual

agreement is concluded only the terms and conditions of the respective

agreement shall apply. NXP Semiconductors hereby expressly objects to

applying the customers general terms and conditions with regard to the

purchase of NXP Semiconductors products by customer.

No offer to sell or license Nothing in this document may be interpreted or

construed as an offer to sell products that is open for acceptance or the grant,

conveyance or implication of any license under any copyrights, patents or

other industrial or intellectual property rights.

Export control This document as well as the item(s) described herein

may be subject to export control regulations. Export might require a prior

authorization from competent authorities.

Document status

[1][2]

Product status

[3]

Definition

Objective [short] data sheet Development This document contains data from the objective specification for product development.

Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.

Product [short] data sheet Production This document contains the product specification.

HEF4017B All information provided in this document is subject to legal disclaimers. NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 8 18 November 2011 17 of 18

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

Non-automotive qualified products Unless this data sheet expressly

states that this specific NXP Semiconductors product is automotive qualified,

the product is not suitable for automotive use. It is neither qualified nor tested

in accordance with automotive testing or application requirements. NXP

Semiconductors accepts no liability for inclusion and/or use of

non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in

automotive applications to automotive specifications and standards, customer

(a) shall use the product without NXP Semiconductors warranty of the

product for such automotive applications, use and specifications, and (b)

whenever customer uses the product for automotive applications beyond

NXP Semiconductors specifications such use shall be solely at customers

own risk, and (c) customer fully indemnifies NXP Semiconductors for any

liability, damages or failed product claims resulting from customer design and

use of the product for automotive applications beyond NXP Semiconductors

standard warranty and NXP Semiconductors product specifications.

15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks

are the property of their respective owners.

16. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

NXP Semiconductors HEF4017B

5-stage Johnson decade counter

NXP B.V. 2011. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 18 November 2011

Document identifier: HEF4017B

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section Legal information.

17. Contents

1 General description. . . . . . . . . . . . . . . . . . . . . . 1

2 Features and benefits . . . . . . . . . . . . . . . . . . . . 1

3 Ordering information. . . . . . . . . . . . . . . . . . . . . 1

4 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2

5 Pinning information. . . . . . . . . . . . . . . . . . . . . . 3

5.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

5.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3

6 Functional description . . . . . . . . . . . . . . . . . . . 4

7 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 5

8 Recommended operating conditions. . . . . . . . 6

9 Static characteristics. . . . . . . . . . . . . . . . . . . . . 6

10 Dynamic characteristics . . . . . . . . . . . . . . . . . . 7

11 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

12 Application information. . . . . . . . . . . . . . . . . . 11

13 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 13

14 Revision history. . . . . . . . . . . . . . . . . . . . . . . . 15

15 Legal information. . . . . . . . . . . . . . . . . . . . . . . 16

15.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 16

15.2 Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

15.3 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

15.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 17

16 Contact information. . . . . . . . . . . . . . . . . . . . . 17

17 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Potrebbero piacerti anche

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Aashto M288-17 Product Selection GuideDocumento1 paginaAashto M288-17 Product Selection GuideDem DemNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- 1994 Manual de Taller Bronco, Econoline, F-Series PDFDocumento208 pagine1994 Manual de Taller Bronco, Econoline, F-Series PDFOscar Cruz100% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Executive Summary: 2013 Edelman Trust BarometerDocumento12 pagineExecutive Summary: 2013 Edelman Trust BarometerEdelman100% (4)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Superlab Manual PDFDocumento76 pagineSuperlab Manual PDFGabriela Soares100% (1)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- A Project Report ON Strategic Purchasing Procedure, Systems and Policies (Hospital Industry)Documento20 pagineA Project Report ON Strategic Purchasing Procedure, Systems and Policies (Hospital Industry)amitwin1983Nessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- PDS DeltaV SimulateDocumento9 paginePDS DeltaV SimulateJesus JuarezNessuna valutazione finora

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Strategic Management SlidesDocumento150 pagineStrategic Management SlidesIqra BilalNessuna valutazione finora

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Documentation Report On School's Direction SettingDocumento24 pagineDocumentation Report On School's Direction SettingSheila May FielNessuna valutazione finora

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Management Accounting by Cabrera Solution Manual 2011 PDFDocumento3 pagineManagement Accounting by Cabrera Solution Manual 2011 PDFClaudette Clemente100% (1)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Section 1 Company Overview StandardsDocumento34 pagineSection 1 Company Overview StandardsChris MedeirosNessuna valutazione finora

- RSW - F - 01 " ": Building UtilitiesDocumento4 pagineRSW - F - 01 " ": Building Utilities62296bucoNessuna valutazione finora

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- P3 Past Papers Model AnswersDocumento211 pagineP3 Past Papers Model AnswersEyad UsamaNessuna valutazione finora

- Source:: APJMR-Socio-Economic-Impact-of-Business-Establishments - PDF (Lpubatangas - Edu.ph)Documento2 pagineSource:: APJMR-Socio-Economic-Impact-of-Business-Establishments - PDF (Lpubatangas - Edu.ph)Ian EncarnacionNessuna valutazione finora

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Technical Sheet Racloflex NTDocumento2 pagineTechnical Sheet Racloflex NTAnthony AngNessuna valutazione finora

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- Chapter 01 What Is Statistics?Documento18 pagineChapter 01 What Is Statistics?windyuriNessuna valutazione finora

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Philo Q2 Lesson 5Documento4 paginePhilo Q2 Lesson 5Julliana Patrice Angeles STEM 11 RUBYNessuna valutazione finora

- Atoma Amd Mol&Us CCTK) : 2Nd ErmDocumento4 pagineAtoma Amd Mol&Us CCTK) : 2Nd ErmjanviNessuna valutazione finora

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- I. Choose The Best Option (From A, B, C or D) To Complete Each Sentence: (3.0pts)Documento5 pagineI. Choose The Best Option (From A, B, C or D) To Complete Each Sentence: (3.0pts)thmeiz.17sNessuna valutazione finora

- IPA Smith Osborne21632Documento28 pagineIPA Smith Osborne21632johnrobertbilo.bertilloNessuna valutazione finora

- How Transformers WorkDocumento15 pagineHow Transformers Worktim schroderNessuna valutazione finora

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Taylor Series PDFDocumento147 pagineTaylor Series PDFDean HaynesNessuna valutazione finora

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Press Statement - Book Launching Shariah Forensic 27 Oct 2023Documento4 paginePress Statement - Book Launching Shariah Forensic 27 Oct 2023aNessuna valutazione finora

- Jurnal Job DescriptionDocumento13 pagineJurnal Job DescriptionAji Mulia PrasNessuna valutazione finora

- SievesDocumento3 pagineSievesVann AnthonyNessuna valutazione finora

- LC For Akij Biax Films Limited: CO2012102 0 December 22, 2020Documento2 pagineLC For Akij Biax Films Limited: CO2012102 0 December 22, 2020Mahadi Hassan ShemulNessuna valutazione finora

- Arudha PDFDocumento17 pagineArudha PDFRakesh Singh100% (1)

- MSDS Buffer Solution PH 4.0Documento5 pagineMSDS Buffer Solution PH 4.0Ardhy LazuardyNessuna valutazione finora

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Logistic RegressionDocumento7 pagineLogistic RegressionShashank JainNessuna valutazione finora

- Pearson R CorrelationDocumento2 paginePearson R CorrelationAira VillarinNessuna valutazione finora

- Banking Ombudsman 58Documento4 pagineBanking Ombudsman 58Sahil GauravNessuna valutazione finora

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)