Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Lab2 EP1S25

Caricato da

assnadDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Lab2 EP1S25

Caricato da

assnadCopyright:

Formati disponibili

Laboratory 2: Amplitude Modulation (AM) Implementation

I. Introduction In the present project, students are required to implement and simulate a simple amplitude modulated (AM) circuit in the Simulink environment (DSPBuilder), using two methodologies to build the cos() function: a hard-coded look-up table and the NumericalControlled Oscillator (NCO) Altera IP core. The design has to be downloaded to the FPGA device on the Stratix EP1S25 DSP development board to perform hardware simulation and verification. II. Theory Amplitude Modulation or AM involves the encoding of a carrier signal by variation of its amplitude in accordance with an input signal. In Amplitude Modulation (AM) the carrier signal cos(c n) modulates a signal x( n) , which typically has at least 10 times lower frequency than the carrier, as follows:

y ( n) = cos(c n) x( n)

Where is the carrier angular frequency with 0 c . c

(1)

However it is not always possible in real-time to call the function cos() numerous times (many computations required). Three more efficient approaches are: To use a hard-coded look-up table for the cos() function, where the index of the table is the input of the function and the values inside the table are the possible outputs To use an oscillator To use a recursive approach for the computation of the cos() function

In the present project, we will use the first two approaches to implement the cosine function. For the second method, the NCO IP core from Altera will be used to generated the required carrier signal. III. Background about DSP Builder and the Altera EP1S25 DSP development board Capabilities of DSP Builder and Simulink were introduced with an example design in the Tutorial: A/D and D/A Conversion on Altera Stratix EP1S25 Development Board using Simulink and DSP Builder [1], which contain a design targeting the 12-bit 125MHz A/D

and 14-bit 165 MHz D/A converters onboard. For further information about the Stratix EP1S25 DSP development board, the student is referred to [2] and [3]. IP cores are megafunctions that are already tested and optimized for specific platforms, in this case, Altera FPGAs. They avoid building functions from scratch, reducing design and test time. In the laboratory, we have several evaluation-version IP cores. They can be parameterized, simulated and downloaded to hardware; although this last feature is restricted to the time in which the design is being tested in hardware (once the connection between the PC and the board is terminated, the program running the IP core is deleted from the FPGA). For more information about Altera IP cores, the student is referred to [5]. In the present lab, students will implement the required cos() function using the Numerically Controlled Oscillator (NCO) IP core v6.1. NOTE: previous IP core versions are not guaranteed to work with the installed Matlab and Quartus II versions. IV. Requirements For this laboratory, students are required to accomplish the next requirements: Implement an AM circuit by applying Equation (1) from Section II. The cosine function must be implemented using a hard-coded look-up table, where the index of the table is the input of the function and the values inside the table are the possible outputs. The signal to be modulated must be acquired through the A/D converter onboard, and then multiplied with the generated cosine function. The resultant signal must be converted back to analog through the D/A converter. You can use the design given in the Tutorial [1] as a template. Place SignalTap II nodes at the output of the AM modulator and at the output of the cosine function to acquire the modulated and carrier signals, respectively (see Figure 1, Tutorial [1]). To implement the cosine function use Counter, ROM EAB and Pattern blocks from the DSPBuilder library, following the same approach given in [SineWave_Generator, 6] to design the look-up table approach. The ROM EAB block points to the hex file containing the points of the desired cosine function. The student must determine the values and required number of points for the cosine function, and implement the hex file. Follow the next specifications: Look-up table cosine function: Precision: 16 bits Cosine frequency: 600kHz Sample frequency: 80MHz

Max. number of points in the look-up table:

20

NOTE: it must be chosen the optimal number of points that minimizes quantization errors and maximizes the approximation to the required cosine frequency. Once, the points have been determined, implement the hex file. You can use Quartus II to do so. However, it is necessary that the points have the appropriate format. Hex files built by using Quartus II require numbers in unsigned decimal format. Thus, first convert the points to integer numbers by using the next Matlab command: values = round(x*2^Var-1); Var must contain the necessary value to have the bitlength of the points at 16 bits maximum, as required from the specifications. Then, convert values to unsigned fixed-point, as follows: q = quantizer('fixed',[16 0]); LUT = num2hex(q,values); hex2dec(LUT) These commands first create a quantizer for fixed-point numbers, fixing the number of bits at 16. Then, the values are converted to hexadecimal, and finally to the required unsigned decimal format. Afterwards, you can create the hex file in Quartus II with the obtained points. Open Quartus II, File > New and select Other Files in the pop-up window. Select Hexadecimal (Intel-format) File from the list, and click OK. A new window opens and asks for number of words and word size. Type 16 in the Word size field (following the look-up table specifications), and type the determined number of points from your previous analysis in the Number of words field. A table is created. Now fill the table with the point values for the cosine function. Save the file in the same directory where your Simulink design is located, and close Quartus II. Finally, specify the recently created hex file in the ROM EAB Block in your design in Simulink. Double click in the ROM EAB icon, and fill the Input Hex File field with the name of the hex file. Simulate your circuit in Simulink to modulate different sinusoidal signals up to 5MHz, observing the modulation behavior. What happens if the input signal frequency is closed to the carrier frequency?

The second part of the project involves the implementation of the cosine function but this time using the NCO IP core. Add to your AM circuit an additional cosine function. This new cosine function must be implemented using the NCO Altera IP core. From the Megacore Functions in the Altera DSPBuilder library, drag and place into your design the nco_v6_1 block. Double click the block to visualize the NCO Compiler v6.1. A menu with several options is available. If you click on Documentation, a pop-up window will appear with information concerning to the IP core. The student is encouraged to review the NCO User Guide v6.1. To parameterize the IP core, click on the Step1: Parameterize button in the NCO Compiler window. The student will select the required options to achieve the next specifications: Architecture: Accumulator precision: Angular precision: Cosine magnitude: Cosine frequency: Sampling frequency: multiplier-based using the multipliers embedded in the FPGA. 32 bits 13 bits 16 bits 600kHz 80MHz

Apply Phase Dithering to have a minimum attenuation of 90dB. What is the required dither level to achieve so? How many FPGA resources are estimated to be consumed by the NCO? Once parameterized, click on Finish, and click the Step2: Generate button in the NCO Compiler to compile and generate the IP core. Once done, the NCO block updates automatically, and is ready to interconnect to your circuit. Place a SignalTap II node at the output of the NCO to acquire the carrier signal during hardware tests later. Simulate your circuit in Simulink using the NCO as cosine generator to modulate different sinusoidal signals up to 5MHz, observing the modulation behavior. You final design must permit the user to select in real-time which cosine generator is going to use at a time: the look-up table based or the NCO-based method. To do so, use one of the push-buttons provided onboard. Download your design to the Stratix EP1S25 DSP development board and test it by using a signal generator and oscilloscope. Observe the effect of the modulation

with sine waves from 20kHz to 5MHz. What range of frequencies works appropriately with the AM circuit? NOTE: because of the IP core, the Signal Compiler will call the Quartus II Programmer during programming. The next message will appear, specifying that once the programmer is disconnected the FPGA will be erased:

Click OK, and then program the device through the next screen:

Check the box below the column Program/Configure, and click the Start button on the left to download the program to the FPGA. The next window will appear:

Your program will run onboard until you click on Cancel and close the Quartus II Programmer window.

While the program is running onboard, capture and analyze the data using SignalTap II Analysis. Also, using the data acquired through SignalTap II, show the frequency response using fft command for several input signals in the range from 20kHz to 5MHz. NOTE: you can use similar commands to those given in the Tutorial [1], Importing the data acquired from the board in Matlab workspace, step2. What differences can be found between the approach using NCO with multipliers and the look-up table? Make a list with at least 3 reasons to justify why one of the approaches is superior to the other in your design.

V. Submission You must submit: The Simulink model (.mdl) developed using DSP Builder blocks with two approaches to implement the cosine function: hard-coded look-up table and multiplier-based NCO. A report describing the general procedure to accomplish the project requirements, and answering questions regarding modulation techniques. The report must contain graphs showing the modulated and carrier signals, and frequency response using fft command for different inputs. VI. References [1] Tutorial: A/D and D/A Conversion on Altera Stratix EP1S25 Development Board using Simulink and DSP Builder. [2] DSP Builder User Guide, ver. 5.1.0, c:\altera\61\DSPBuilder\Doc\ug_dspbuilder.pdf Altera, 2005. Local copy at:

[3] Stratix EP1S25 DSP Development Board Data Sheet, ver. 1.6, Altera, 2004. Available online at: http://www.altera.com/literature/ds/ds_stratix_dsp-board-starter.pdf or local copy at: c:\altera\61\kits\stratix_dsp_kit-v1.3.0\Docs\ds_stratix_dsp_bd.pdf [4] DSP Development Kit Stratix & Stratix Professional Edition (Getting Started User Guide), ver. 1.3.0 rev. 1, Altera, 2004. Available online at: http://www.altera.com/literature/ug/ug_stratix_dsp_kit.pdf or local copy at: c:\altera\61\kits\stratix_dsp_kit-v1.3.0\Docs\ug_stratix_dsp_kit.pdf [5] IP MegaStore, Altera. Available online at: http://www.altera.com/products/ip/ipmindex.html

[6] Reference Design, Altera, 2004. Local copy at: C:\altera\61\DSPBuilder\DesignExamples\Demos\Filters\FilteringLab\Stap\stfilteringlab. mdl

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- MBA Study On Organisational Culture and Its Impact On Employees Behaviour - 237652089Documento64 pagineMBA Study On Organisational Culture and Its Impact On Employees Behaviour - 237652089sunitha kada55% (20)

- CpE194 Lab Experiment # 1 - MTS-88 FamiliarizationDocumento4 pagineCpE194 Lab Experiment # 1 - MTS-88 FamiliarizationLouieMurioNessuna valutazione finora

- Fuzzy Node Localization in Wireless Sensor Network: Suman Bhowmik Rajib Kar Chandan GiriDocumento5 pagineFuzzy Node Localization in Wireless Sensor Network: Suman Bhowmik Rajib Kar Chandan GiriassnadNessuna valutazione finora

- PH and PH MeterDocumento9 paginePH and PH MeterassnadNessuna valutazione finora

- Azure Intel EDGEDocumento9 pagineAzure Intel EDGEassnadNessuna valutazione finora

- IJMGE Volume 50 Issue 2 Pages 231-238 2Documento8 pagineIJMGE Volume 50 Issue 2 Pages 231-238 2assnadNessuna valutazione finora

- IEEE Career Brochure 3.1.07 PDFDocumento2 pagineIEEE Career Brochure 3.1.07 PDFassnadNessuna valutazione finora

- Bee Colony Optimization For ClusteringDocumento1 paginaBee Colony Optimization For ClusteringassnadNessuna valutazione finora

- Training PLC's 200Documento84 pagineTraining PLC's 200George Makdessi EliasNessuna valutazione finora

- AS1xxx - Stepper Motors: New Automation TechnologyDocumento2 pagineAS1xxx - Stepper Motors: New Automation TechnologyassnadNessuna valutazione finora

- Modbus Poll Prime Setup GuideDocumento5 pagineModbus Poll Prime Setup GuideassnadNessuna valutazione finora

- Som Kohonen FuzzyDocumento19 pagineSom Kohonen FuzzyassnadNessuna valutazione finora

- Nicole Kidman's History of Success in 40 CharactersDocumento2 pagineNicole Kidman's History of Success in 40 CharactersassnadNessuna valutazione finora

- Transportation ProblemDocumento21 pagineTransportation ProblemPak NgahNessuna valutazione finora

- Introduction To Instrumentation PDFDocumento9 pagineIntroduction To Instrumentation PDFWalaa GabrNessuna valutazione finora

- Art of PresentationDocumento30 pagineArt of PresentationRinji HiroahNessuna valutazione finora

- 2014 IEEE IV Symposium Call for PapersDocumento1 pagina2014 IEEE IV Symposium Call for PapersassnadNessuna valutazione finora

- Exam (2000) AnswersDocumento2 pagineExam (2000) AnswersassnadNessuna valutazione finora

- Optimization Model For Elevator SystemDocumento5 pagineOptimization Model For Elevator SystemassnadNessuna valutazione finora

- ENGG 3490 Mechatronics Systems Design: Lab 3: Closed Loop ControlDocumento11 pagineENGG 3490 Mechatronics Systems Design: Lab 3: Closed Loop ControlassnadNessuna valutazione finora

- Backup 2Documento59 pagineBackup 2Fabiola Tineo GamarraNessuna valutazione finora

- 0418 w08 QP 1Documento17 pagine0418 w08 QP 1pmvarshaNessuna valutazione finora

- MGMT 410 Book ReportDocumento1 paginaMGMT 410 Book ReportLester F BoernerNessuna valutazione finora

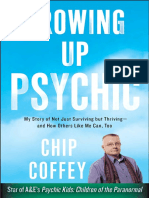

- Growing Up Psychic by Chip Coffey - ExcerptDocumento48 pagineGrowing Up Psychic by Chip Coffey - ExcerptCrown Publishing Group100% (1)

- RBI and Maintenance For RCC Structure SeminarDocumento4 pagineRBI and Maintenance For RCC Structure SeminarcoxshulerNessuna valutazione finora

- User Manual: Swift S3Documento97 pagineUser Manual: Swift S3smnguyenNessuna valutazione finora

- DPCA OHE Notice of Appeal 4-11-2018 FinalDocumento22 pagineDPCA OHE Notice of Appeal 4-11-2018 Finalbranax2000Nessuna valutazione finora

- 07CRMDocumento81 pagine07CRMsangramlifeNessuna valutazione finora

- Tutor Marked Assignment (TMA) SR Secondary 2018 19Documento98 pagineTutor Marked Assignment (TMA) SR Secondary 2018 19kanna2750% (1)

- Users GuideDocumento34 pagineUsers GuideZaratustra NietzcheNessuna valutazione finora

- Worksheet 9-2 - Math 7Documento2 pagineWorksheet 9-2 - Math 7bfbrfvlfrerNessuna valutazione finora

- Navier-Stokes EquationsDocumento395 pagineNavier-Stokes EquationsBouhadjar Meguenni100% (7)

- Pedestrian Safety in Road TrafficDocumento9 paginePedestrian Safety in Road TrafficMaxamed YusufNessuna valutazione finora

- Failure Reporting, Analysis, and Corrective Action SystemDocumento46 pagineFailure Reporting, Analysis, and Corrective Action Systemjwpaprk1Nessuna valutazione finora

- JHS SLM 1 Q2 Math Grade 10 32pagesDocumento32 pagineJHS SLM 1 Q2 Math Grade 10 32pagesAngel Naiza JimenezNessuna valutazione finora

- The Effect of Reward Practices on Employee Performance in Ethio TelecomDocumento29 pagineThe Effect of Reward Practices on Employee Performance in Ethio TelecomZakki Hersi AbdiNessuna valutazione finora

- English Class Language DevicesDocumento56 pagineEnglish Class Language DevicesKAREN GREGANDANessuna valutazione finora

- Cellulose StructureDocumento9 pagineCellulose Structuremanoj_rkl_07Nessuna valutazione finora

- Nektar Impact LX25 (En)Documento32 pagineNektar Impact LX25 (En)Camila Gonzalez PiatNessuna valutazione finora

- LuberigthDocumento24 pagineLuberigthEnrique BarriosNessuna valutazione finora

- C code snippets with answersDocumento14 pagineC code snippets with answersqwerty6327Nessuna valutazione finora

- PLC 2 Ladder DiagramDocumento53 paginePLC 2 Ladder DiagramAnkur GuptaNessuna valutazione finora

- Studies On Diffusion Approach of MN Ions Onto Granular Activated CarbonDocumento7 pagineStudies On Diffusion Approach of MN Ions Onto Granular Activated CarbonInternational Journal of Application or Innovation in Engineering & ManagementNessuna valutazione finora

- C1 Reading 1Documento2 pagineC1 Reading 1Alejandros BrosNessuna valutazione finora

- The Stolen Bacillus - HG WellsDocumento6 pagineThe Stolen Bacillus - HG Wells1mad.cheshire.cat1Nessuna valutazione finora

- Companies DatabaseDocumento2 pagineCompanies DatabaseNIRAJ KUMARNessuna valutazione finora

- A Comparative Marketing Study of LG ElectronicsDocumento131 pagineA Comparative Marketing Study of LG ElectronicsAshish JhaNessuna valutazione finora