Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Interrupts

Caricato da

browseanddownloadDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Interrupts

Caricato da

browseanddownloadCopyright:

Formati disponibili

Interrupts

Interrupt driven IO Processors are notified when an IO device required attention from processors An IO interrupt is asynchronous w.r.t the instruction execution. That means it is not associated with any instruction and does not prevent instruction execution. The control unit of a processor only checks for a pending IO interrupt at the start of a new instruction To communicate the origin and cause of the interrupt to the processor, a system can use either vectored interrupts or exception-cause register. Sequence of operations on the reception of an interrupt by the processor Device raises an interrupt using the interrupt-request-line(INTR). Complete the execution of the current instruction, i. Take steps to ensure that only one interrupt is processed for the whole duration of the interrupt line being active. Contents of PC which point to i + 1 are saved in a special register as a part of saving-state Load the PC with the address of the interrupt service routine so that the ISR runs The interrupt from the IO device is acknowledged by the processor to the device explicitly either by asserting a line(interrupt-acknowledge - INTA) on the bus or implicitly by a instruction in the ISR which accesses a status or data register in the device. The ISR is executed. The ISR contains a return-from-interrupt routine instruction which loads the address of i + 1 from the special register back to PC(among other things), causing the execution to resume at instruction i + 1. The state of the processor is restored before the resumption of instruction at i+1 of course Interrupt latency Time required by the processor to start the ISR after the delivery of an interrupt. What is the interrupt-line a part of? It is one of the control lines of the bus. Choices available w. r. t. saving the state of the processor before the start of an ISR The processor typically saves just the PC and processors-status-register to keep the interrupt latency to a minimum. Program instructions at the start of the ISR should typically save other stuff and restore stuff at the end of the ISR. The processor restores the PC and processor-status-registers as a part of the return-from-interrupt instruction. The processor saves everything. State is restored as a p[art of the return-from-interrupt instruction. There are multiple register sets eliminating(to an extent) the need to save state. How is it ensured that an active interrupt line does not lead to successive interruptions Have the processor hardware ignore the interrupt-request line until the execution of the first instruction of the ISR. The ISR is coded such that a disable-interrupt is the first instruction of the ISR and a enable-interrupt is the last-but-one instruction of the ISR(the last one being return-from-interrupt). Have the processor disable the interrupts by executing a disable-interrupt as a part of the state-save before entering the ISR and a enable-interrupt as a part of the return-frominterrupt. This is suitable for a uniprocessor which has a single interrupt line Have the interrupt-handling circuitry of the processor respond only to the leading edge of the signal(edge-triggered). Thus a interrupt line being active will trigger only a single

interrupt. How is the origin of an interrupt discovered by the processor when devices share a common interrupt-line with the processor? Polling When a interrupt is received the processor polls all devices connected to that line and inspects to see whose IRQ(Interrupt request) bit is set in their status registers is set Vectored interrupts Devices send a code(usually on the data bus) giving the offset of the ISR to be run(There is a fixed place in memory where the ISR table contains ISR's for all devices connected is kept). The processor thus places into the PC the address of the start of the ISR(known base address + offset provided). Further flexibility is obtained by placing a jump instruction at that location which takes the execution to the actual ISR. What happens if a device raises a vectored interrupt and finds that the interrupts are disabled? It must, within reasonable limits, try again. This works for most simple devices as the delay caused is small, until the completion of execution of the ISR. An example where a delay in service, like the above is unacceptable A timer sends regular interrupts to the processor using which the system time is maintained. Need for nested interrupts and hence priority levels like above Handling of devices like timers who cannot wait or afford to try again Organization of devices w.r.t. buses in vectored interrupt scheme Multiple interrupt lines(parallel priority interrupt) This is implemented easily by using a separate interrupt request and interruptacknowledge line for each device. The processor accepts interrupts according to the multiple-priority and nested priority arbitration logic in its interrupt controller. Single interrupt line The INTR line is common to all devices INTA is attached in a daisy chain fashion from the processor to all devices such that it propagates serially through all devices. When a device/es want to interrupt it activates the INTR The processor responds by activating the INTA line. This signal propagates from device1 to device2 and so on. The device which INTR'ed sends the interrupt vector. This scheme requires lesser wires than the before. Mechanisms for controlling interrupts At the device end there is an interrupt enable bit which can be set/reset by the processor At the processor end either an interrupt enable bit in the PS register or a priority structure determines whether a given interrupt will be accepted. How does an interrupt get converted to a exception code in the cause register of the coprocessor in mips? How is the device causing the interrupt recognized? From a single ISR when there is no interrupt vector?

Structure of interrupt vector table when they are used.

Potrebbero piacerti anche

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- LinkedIn - Staff Generic SI TPS - One HourDocumento2 pagineLinkedIn - Staff Generic SI TPS - One HourbrowseanddownloadNessuna valutazione finora

- Scaling Memcache at FacebookDocumento14 pagineScaling Memcache at FacebookbrowseanddownloadNessuna valutazione finora

- 0 1 KnapsackDocumento2 pagine0 1 KnapsackbrowseanddownloadNessuna valutazione finora

- TypewritingDocumento84 pagineTypewritingbrowseanddownloadNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Assembly MnemonicsDocumento3 pagineAssembly MnemonicsDonald WorthumNessuna valutazione finora

- Mondorescue Howto PDFDocumento53 pagineMondorescue Howto PDFTitus Kernel MaestriaNessuna valutazione finora

- Service Manual RCF Art 500 ADocumento3 pagineService Manual RCF Art 500 AFederico Torre0% (1)

- Rate Analysis For Pile E700194.648, N1927757.887 Datum Level +5.899Documento5 pagineRate Analysis For Pile E700194.648, N1927757.887 Datum Level +5.899NaveenNessuna valutazione finora

- Jasmine MotifDocumento25 pagineJasmine MotifHunar Lamba100% (2)

- ProE Manual Publisher ReadmeDocumento2 pagineProE Manual Publisher ReadmeSan RockNessuna valutazione finora

- SAP HCI OverviewDocumento6 pagineSAP HCI OverviewSunil SharmaNessuna valutazione finora

- 111.expression - of - Interest - of - Architect - tmbd-3rd Phase FinalDocumento4 pagine111.expression - of - Interest - of - Architect - tmbd-3rd Phase FinalSyed ZamanNessuna valutazione finora

- INSTALL AND SERVICE 21ST CENTURY LIGHTSDocumento84 pagineINSTALL AND SERVICE 21ST CENTURY LIGHTSAnonymous D9bqxF100% (1)

- Explore the City Centre in Salt Lake, KolkataDocumento7 pagineExplore the City Centre in Salt Lake, Kolkataaishwarya raniNessuna valutazione finora

- Gaggenau DF 291-760Documento1 paginaGaggenau DF 291-760PurcellMurrayNessuna valutazione finora

- 5ar01 History of Architecture - V - Baroque and Rococo Architecture, Revivals - NotesDocumento27 pagine5ar01 History of Architecture - V - Baroque and Rococo Architecture, Revivals - NotesSumukha .kNessuna valutazione finora

- Oracle Nosql Database,: 12.1.3.5, COMMUNITY EDITIONDocumento5 pagineOracle Nosql Database,: 12.1.3.5, COMMUNITY EDITIONCarlos Mario HerreraNessuna valutazione finora

- Zahvalnica Bla BlaDocumento2 pagineZahvalnica Bla BlaBiljanaJanjušević100% (1)

- Saudi Aramco Inspection Checklist: Compaction Testing SAIC-A-1005 31-Nov-2019 CivilDocumento2 pagineSaudi Aramco Inspection Checklist: Compaction Testing SAIC-A-1005 31-Nov-2019 CivilyazNessuna valutazione finora

- CCBM 2 AssignmentDocumento2 pagineCCBM 2 Assignmentsaarthak srivastavaNessuna valutazione finora

- ATM System Case StudyDocumento14 pagineATM System Case StudySmita B Kumar GuptaNessuna valutazione finora

- Urban MorphologyDocumento7 pagineUrban MorphologyPavithra Supramanian100% (1)

- PHT Pipe Clamp Catalog2012ADocumento10 paginePHT Pipe Clamp Catalog2012ADifa LiuNessuna valutazione finora

- React NativeDocumento100 pagineReact NativeMohammed Zeeshan0% (2)

- Mastertile 30Documento3 pagineMastertile 30Vajira KumaraNessuna valutazione finora

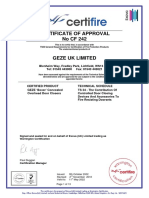

- Certificate of Approval No CF 242Documento13 pagineCertificate of Approval No CF 242Florin RazvanNessuna valutazione finora

- Advproxy - Advanced Web Proxy For SmoothWall Express 2.0 (Marco Sondermann, p76) PDFDocumento76 pagineAdvproxy - Advanced Web Proxy For SmoothWall Express 2.0 (Marco Sondermann, p76) PDFjayan_Sikarwar100% (1)

- E-Learning: Project ReportDocumento36 pagineE-Learning: Project Reportprateek_maheshwar_11Nessuna valutazione finora

- Nilangsu MitraDocumento5 pagineNilangsu MitraNilangsu MitraNessuna valutazione finora

- Suikoden II Perfect Game Guide v2.1 - Neoseeker WalkthroughsDocumento27 pagineSuikoden II Perfect Game Guide v2.1 - Neoseeker WalkthroughsSMTNessuna valutazione finora

- Basics Configuration of PBX Nortel Meridain 81cDocumento26 pagineBasics Configuration of PBX Nortel Meridain 81cGil HaleNessuna valutazione finora

- The Sloop's Log Spring 2011Documento20 pagineThe Sloop's Log Spring 2011Chebeague Island Historical SocietyNessuna valutazione finora

- Lecture 1 Theory QS Measurement BQ SMMDocumento40 pagineLecture 1 Theory QS Measurement BQ SMMAtef RagabNessuna valutazione finora

- Graphic Era University: "Cloudsim ToolkitDocumento11 pagineGraphic Era University: "Cloudsim ToolkitnitinNessuna valutazione finora