Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

The 8085 Instruction Set

Caricato da

Sindu RangaswamyDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

The 8085 Instruction Set

Caricato da

Sindu RangaswamyCopyright:

Formati disponibili

The 8085 Instruction Set

As I promised, in an earlier lesson, I am going to go through an in-depth explaination of ALL the 8085 instructions.

---------------------------------------------------------------| | | | | Intel | | | | 88888 000 88888 5555555 A | | 8 8 0 0 8 8 5 A A | | 8 8 0 0 0 8 8 5 A A | | 88888 0 0 0 88888 555555 AAAAAAA | | 8 8 0 0 0 8 8 5 A A | | 8 8 0 0 8 8 5 A A | | 88888 000 88888 555555 A A | | | | 8085A MICROPROCESSOR Instruction Set Summary | | | | | | | | | | | | _________ _________ | | _| \__/ |_ | | --> X1 |_|1 40|_| Vcc (+5V) | | _| |_ | | --> X2 |_|2 39|_| HOLD <-| | _| |_ | | <-- RESET OUT |_|3 38|_| HLDA --> | | _| |_ | | <-- SOD |_|4 37|_| CLK (OUT) --> | | _| |_ ________ | | --> SID |_|5 36|_| RESET IN <-| | _| |_ | | --> TRAP |_|6 35|_| READY <-| | _| |_ _ | | --> RST 7.5 |_|7 34|_| IO/M --> | | _| |_ | | --> RST 6.5 |_|8 33|_| S1 --> | | _| |_ __ | | --> RST 5.5 |_|9 32|_| RD --> | | _| |_ __ | | --> INTR |_|10 8085A 31|_| WR --> | | ____ _| |_ | | <-- INTA |_|11 30|_| ALE --> | | _| |_ | | <--> AD0 |_|12 29|_| S0 --> | | _| |_ | | <--> AD1 |_|13 28|_| A15 --> | | _| |_ | | <--> AD2 |_|14 27|_| A14 --> | | _| |_ |

| | | | | | | | | | | | | | | |

<--> AD3 |_|15 26|_| _| |_ <--> AD4 |_|16 25|_| _| |_ <--> AD5 |_|17 24|_| _| |_ <--> AD6 |_|18 23|_| _| |_ <--> AD7 |_|19 22|_| _| |_ (Gnd) Vss |_|20 21|_| |______________________|

| | A12 --> | | A11 --> | | A10 --> | | A9 --> | | A8 --> | | | | | Copyright (C) J.P.Bowen 1985|

A13 -->

Instructions can be categorized according to their method of addressing the hardware registers and/or memory. Implied Addressing: The addressing mode of certain instructions is implied by the instructions function. For example, the STC (set carry flag) instruction deals only with the carry flag, the DAA (decimal adjust accumulator) instruction deals with the accumulator. Register Addressing: Quite a large set of instructions call for register addressing. With these instructions, you must specify one of the registers A through E, H or L as well as the operation code. With these instructions, the accumulator is implied as a second operand. For example, the instruction CMP E may be interpreted as 'compare the contents of the E register with the contents of the accumulator. Most of the instructions that use register addressing deal with 8-bit values. However, a few of these instructions deal with 16-bit register pairs. For example, the PCHL instruction exchanges the contents of the program counter with the contents of the H and L registers. Immediate Addressing: Instructions that use immediate addressing have data assembled as a part of the instruction itself. For example, the instruction CPI 'C' may be interpreted as compare the contents of the accumulator with the letter C. When assembled, this instruction has the hexadecimal value FE43. Hexadecimal 43 is the internal representation for the

letter C. When this instruction is executed, the processor fetches the first instruction byte and determines that it must fetch one more byte. The processor fetches the next byte into one of its internal registers and then performs the compare operation. Notice that the names of the immediate instructions indicate that they use immediate data. Thus, the name of an add instruction is ADD; the name of an add immediate instruction is ADI. All but two of the immediate instructions uses the accumulator as an implied operand, as in the CPI instruction shown previously. The MVI (move immediate) instruction can move its immediate data to any of the working registers including the accumulator or to memory. Thus, the instruction MVI D, OFFH moves the hexadecimal value FF to the D register. The LXI instruction (load register pair immediate) is even more unusual in that its immediate data is a 16-bit value. This instruction is commonly used to load addresses into a register pair. As mentioned previously, your program must initialize the stack pointer; LXI is the instruction most commonly used for this purpose. For example, the instruction LXI SP,3OFFH loads the stack pointer with the hexadecimal value 30FF. Direct Addressing: Jump instructions include a 16-bit address as part of the instruction. For example, the instruction JMP 1000H causes a jump to the hexadecimal address 1000 by replacing the current contents of the program counter with the new value 1000H. Instructions that include a direct address require three bytes of storage: one for the instruction code, and two for the 16-bit address Register Indirect Addressing: Register indirect instructions reference memory via a register pair. Thus, the instruction MOV M,C moves the contents of the C register into the memory address stored in the H and L register pair. The instruction LDAX B loads the accumulator with the byte of data specified by the address in the B and C register pair.

Combined Addressing Modes: Some instructions use a combination of addressing modes. A CALL instruction, for example, combines direct addressing and register indirect addressing. The direct address in a CALL instruction specifies the address of the desired subroutine; the register indirect address is the stack pointer. The CALL instruction pushes the current contents of the program counter into the memory location specified by the stack pointer. Timing Effects of Addressing Modes: Addressing modes affect both the amount of time required for executing an instruction and the amount of memory required for its storage. For example, instructions that use implied or register addressing, execute very quickly since they deal directly with the processors hardware or with data already present in hardware registers. Most important, however is that the entire instruction can be fetched with a single memory access. The number of memory accesses required is the single greatest factor in determining execution timing. More memory accesses therefore require more execution time. A CALL instruction for example, requires five memory accesses: three to access the entire instruction and two more to push the contents of the program counter onto the stack. The processor can access memory once during each processor cycle. Each cycle comprises a variable number of states. (See below and the appendix of USING THE SDK-85 MICROPROCESSOR TRAINER). The length of a state depends on the clock frequency specified for your system, and may range from 480 nanoseconds to 2 microseconds. Thus, the timing for a four state instruction may range from 1.920 microseconds through 8 microseconds. (The 8085 have a maximum clock frequency of 5 MHz and therefore a minimum state length of 200 nanoseconds.) Instruction Naming Conventions: The mnemonics assigned to the instructions are designed to indicate the function of the instruction. The instructions fall into the following functional categories: Data Transfer Croup: The data transfer instructions move data between registers or between memory and registers.

MOV MVI LDA STA LHLD SHLD

Move Move Immediate Load Accumulator Directly from Memory Store Accumulator Directly in Memory Load H & L Registers Directly from Memory Store H & L Registers Directly in Memory

An 'X' in the name of a data transfer instruction implies that it deals with a register pair (16-bits); LXI LDAX Pair STAX XCHG XTHL Load Register Pair with Immediate data Load Accumulator from Address in Register Store Accumulator in Address in Register Pair Exchange H & L with D & E Exchange Top of Stack with H & L

Arithmetic Group: The arithmetic instructions add, subtract, increment, or decrement data in registers or memory. ADD ADI ADC ACI SUB SUI SBB (Carry) Flag SBI INR DCR INX DCX DAD Add to Accumulator Add Immediate Data to Accumulator Add to Accumulator Using Carry Flag Add Immediate data to Accumulator Using Carry Subtract from Accumulator Subtract Immediate Data from Accumulator Subtract from Accumulator Using Borrow Subtract Immediate from Accumulator Using Borrow (Carry) Flag Increment Specified Byte by One Decrement Specified Byte by One Increment Register Pair by One Decrement Register Pair by One Double Register Add; Add Content of Register Pair to H & L Register Pair

Logical Group: This group performs logical (Boolean) operations on data in registers and memory and on condition flags. The logical AND, OR, and Exclusive OR instructions enable you to set specific bits in the accumulator ON or OFF. ANA Logical AND with Accumulator

ANI Data ORA OR Data XRA XRI

Logical AND with Accumulator Using Immediate Logical OR with Accumulator Logical OR with Accumulator Using Immediate Exclusive Logical OR with Accumulator Exclusive OR Using Immediate Data

The Compare instructions compare the content of an 8-bit value with the contents of the accumulator; CMP CPI Compare Compare Using Immediate Data

The rotate instructions shift the contents of the accumulator one bit position to the left or right: RLC RRC RAL RAR Rotate Rotate Rotate Rotate Accumulator Left Accumulator Right Left Through Carry Right Through Carry

Complement and carry flag instructions: CMA CMC STC Complement Accumulator Complement Carry Flag Set Carry Flag

Branch Group: The branching instructions alter normal sequential program flow, either unconditionally or conditionally. The unconditional branching instructions are as follows: JMP CALL RET Jump Call Return

Conditional branching instructions examine the status of one of four condition flags to determine whether the specified branch is to be executed. The conditions that may be specified are as follows: NZ Z NC C PO Not Zero (Z = 0) Zero (Z = 1) No Carry (C = 0) Carry (C = 1) Parity Odd (P = 0)

PE P M

Parity Even (P Plus (S = 0) Minus (S = 1)

= 1)

Thus, the conditional branching instructions are specified as follows: Jumps C INC JZ JNZ JP JM JPE JP0 Calls CC CNC CZ CNZ CP CM CPE CPO Returns RC RNC RZ RNZ RP RM RPE RPO (Carry) (No Carry) (Zero) (Not Zero) (Plus) (Minus) (Parity Even) (Parity Odd)

Two other instructions can affect a branch by replacing the contents or the program counter: PCHL RST Move H & L to Program Counter Special Restart Instruction Used with Interrupts

Stack I/O, and Machine Control Instructions: The following instructions affect the Stack and/or Stack Pointer: PUSH POP XTHL SPHL Push Two bytes of Data onto the Stack Pop Two Bytes of Data off the Stack Exchange Top of Stack with H & L Move content of H & L to Stack Pointer

The I/0 instructions are as follows: IN OUT Initiate Input Operation Initiate Output Operation

The Machine Control instructions are as follows: EI Enable Interrupt System DI Disable Interrupt System HLT Halt NOP No Operation

---------------------------------------------------------------|Mnemonic |Op|SZAPC|~s|Description |Notes | |---------+--+-----+--+--------------------------+-------------| |ACI n |CE|*****| 7|Add with Carry Immediate |A=A+n+CY |

|ADC r |ADC M |ADD r |ADD M |ADI n |ANA r |ANA M |ANI n |CALL a |CC a |CM a |CMA |CMC |CMP r |CMP M |CNC a |CNZ a |CP a |CPE a |CPI n |CPO a |CZ a |DAA |DAD B |DAD D |DAD H |DAD SP |DCR r |DCR M |DCX B |DCX D |DCX H |DCX SP |DI |EI |HLT |IN p |INR r |INR M |INX B |INX D |INX H |INX SP |JMP a |JC a |JM a |JNC a |JNZ a |JP a |JPE a |JPO a |JZ a |LDA a |LDAX B |LDAX D |LHLD a |LXI B,nn

|8F|*****| 4|Add with Carry |A=A+r+CY(21X)| |8E|*****| 7|Add with Carry to Memory |A=A+[HL]+CY | |87|*****| 4|Add |A=A+r (20X)| |86|*****| 7|Add to Memory |A=A+[HL] | |C6|*****| 7|Add Immediate |A=A+n | |A7|****0| 4|AND Accumulator |A=A&r (24X)| |A6|****0| 7|AND Accumulator and Memory|A=A&[HL] | |E6|**0*0| 7|AND Immediate |A=A&n | |CD|-----|18|Call unconditional |-[SP]=PC,PC=a| |DC|-----| 9|Call on Carry |If CY=1(18~s)| |FC|-----| 9|Call on Minus |If S=1 (18~s)| |2F|-----| 4|Complement Accumulator |A=~A | |3F|----*| 4|Complement Carry |CY=~CY | |BF|*****| 4|Compare |A-r (27X)| |BF|*****| 7|Compare with Memory |A-[HL] | |D4|-----| 9|Call on No Carry |If CY=0(18~s)| |C4|-----| 9|Call on No Zero |If Z=0 (18~s)| |F4|-----| 9|Call on Plus |If S=0 (18~s)| |EC|-----| 9|Call on Parity Even |If P=1 (18~s)| |FE|*****| 7|Compare Immediate |A-n | |E4|-----| 9|Call on Parity Odd |If P=0 (18~s)| |CC|-----| 9|Call on Zero |If Z=1 (18~s)| |27|*****| 4|Decimal Adjust Accumulator|A=BCD format | |09|----*|10|Double Add BC to HL |HL=HL+BC | |19|----*|10|Double Add DE to HL |HL=HL+DE | |29|----*|10|Double Add HL to HL |HL=HL+HL | |39|----*|10|Double Add SP to HL |HL=HL+SP | |3D|****-| 4|Decrement |r=r-1 (0X5)| |35|****-|10|Decrement Memory |[HL]=[HL]-1 | |0B|-----| 6|Decrement BC |BC=BC-1 | |1B|-----| 6|Decrement DE |DE=DE-1 | |2B|-----| 6|Decrement HL |HL=HL-1 | |3B|-----| 6|Decrement Stack Pointer |SP=SP-1 | |F3|-----| 4|Disable Interrupts | | |FB|-----| 4|Enable Interrupts | | |76|-----| 5|Halt | | |DB|-----|10|Input |A=[p] | |3C|****-| 4|Increment |r=r+1 (0X4)| |3C|****-|10|Increment Memory |[HL]=[HL]+1 | |03|-----| 6|Increment BC |BC=BC+1 | |13|-----| 6|Increment DE |DE=DE+1 | |23|-----| 6|Increment HL |HL=HL+1 | |33|-----| 6|Increment Stack Pointer |SP=SP+1 | |C3|-----| 7|Jump unconditional |PC=a | |DA|-----| 7|Jump on Carry |If CY=1(10~s)| |FA|-----| 7|Jump on Minus |If S=1 (10~s)| |D2|-----| 7|Jump on No Carry |If CY=0(10~s)| |C2|-----| 7|Jump on No Zero |If Z=0 (10~s)| |F2|-----| 7|Jump on Plus |If S=0 (10~s)| |EA|-----| 7|Jump on Parity Even |If P=1 (10~s)| |E2|-----| 7|Jump on Parity Odd |If P=0 (10~s)| |CA|-----| 7|Jump on Zero |If Z=1 (10~s)| |3A|-----|13|Load Accumulator direct |A=[a] | |0A|-----| 7|Load Accumulator indirect |A=[BC] | |1A|-----| 7|Load Accumulator indirect |A=[DE] | |2A|-----|16|Load HL Direct |HL=[a] | |01|-----|10|Load Immediate BC |BC=nn |

|LXI D,nn |11|-----|10|Load Immediate DE |DE=nn | |LXI H,nn |21|-----|10|Load Immediate HL |HL=nn | |LXI SP,nn|31|-----|10|Load Immediate Stack Ptr |SP=nn | |MOV r1,r2|7F|-----| 4|Move register to register |r1=r2 (1XX)| |MOV M,r |77|-----| 7|Move register to Memory |[HL]=r (16X)| |MOV r,M |7E|-----| 7|Move Memory to register |r=[HL] (1X6)| |MVI r,n |3E|-----| 7|Move Immediate |r=n (0X6)| |MVI M,n |36|-----|10|Move Immediate to Memory |[HL]=n | |NOP |00|-----| 4|No Operation | | |ORA r |B7|**0*0| 4|Inclusive OR Accumulator |A=Avr (26X)| |ORA M |B6|**0*0| 7|Inclusive OR Accumulator |A=Av[HL] | |ORI n |F6|**0*0| 7|Inclusive OR Immediate |A=Avn | |OUT p |D3|-----|10|Output |[p]=A | |PCHL |E9|-----| 6|Jump HL indirect |PC=[HL] | |POP B |C1|-----|10|Pop BC |BC=[SP]+ | |POP D |D1|-----|10|Pop DE |DE=[SP]+ | |POP H |E1|-----|10|Pop HL |HL=[SP]+ | |POP PSW |F1|-----|10|Pop Processor Status Word |{PSW,A}=[SP]+| ------------------------------------------------------------------------------------------------------------------------------|Mnemonic |Op|SZAPC|~s|Description |Notes | |---------+--+-----+--+--------------------------+-------------| |PUSH B |C5|-----|12|Push BC |-[SP]=BC | |PUSH D |D5|-----|12|Push DE |-[SP]=DE | |PUSH H |E5|-----|12|Push HL |-[SP]=HL | |PUSH PSW |F5|-----|12|Push Processor Status Word|-[SP]={PSW,A}| |RAL |17|----*| 4|Rotate Accumulator Left |A={CY,A}<| |RAR |1F|----*| 4|Rotate Accumulator Righ |A=->{CY,A} | |RET |C9|-----|10|Return |PC=[SP]+ | |RC |D8|-----| 6|Return on Carry |If CY=1(12~s)| |RIM |20|-----| 4|Read Interrupt Mask |A=mask | |RM |F8|-----| 6|Return on Minus |If S=1 (12~s)| |RNC |D0|-----| 6|Return on No Carry |If CY=0(12~s)| |RNZ |C0|-----| 6|Return on No Zero |If Z=0 (12~s)| |RP |F0|-----| 6|Return on Plus |If S=0 (12~s)| |RPE |E8|-----| 6|Return on Parity Even |If P=1 (12~s)| |RPO |E0|-----| 6|Return on Parity Odd |If P=0 (12~s)| |RZ |C8|-----| 6|Return on Zero |If Z=1 (12~s)| |RLC |07|----*| 4|Rotate Left Circular |A=A<| |RRC |0F|----*| 4|Rotate Right Circular |A=->A | |RST z |C7|-----|12|Restart (3X7)|-[SP]=PC,PC=z| |SBB r |9F|*****| 4|Subtract with Borrow |A=A-r-CY | |SBB M |9E|*****| 7|Subtract with Borrow |A=A-[HL]-CY | |SBI n |DE|*****| 7|Subtract with Borrow Immed|A=A-n-CY | |SHLD a |22|-----|16|Store HL Direct |[a]=HL | |SIM |30|-----| 4|Set Interrupt Mask |mask=A | |SPHL |F9|-----| 6|Move HL to SP |SP=HL | |STA a |32|-----|13|Store Accumulator |[a]=A | |STAX B |02|-----| 7|Store Accumulator indirect|[BC]=A | |STAX D |12|-----| 7|Store Accumulator indirect|[DE]=A | |STC |37|----1| 4|Set Carry |CY=1 | |SUB r |97|*****| 4|Subtract |A=A-r (22X)| |SUB M |96|*****| 7|Subtract Memory |A=A-[HL] | |SUI n |D6|*****| 7|Subtract Immediate |A=A-n | |XCHG |EB|-----| 4|Exchange HL with DE |HL<->DE | |XRA r |AF|**0*0| 4|Exclusive OR Accumulator |A=Axr (25X)| |XRA M |AE|**0*0| 7|Exclusive OR Accumulator |A=Ax[HL] |

|XRI n |EE|**0*0| 7|Exclusive OR Immediate |A=Axn | |XTHL |E3|-----|16|Exchange stack Top with HL|[SP]<->HL | |------------+-----+--+----------------------------------------| | PSW |-*01 | |Flag unaffected/affected/reset/set | | S |S | |Sign (Bit 7) | | Z | Z | |Zero (Bit 6) | | AC | A | |Auxilary Carry (Bit 4) | | P | P | |Parity (Bit 2) | | CY | C| |Carry (Bit 0) | |---------------------+----------------------------------------| | a p |Direct addressing | | M z |Register indirect addressing | | n nn |Immediate addressing | | r |Register addressing | |---------------------+----------------------------------------| |DB n(,n) |Define Byte(s) | |DB 'string' |Define Byte ASCII character string | |DS nn |Define Storage Block | |DW nn(,nn) |Define Word(s) | |---------------------+----------------------------------------| | A B C D E H L |Registers (8-bit) | | BC DE HL |Register pairs (16-bit) | | PC |Program Counter register (16-bit) | | PSW |Processor Status Word (8-bit) | | SP |Stack Pointer register (16-bit) | |---------------------+----------------------------------------| | a nn |16-bit address/data (0 to 65535) | | n p |8-bit data/port (0 to 255) | | r |Register (X=B,C,D,E,H,L,M,A) | | z |Vector (X=0H,8H,10H,18H,20H,28H,30H,38H)| |---------------------+----------------------------------------| | + |Arithmetic addition/subtraction | | & ~ |Logical AND/NOT | | v x |Logical inclusive/exclusive OR | | <- -> |Rotate left/right | | <-> |Exchange | | [ ] |Indirect addressing | | [ ]+ -[ ] |Indirect address auto-inc/decrement | | { } |Combination operands | | ( X ) |Octal op code where X is a 3-bit code | | If ( ~s) |Number of cycles if condition true | ----------------------------------------------------------------

On to lesson 19

To front page. Still under construction.

The 8085 Microprocessor Instruction Set

Table of Contents Introduction Processor 8085 Registers Assembly Language Format Instruction Set Encyclopedia The Processor 8085 Electrical Pins and Pin Descriptions References.

Introduction The 8085 microprocessor is an eight bit general purpose processor. It is a conventional Von Neumann type computer design that uses binary numbers as information storage. A binary number consists only as ones and zero. A bit 1 is represented by about +5 volts at about 0.02 watt, and a binary zero is represented by a voltage of less than +0.8 volt. It was first made by Intel in 1977. Its main advantages are its small size, fast calculation speed, relatively low electrical power consumption, requires less hardware, has only about 256 instructions for easier assembler construction, and low cost. It has a 16 bit address bus which permits ffff16 bytes of main memory size of read only memory and random access memory electronic intergrated circuits accessed directly. The 8085 may have been used by the United States military. The circuit uses miniature electronic components called transistors (metal-oxide semiconductor), diodes and resistors to form logic gates. Logic gates can be combined to form electronic temporary memory circuits called registers in the 8085.

Processor 8085 Registers Table 2 shows the 8085 microprocessor internal registers that the programmer has access to. Registers are temporary memories that can be accessed with some of the instructions. each are 8 bits long and two are combined to form 16 bit binary numbers like registers B and C. Stack pointer register SP as low order byte in SPL and most significant byte in SPH. Value in SP points to current top of stack memory.

Table2: Microprocesor 8085 Registers 7 0 7 0 B D H SPH 15 A C E L SPL PCL 0

PCH (program counter) increment/decrement register

Assembly Language Format The 8085 instruction consists of a label label2, followed by the mnemonics, then the distination operand and the source operand if present on a single line like this: label2: MOV A,(HL) ; Code explanantions and comments. where label label2 to is made equivalent to the location of the first byte of the instruction by the assembler. The word "MOV" is the mnemonics, character "A" is the distination instruction operand in this case. The (HL) is the source instruction operand in this case and means that the contents of registers H,L points to a memory location. The characters to the right of character ";" to end of line "\n" are code explanations and are not compiled by the assembler. Mnemonics Reprentation Conventions r, r1, r2 One of the registers A, B, C, D, E ,H, L (, ) round brackets means register(s) in these contains a pointer value to a main memory location, DDD three bits in opcode representing destination register in table 4, SSS three bits in opcode representing source register in table 4, M a 16 bit pointer value to a main memory location, d8 data as a 1 byte operand immediately following the opcode, d16 data as a 2 byte operand immediately following the opcode, low order data byte first; low order byte d16l

of d16, most signifcant byte d16h of d16; word d16 is two bytes. rp Two bits in opcode representing the use a register pair in table 5; register pair instruction operand: BC, DE, HL or SP. PC 16 bit progam counter register, with PCL low order byte of PC and PCH the most significant byte of PC. SP 16 bit stack pointer register which points to start location of stack in main memeory, SPL is low order byte of SP, SPH is most signifcant byte of SP. port an eight bit number as port number that follows the opcode byte in main memory and is from address pins A0 through A7 used by "IN", or "OUT" instruction. . Tables 4 and 5 shows bits that needs be included in some opcodes depending on the register(s) used in instruction. For example if register B is used in instruction "MOV B,(HL)", its opcode will be: 01DDD110=01000110. Table 4: Register Bits DDD or SSS bits: 111 000 001 010 011 100 101 register names: A B C D E H L

Table 5: Register Pairs For Opcode rp bits: 00 01 10 11 register pairs (rh, rl): B, C D, E H, L S, P.

Intruction Set Encyclopedea Intruction set encyclopedea for each intruction below has instruction syntax (mnemonics) format, basic operation, code explanations and comments, operation function, machine code or opcode of corresponding instruction in binary format with optional immediate operands, addressign types, flags affected, other information and then perhaps an example instruction. The 8085 microprocessor has ff16 assembly instructions that have opcodes that are eight bits long. Some opcodes have an immediate byte or two immediately following it in main memory. Indirect addressing means that a value in one of the register pairs (b-c, d-e, h-l or sp) contains a value that points to a main memory location of a byte. Direct addressing means the immediate operands (2 bytes) following the opcode points to a location in main memory of a byte.

Data Transfer Mnemonics MOV r1,r2 (move value between registers). The content of source register r2 is moved or copied to destination register r1: r1 r2. Opcode: 11DDDSSS2 . Addressing type(s): register r; flags affected: none. Example: MOV A,B.

MOV r,M (move byte from main memory to a register). The byte contents of main memory location whose address is in index registers H and L is moved to register r: M= (HL). r (HL). 01DDD110. Addressing: register r, indirect M; flags affected: none. Example: MOV B,(HL).

MOV M,r (move byte from a register to a memory location) The contents of register r is moved or copied to the memory location whose address in in registers H, and L; register L contains to the lower byte of location M and H the most significant byte of M: (HL) r. 01110SSS. Example: MOV (HL),C.

MVI r,d8 (move immediate byte to register e) The content d8 of immediate operand byte of the instruction into register r: r d8. Opcode and operand: 00DDD1102, d816 . Example: MVI D,02h.

MVI M,d8 (move immediate byte to a memory location) The content d8 of immediate byte operand of the instruction is moved or copied the main memory whose address is in registers H and L. (HL) d8. 00110110, d8 Example: MOV (HL),03h.

LXI rp,d16 (load register pair rp with immediate word d16) Most significant byte d16h of data of d16 is moved to most significant register rh of register pair rp and low order byte d16l of d16 is moved to low order register rl of register pair rp: rh d16h, rl d16l. 00rp0001, d16l, d16h Example:LXI HL,025dh.

LDA A,(d16) (load accummulator A direct) The content of the memory location pointed to by immediate operand value

d16 is moved to register A. A (d16). 00111010, d16l, d16h. Example: LDA A,(0255h)

STA (d16) (Store from accummulator direct) The content of accumulator A is stored in main memory location whose address is d16 (immediate word). Low order byte is d16l. 00110010, d16l, d16h. STA (041ch)

LHL (d16) (load H and L register direct) The content of two adjacent memory locations whose starting address is immediate operand d16 is loaded into register paint H and L, with lower order byte in L and most signficant bye following is stored into register H. L (d16), H (d16+1). 00101010, d16l, d16h. LHL (02a7h)

SHLD (d16) (store H and L direct) Store H and L values into memory location beginning at location d16. Lower byte in L into main memory location d16, and most significant byte in H into location d16+1 (following L). (d16) L, (d16+1) H. 00100010. d16l, d16h. SHLD (030fh).

Arithmetic Mnemonics ADC r (add register r to A with carry) The content of register r and contents of current carry bit C are added to content of accmumulator A=An with results in acccumulator A=An+1 .ResetscarryflagtoC=1=Cn+1 bit if carry bit is present. Example value An+1=100011012. An+1 An+r+Cn, Cn+1.

10001SSS. ADC B.

ADC M (Add a memory location content with carry) The byte content of the memory location whose address is contained in register pair H and L and the current carry flag C bit are added to the accumulator A value with result in accumulator A. An+1 An+(HL)+Cn, Cn+1. Opcode: 10001110. Example: ADC (HL).

ACI d8 (add immediate operand with carry) The content of the second byte (immedate operand) d8 of instruction, the current carry bit Cn and contents of accumulator A are added. Results in accumulator A=An+1. An+1 An+d8+Cn, Cn+1. 11001110, d8. Example: ACI 04h.

Processor Input, Output IN port (processor byte input) The byte data is placed on the eight bit bi-drectional data bits (bits D0 through D7) by another circuit (8155)) by the specified port is moved to register A. Pin IO/~M goes bit 1, and address pins A7 through A0 contains the port number. A (data). 11011011, port. Addressing: direct; flags: none. Rxample: IN 82.

OUT port (Byte output from processor) The contents of register A is placed on the eight bit bi-directional data bus

(D0 through D7) for transmission the specified port. During data transmission (on the eight bit bi-directional data bus) pin IO/~M goes bit 1 and ~Wr pin goes to bit 0. The IO/~M pin goes bit 1, and port number byte is address value in pins A7 through A0, and then repeated at the most significant byte of address word at pins A8 through A15. (data) A. 11010011, port. Addressing type: direct; flags affected: none. address A: 8155 names: 76543210 x x x x x 0 0 0 command status register x x x x x 0 0 1 port A x x x x x 0 1 0 port B x x x x x 0 1 1 port C. The x means does not care, can be bit 1 or 0. Example: OUT 80.

HLT (halt procesor) The proceesor is stopped. Switch "reset in" pin to restart processor. 01110110.

NOP (no operation) No operation, proceed to next intruction in main memory. Program counter register PC value is incremented by 1. Registers and flags are unaffected. Opcode: 000000002 . Example: NOP.

RIM (read interrupt mask) The RIM intruction loads data into the accumulator relating to interrupts and serial data input. Opcode: 00100000.

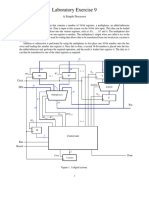

The Processor 8085 Electrical Pins and Pin Descriptions Figure 3 shows the overview of the electrical signal pins of the 8085 microprocessor. The 8085 Microprocessor Pins

Figure 3.

Pin Descriptions

Ale Pin The Ale pin is an output called the address latch (memory) enable. It tells an

external circuit that the AD0 through AD 7

contents are address outputs A0 through A7 when it (Ale) is bit 1. When Ale is bit 0, the pins AD0 through AD7 will be data byte in pins D0 through D7. Pins AD0 Through AD 7

Pins AD0 through AD7 are pins that can be address output pins A0 through A7 or bi-directional data pins D0 through D7 depending in pin ALE bit value. Signal of +5 volts at about 0.025 watt is bit 1. Pins A8 Through A15 Pins A8 Through A15 are address pins part of address bus with A15 being the most significant bit. Most signficant bits of pins A0 through A15. Are tristate outputs as bit 1, 0 or large impedance (no output). VCC Supply VCC is a +5 volt electric supply pin with about 0.2 ampere supply current.

A Simple 8085 Computer Circuit Figure 4.

References 1: Micro-Master MM-8000 8085 Microprocessor - Basic Systems Course; 753808. 2: M8085AH 8 Bit Hmos Microprocessor; Intel. .

8085 Instruction Set Page 1

8085 INSTRUCTION SET

INSTRUCTION DETAILS

DATA TRANSFER INSTRUCTIONS

Opcode Operand Description Copy from source to destination

MOV Rd, Rs This instruction copies the contents of the source M, Rs register into the destination register; the contents of Rd, M the source register are not altered. If one of the operands is a memory location, its location is specified by the contents of the HL registers. Example: MOV B, C or MOV B, M Move immediate 8-bit MVI Rd, data The 8-bit data is stored in the destination register or M, data memory. If the operand is a memory location, its location is specified by the contents of the HL registers. Example: MVI B, 57H or MVI M, 57H Load accumulator LDA 16-bit address The contents of a memory location, specified by a 16-bit address in the operand, are copied to the accumulator. The contents of the source are not altered. Example: LDA 2034H Load accumulator indirect LDAX B/D Reg. pair The contents of the designated register pair point to a memory location. This instruction copies the contents of that memory location into the accumulator. The contents of either the register pair or the memory location are not altered. Example: LDAX B Load register pair immediate LXI Reg. pair, 16-bit data The instruction loads 16-bit data in the register pair designated in the operand. Example: LXI H, 2034H or LXI H, XYZ Load H and L registers direct LHLD 16-bit address The instruction copies the contents of the memory location pointed out by the 16-bit address into register L and copies the contents of the next memory location into register H. The contents of source memory locations are not altered. Example: LHLD 2040H

8085 Instruction Set Page 2 Store accumulator direct STA 16-bit address The contents of the accumulator are copied into the memory location specified by the operand. This is a 3-byte instruction, the second byte specifies the low-order address and the third byte specifies the high-order address.

Example: STA 4350H Store accumulator indirect STAX Reg. pair The contents of the accumulator are copied into the memory location specified by the contents of the operand (register pair). The contents of the accumulator are not altered. Example: STAX B Store H and L registers direct SHLD 16-bit address The contents of register L are stored into the memory location specified by the 16-bit address in the operand and the contents of H register are stored into the next memory location by incrementing the operand. The contents of registers HL are not altered. This is a 3-byte instruction, the second byte specifies the low-order address and the third byte specifies the high-order address. Example: SHLD 2470H Exchange H and L with D and E XCHG none The contents of register H are exchanged with the contents of register D, and the contents of register L are exchanged with the contents of register E. Example: XCHG Copy H and L registers to the stack pointer SPHL none The instruction loads the contents of the H and L registers into the stack pointer register, the contents of the H register provide the high-order address and the contents of the L register provide the low-order address. The contents of the H and L registers are not altered. Example: SPHL Exchange H and L with top of stack XTHL none The contents of the L register are exchanged with the stack location pointed out by the contents of the stack pointer register. The contents of the H register are exchanged with the next stack location (SP+1); however, the contents of the stack pointer register are not altered. Example: XTHL

Push register pair onto stack PUSH Reg. pair The contents of the register pair designated in the operand are copied onto the stack in the following sequence. The stack pointer register is decremented and the contents of the highorder register (B, D, H, A) are copied into that location. The stack pointer register is decremented again and the contents of the low-order register (C, E, L, flags) are copied to that location. Example: PUSH B or PUSH A Pop off stack to register pair POP Reg. pair The contents of the memory location pointed out by the stack pointer register are copied to the low-order register (C, E, L, status flags) of the operand. The stack pointer is incremented by 1 and the contents of that memory location are copied to the high-order register (B, D, H, A) of the operand. The stack pointer register is again incremented by 1. Example: POP H or POP A Output data from accumulator to a port with 8-bit address OUT 8-bit port address The contents of the accumulator are copied into the I/O port specified by the operand. Example: OUT F8H Input data to accumulator from a port with 8-bit address

IN 8-bit port address The contents of the input port designated in the operand are read and loaded into the accumulator. Example: IN 8CH

8085 Instruction Set Page 4 ARITHMETIC INSTRUCTIONS Opcode Operand Description Add register or memory to accumulator ADD R The contents of the operand (register or memory) are M added to the contents of the accumulator and the result is stored in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the addition. Example: ADD B or ADD M Add register to accumulator with carry ADC R The contents of the operand (register or memory) and M the Carry flag are added to the contents of the accumulator and the result is stored in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the addition. Example: ADC B or ADC M Add immediate to accumulator ADI 8-bit data The 8-bit data (operand) is added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition. Example: ADI 45H Add immediate to accumulator with carry ACI 8-bit data The 8-bit data (operand) and the Carry flag are added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition. Example: ACI 45H Add register pair to H and L registers DAD Reg. pair The 16-bit contents of the specified register pair are added to the contents of the HL register and the sum is stored in the HL register. The contents of the source register pair are not altered. If the result is larger than 16 bits, the CY flag is set. No other flags are affected. Example: DAD H

8085 Instruction Set Page 5 Subtract register or memory from accumulator SUB R The contents of the operand (register or memory ) are M subtracted from the contents of the accumulator, and the result is stored in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the subtraction. Example: SUB B or SUB M Subtract source and borrow from accumulator SBB R The contents of the operand (register or memory ) and M the Borrow flag are subtracted from the contents of the accumulator and the result is placed in the accumulator. If the operand is a memory location, its location is specified by

the contents of the HL registers. All flags are modified to reflect the result of the subtraction. Example: SBB B or SBB M Subtract immediate from accumulator SUI 8-bit data The 8-bit data (operand) is subtracted from the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the subtraction. Example: SUI 45H Subtract immediate from accumulator with borrow SBI 8-bit data The 8-bit data (operand) and the Borrow flag are subtracted from the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the subtracion. Example: SBI 45H Increment register or memory by 1 INR R The contents of the designated register or memory) are M incremented by 1 and the result is stored in the same place. If the operand is a memory location, its location is specified by the contents of the HL registers. Example: INR B or INR M Increment register pair by 1 INX R The contents of the designated register pair are incremented by 1 and the result is stored in the same place. Example: INX H

8085 Instruction Set Page 6 Decrement register or memory by 1 DCR R The contents of the designated register or memory are M decremented by 1 and the result is stored in the same place. If the operand is a memory location, its location is specified by the contents of the HL registers. Example: DCR B or DCR M Decrement register pair by 1 DCX R The contents of the designated register pair are decremented by 1 and the result is stored in the same place. Example: DCX H Decimal adjust accumulator DAA none The contents of the accumulator are changed from a binary value to two 4-bit binary coded decimal (BCD) digits. This is the only instruction that uses the auxiliary flag to perform the binary to BCD conversion, and the conversion procedure is described below. S, Z, AC, P, CY flags are altered to reflect the results of the operation. If the value of the low-order 4-bits in the accumulator is greater than 9 or if AC flag is set, the instruction adds 6 to the low-order four bits. If the value of the high-order 4-bits in the accumulator is greater than 9 or if the Carry flag is set, the instruction adds 6 to the high-order four bits. Example: DAA

8085 Instruction Set Page 7 BRANCHING INSTRUCTIONS Opcode Operand Description Jump unconditionally JMP 16-bit address The program sequence is transferred to the memory location

specified by the 16-bit address given in the operand. Example: JMP 2034H or JMP XYZ Jump conditionally Operand: 16-bit address The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Example: JZ 2034H or JZ XYZ Opcode Description Flag Status JC Jump on Carry CY = 1 JNC Jump on no Carry CY = 0 JP Jump on positive S = 0 JM Jump on minus S = 1 JZ Jump on zero Z = 1 JNZ Jump on no zero Z = 0 JPE Jump on parity even P = 1 JPO Jump on parity odd P = 0

8085 Instruction Set Page 8 Unconditional subroutine call CALL 16-bit address The program sequence is transferred to the memory location specified by the 16-bit address given in the operand. Before the transfer, the address of the next instruction after CALL (the contents of the program counter) is pushed onto the stack. Example: CALL 2034H or CALL XYZ Call conditionally Operand: 16-bit address The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Before the transfer, the address of the next instruction after the call (the contents of the program counter) is pushed onto the stack. Example: CZ 2034H or CZ XYZ Opcode Description Flag Status CC Call on Carry CY = 1 CNC Call on no Carry CY = 0 CP Call on positive S = 0 CM Call on minus S = 1 CZ Call on zero Z = 1 CNZ Call on no zero Z = 0 CPE Call on parity even P = 1 CPO Call on parity odd P = 0

8085 Instruction Set Page 9 Return from subroutine unconditionally RET none The program sequence is transferred from the subroutine to the calling program. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RET Return from subroutine conditionally Operand: none The program sequence is transferred from the subroutine to the calling program based on the specified flag of the PSW as described below. The two bytes from the top of the stack are copied into the program counter, and program execution

begins at the new address. Example: RZ Opcode Description Flag Status RC Return on Carry CY = 1 RNC Return on no Carry CY = 0 RP Return on positive S = 0 RM Return on minus S = 1 RZ Return on zero Z = 1 RNZ Return on no zero Z = 0 RPE Return on parity even P = 1 RPO Return on parity odd P = 0

8085 Instruction Set Page 10 Load program counter with HL contents PCHL none The contents of registers H and L are copied into the program counter. The contents of H are placed as the high-order byte and the contents of L as the low-order byte. Example: PCHL Restart RST 0-7 The RST instruction is equivalent to a 1-byte call instruction to one of eight memory locations depending upon the number. The instructions are generally used in conjunction with interrupts and inserted using external hardware. However these can be used as software instructions in a program to transfer program execution to one of the eight locations. The addresses are: Instruction Restart Address RST 0 0000H RST 1 0008H RST 2 0010H RST 3 0018H RST 4 0020H RST 5 0028H RST 6 0030H RST 7 0038H The 8085 has four additional interrupts and these interrupts generate RST instructions internally and thus do not require any external hardware. These instructions and their Restart addresses are: Interrupt Restart Address TRAP 0024H RST 5.5 002CH RST 6.5 0034H RST 7.5 003CH

8085 Instruction Set Page 11 LOGICAL INSTRUCTIONS Opcode Operand Description Compare register or memory with accumulator CMP R The contents of the operand (register or memory) are M compared with the contents of the accumulator. Both contents are preserved . The result of the comparison is shown by setting the flags of the PSW as follows: if (A) < (reg/mem): carry flag is set if (A) = (reg/mem): zero flag is set

if (A) > (reg/mem): carry and zero flags are reset Example: CMP B or CMP M Compare immediate with accumulator CPI 8-bit data The second byte (8-bit data) is compared with the contents of the accumulator. The values being compared remain unchanged. The result of the comparison is shown by setting the flags of the PSW as follows: if (A) < data: carry flag is set if (A) = data: zero flag is set if (A) > data: carry and zero flags are reset Example: CPI 89H Logical AND register or memory with accumulator ANA R The contents of the accumulator are logically ANDed with M the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the operation. CY is reset. AC is set. Example: ANA B or ANA M Logical AND immediate with accumulator ANI 8-bit data The contents of the accumulator are logically ANDed with the 8-bit data (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY is reset. AC is set. Example: ANI 86H

8085 Instruction Set Page 12 Exclusive OR register or memory with accumulator XRA R The contents of the accumulator are Exclusive ORed with M the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: XRA B or XRA M Exclusive OR immediate with accumulator XRI 8-bit data The contents of the accumulator are Exclusive ORed with the 8-bit data (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: XRI 86H Logical OR register or memory with accumulaotr ORA R The contents of the accumulator are logically ORed with M the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: ORA B or ORA M Logical OR immediate with accumulator ORI 8-bit data The contents of the accumulator are logically ORed with the 8-bit data (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: ORI 86H Rotate accumulator left RLC none Each binary bit of the accumulator is rotated left by one

position. Bit D7 is placed in the position of D0 as well as in the Carry flag. CY is modified according to bit D7. S, Z, P, AC are not affected. Example: RLC Rotate accumulator right RRC none Each binary bit of the accumulator is rotated right by one position. Bit D0 is placed in the position of D7 as well as in the Carry flag. CY is modified according to bit D0. S, Z, P, AC are not affected. Example: RRC

8085 Instruction Set Page 13 Rotate accumulator left through carry RAL none Each binary bit of the accumulator is rotated left by one position through the Carry flag. Bit D7 is placed in the Carry flag, and the Carry flag is placed in the least significant position D0. CY is modified according to bit D7. S, Z, P, AC are not affected. Example: RAL Rotate accumulator right through carry RAR none Each binary bit of the accumulator is rotated right by one position through the Carry flag. Bit D0 is placed in the Carry flag, and the Carry flag is placed in the most significant position D7. CY is modified according to bit D0. S, Z, P, AC are not affected. Example: RAR Complement accumulator CMA none The contents of the accumulator are complemented. No flags are affected. Example: CMA Complement carry CMC none The Carry flag is complemented. No other flags are affected. Example: CMC Set Carry STC none The Carry flag is set to 1. No other flags are affected. Example: STC

8085 Instruction Set Page 14 CONTROL INSTRUCTIONS Opcode Operand Description No operation NOP none No operation is performed. The instruction is fetched and decoded. However no operation is executed. Example: NOP Halt and enter wait state HLT none The CPU finishes executing the current instruction and halts any further execution. An interrupt or reset is necessary to exit from the halt state. Example: HLT Disable interrupts DI none The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled. No flags are affected. Example: DI Enable interrupts EI none The interrupt enable flip-flop is set and all interrupts are enabled. No flags are affected. After a system reset or the

acknowledgement of an interrupt, the interrupt enable flipflop is reset, thus disabling the interrupts. This instruction is necessary to reenable the interrupts (except TRAP). Example: EI

8085 Instruction Set Page 15 Read interrupt mask RIM none This is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit. The instruction loads eight bits in the accumulator with the following interpretations. Example: RIM Set interrupt mask SIM none This is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output. The instruction interprets the accumulator contents as follows. Example: SIM Read more: http://wiki.answers.com/Q/74_basic_instructions_set_in_8085_microprocessor#ixzz3q H8StjXS

Potrebbero piacerti anche

- 8255Documento34 pagine8255Manjula Bn100% (1)

- 8088 Instruction SetDocumento6 pagine8088 Instruction SetMuhammad RezkyNessuna valutazione finora

- By: Dr. Anil Swarnkar Assistant Professor Department of Electrical Engineering, MNIT, JaipurDocumento115 pagineBy: Dr. Anil Swarnkar Assistant Professor Department of Electrical Engineering, MNIT, Jaipurpankajkthr100% (2)

- Matica Z3Documento2 pagineMatica Z3MCO di Osio Igor100% (1)

- Microprocessor and Architecture Solution PDFDocumento23 pagineMicroprocessor and Architecture Solution PDFKarmaveer Bhaurao Patil CollegeNessuna valutazione finora

- Microcontroller - PDF 1411210674Documento27 pagineMicrocontroller - PDF 1411210674Anney RevathiNessuna valutazione finora

- Microprosser 8085Documento15 pagineMicroprosser 8085saigdv1978Nessuna valutazione finora

- 8085 Instruction Set Gaonkar WordpresscomDocumento4 pagine8085 Instruction Set Gaonkar WordpresscomPrabhat PankajNessuna valutazione finora

- Instruction Set 8085Documento15 pagineInstruction Set 8085MuhammadAli VellaniNessuna valutazione finora

- 8085 Instruction SetDocumento27 pagine8085 Instruction Setbostanci100% (1)

- 8085 Instruction SetDocumento79 pagine8085 Instruction SetsivaperumalNessuna valutazione finora

- Ilovepdf MergedDocumento430 pagineIlovepdf MergedYuvraj ChhabraNessuna valutazione finora

- Instruction Set 8085Documento19 pagineInstruction Set 8085internetwealthdonNessuna valutazione finora

- Ramesh Mandal PPT 3rd YearDocumento26 pagineRamesh Mandal PPT 3rd YearRAMESH MANDALNessuna valutazione finora

- Digital Techniques and MicroprocessorsDocumento3 pagineDigital Techniques and MicroprocessorsHarshal DevadeNessuna valutazione finora

- Programming Practices With SimulatorsDocumento11 pagineProgramming Practices With Simulatorsarun0% (2)

- 8085 Programming Examples - CollegeekDocumento6 pagine8085 Programming Examples - CollegeekH Aries OñaNessuna valutazione finora

- Traffic Light ControllerDocumento16 pagineTraffic Light ControllerJoshua Jebaraj JosephNessuna valutazione finora

- Assembler Language - 8051powerpoint PresentationDocumento56 pagineAssembler Language - 8051powerpoint PresentationtauseeeeeeeeNessuna valutazione finora

- Timing Diagram of 8085 Instructions: Prof. Jagadish Bhattacharya. ECE Dept., HETCDocumento18 pagineTiming Diagram of 8085 Instructions: Prof. Jagadish Bhattacharya. ECE Dept., HETCNitesh Kumar RamNessuna valutazione finora

- 8251 UsartDocumento24 pagine8251 UsartNava KrishnanNessuna valutazione finora

- Mupi 2 MarksDocumento11 pagineMupi 2 Marksveeyesyes08Nessuna valutazione finora

- 8085 Addressing Modes and Memory MappingDocumento8 pagine8085 Addressing Modes and Memory MappingRocky SamratNessuna valutazione finora

- Interfacing Prgrammable Keyboard and Display Controller - 8279Documento3 pagineInterfacing Prgrammable Keyboard and Display Controller - 8279senthilvlNessuna valutazione finora

- 8086 ManualDocumento45 pagine8086 ManualGarima SinghalNessuna valutazione finora

- Assemblylanguageprogrammingof8085 100523023329 Phpapp02Documento52 pagineAssemblylanguageprogrammingof8085 100523023329 Phpapp02Napoleon LygdasNessuna valutazione finora

- Chapter 2.1-Introduction To 8085 Instruction SetDocumento47 pagineChapter 2.1-Introduction To 8085 Instruction SetBulbula KumedaNessuna valutazione finora

- 8279 Keyboard and Display ControllerDocumento33 pagine8279 Keyboard and Display Controllergutzz0079197100% (1)

- DE09 SolDocumento157 pagineDE09 SolRakesh KumarNessuna valutazione finora

- 8085 Instruction Set: Instruction Summary Data Transfer InstructionsDocumento2 pagine8085 Instruction Set: Instruction Summary Data Transfer Instructionsganesh92Nessuna valutazione finora

- RP Jain Adc DacDocumento27 pagineRP Jain Adc DacAnand SinghNessuna valutazione finora

- Interfacing Analog To Digital Data ConvertersDocumento16 pagineInterfacing Analog To Digital Data ConvertersPrabin123Nessuna valutazione finora

- Lab9 VHDLDocumento8 pagineLab9 VHDLFasli CoolNessuna valutazione finora

- MICROPORCESSOR 8085 Lab ManualDocumento53 pagineMICROPORCESSOR 8085 Lab ManualAjay PatilNessuna valutazione finora

- Assignment 1Documento9 pagineAssignment 1Smarajit MishraNessuna valutazione finora

- 8085Documento56 pagine8085Kunal MeherNessuna valutazione finora

- 8086 Microprocessor For ScientistDocumento21 pagine8086 Microprocessor For ScientistRam Kishore RoyNessuna valutazione finora

- MPI Unit 2Documento4 pagineMPI Unit 2Dishant RathiNessuna valutazione finora

- Interfacing Programs For 8085Documento37 pagineInterfacing Programs For 8085archankumarturagaNessuna valutazione finora

- AZI - Computer Architecture - 672.7E Exams Questions List - 2018Documento6 pagineAZI - Computer Architecture - 672.7E Exams Questions List - 2018Murad QəhramanovNessuna valutazione finora

- Laboratory Experiment For Digital ElectronicsDocumento1 paginaLaboratory Experiment For Digital ElectronicsPiyush RajNessuna valutazione finora

- Instruction Set of 8085 Microprocessor By, Er. Swapnil V. KawareDocumento107 pagineInstruction Set of 8085 Microprocessor By, Er. Swapnil V. KawareswapnilNessuna valutazione finora

- C5 - Intro To 8085 - Hardware PDFDocumento39 pagineC5 - Intro To 8085 - Hardware PDFsiti hajarNessuna valutazione finora

- EE8551-Microprocessors and MicrocontrollersDocumento13 pagineEE8551-Microprocessors and MicrocontrollersPACET EEENessuna valutazione finora

- 8086 Trainer Kit User and Technical Reference Manual PDFDocumento71 pagine8086 Trainer Kit User and Technical Reference Manual PDFJohn Johnston0% (1)

- Push Pop Instruction 8085 MicroprocessorDocumento3 paginePush Pop Instruction 8085 MicroprocessorRohan Gaonkar0% (1)

- 8085 Microprocessor Programs 1. Statement:: Store The Data Byte 32H Into Memory Location 4000HDocumento19 pagine8085 Microprocessor Programs 1. Statement:: Store The Data Byte 32H Into Memory Location 4000Hnirmal_inboxNessuna valutazione finora

- Question Bank - 150504 - Session - 19 - 20Documento14 pagineQuestion Bank - 150504 - Session - 19 - 20Aashutosh TiwariNessuna valutazione finora

- 8085 and 8051 PresentationDocumento54 pagine8085 and 8051 PresentationJitendra Chuugh100% (3)

- Microprocessor and InterfacingDocumento25 pagineMicroprocessor and InterfacingEr Bhavik PatelNessuna valutazione finora

- 8051 Microcontroller FAQDocumento160 pagine8051 Microcontroller FAQkranthi633Nessuna valutazione finora

- Dspa 17ec751 M5Documento34 pagineDspa 17ec751 M5digital loveNessuna valutazione finora

- Programming The MCU 8051 PDFDocumento48 pagineProgramming The MCU 8051 PDFDK White LionNessuna valutazione finora

- LCD and Keyboard Interfacing: Unit VDocumento21 pagineLCD and Keyboard Interfacing: Unit VrushitaaNessuna valutazione finora

- 8051 PPT For MSCDocumento138 pagine8051 PPT For MSCvikash sharmaNessuna valutazione finora

- 8085 Complete ArchitectureDocumento39 pagine8085 Complete ArchitectureSana KhanNessuna valutazione finora

- Unit 2Documento166 pagineUnit 2rohanrec92Nessuna valutazione finora

- Microprocessor 8085 & 8086 ProgramsDocumento141 pagineMicroprocessor 8085 & 8086 ProgramsDwane Almeida100% (1)

- Machine Architecture (Instruction Set 8085)Documento11 pagineMachine Architecture (Instruction Set 8085)Shubham KediaNessuna valutazione finora

- Addressing Modes & Instruction SetDocumento39 pagineAddressing Modes & Instruction SetlekaNessuna valutazione finora

- 8085 Architecture Pin DiagramDocumento21 pagine8085 Architecture Pin DiagramAshfaq SulaimanNessuna valutazione finora

- Leith Food Menu s22 CompressedDocumento1 paginaLeith Food Menu s22 CompressedSindu RangaswamyNessuna valutazione finora

- Chapter 10 PDFDocumento36 pagineChapter 10 PDFSindu RangaswamyNessuna valutazione finora

- Chapter 7Documento48 pagineChapter 7Sindu RangaswamyNessuna valutazione finora

- Subject Code: Cs2302 Subject Name: Computer Networks: Two MarksDocumento32 pagineSubject Code: Cs2302 Subject Name: Computer Networks: Two MarksSindu RangaswamyNessuna valutazione finora

- Introduction To VirtualizationDocumento64 pagineIntroduction To VirtualizationSindu RangaswamyNessuna valutazione finora

- Distinguish Between Window PortDocumento8 pagineDistinguish Between Window PortSindu RangaswamyNessuna valutazione finora

- Pressman CH 8 Analysis ModelingDocumento34 paginePressman CH 8 Analysis ModelingSindu RangaswamyNessuna valutazione finora

- hw1 SolDocumento3 paginehw1 SolmanalidubalNessuna valutazione finora

- CN QBDocumento18 pagineCN QBSindu RangaswamyNessuna valutazione finora

- 2 ACM Java GraphicsDocumento22 pagine2 ACM Java GraphicsSindu RangaswamyNessuna valutazione finora

- PQT NotesDocumento337 paginePQT NotesDot Kidman100% (1)

- Low Pass Filter Installation For Reducing Harmonic Current Emissions From LED Lamps Based On EMC StandardDocumento4 pagineLow Pass Filter Installation For Reducing Harmonic Current Emissions From LED Lamps Based On EMC StandardEduardo Lourenco De SousaNessuna valutazione finora

- HRUI POE Switch Catalog2020Documento8 pagineHRUI POE Switch Catalog2020delapenar843Nessuna valutazione finora

- Adc ProgramDocumento3 pagineAdc ProgramMallikarjun DeshmukhNessuna valutazione finora

- Fullwave RectifierDocumento4 pagineFullwave RectifierAlex VuNessuna valutazione finora

- PAT Serena New BuildingDocumento15 paginePAT Serena New BuildingMuhammad IsmaildadNessuna valutazione finora

- Arima Comm BU3 Profile & Roadmap 3 - 2008Documento31 pagineArima Comm BU3 Profile & Roadmap 3 - 2008yujochiNessuna valutazione finora

- DatasheetDocumento4 pagineDatasheetselocaNessuna valutazione finora

- Evaluation Voltage Excitation TestsDocumento34 pagineEvaluation Voltage Excitation Testshajimak100% (2)

- Cornwall III Spec Sheet v03Documento1 paginaCornwall III Spec Sheet v03Cotcot PianoNessuna valutazione finora

- JVC HX d7Documento2 pagineJVC HX d7Zoran BunčićNessuna valutazione finora

- AN000042 SERCOS Troubleshooting Guide - ApplicationNote - En-Us - Revision1Documento14 pagineAN000042 SERCOS Troubleshooting Guide - ApplicationNote - En-Us - Revision1uongquocvuNessuna valutazione finora

- ECEG-1551-FEC-Lec - 02 - DC AnalysisDocumento100 pagineECEG-1551-FEC-Lec - 02 - DC AnalysisErmias MesfinNessuna valutazione finora

- Antenna Rotator System: Jan/2019 Rev 3.2gDocumento50 pagineAntenna Rotator System: Jan/2019 Rev 3.2gTasos koyraNessuna valutazione finora

- Introduction To TMS320C6000 DSP Optimization: Application ReportDocumento31 pagineIntroduction To TMS320C6000 DSP Optimization: Application ReportHai Le Ngoc HaiNessuna valutazione finora

- Lab 9 Comb CKT With MUX and DEC Full PackageDocumento4 pagineLab 9 Comb CKT With MUX and DEC Full PackageLoveWorldCanadaNessuna valutazione finora

- Top 10 Design RecommendationsDocumento25 pagineTop 10 Design RecommendationsUnik WadhwaniNessuna valutazione finora

- Fwhomfbrhi 27435 FWHOMFBRHIDocumento19 pagineFwhomfbrhi 27435 FWHOMFBRHIAnu AnushaNessuna valutazione finora

- What Is NanoWatt TechnologyDocumento1 paginaWhat Is NanoWatt Technologyfolk_sharathNessuna valutazione finora

- Ihm Exor PDFDocumento4 pagineIhm Exor PDFMário Sérgio OliveiraNessuna valutazione finora

- 19" LCD Color Monitor AOC LM960sDocumento57 pagine19" LCD Color Monitor AOC LM960sRaúl García LópezNessuna valutazione finora

- Lesson Plan in ComputerDocumento3 pagineLesson Plan in ComputerAngelo SorianoNessuna valutazione finora

- Digi Delay Construction GuideDocumento11 pagineDigi Delay Construction GuidetumundoalternoNessuna valutazione finora

- Osmeoisis 2022-09-06 15-33-19PIC - Enh-Mig - C - 9Documento20 pagineOsmeoisis 2022-09-06 15-33-19PIC - Enh-Mig - C - 9Tomás BurónNessuna valutazione finora

- Zse 30Documento14 pagineZse 30awttceoNessuna valutazione finora

- Sistema de Mensajes MeridianDocumento1.252 pagineSistema de Mensajes MeridianEduardo Javier0% (1)

- Wireless Transmission Detection and Monitoring System Using GNU Radio and Multiple RTL - SDR ReceiversDocumento7 pagineWireless Transmission Detection and Monitoring System Using GNU Radio and Multiple RTL - SDR ReceiversBHARGAV VANAPALLINessuna valutazione finora

- Il2220 2B5457, PHD Course Low-Power Analog & Mixed Signal IcsDocumento18 pagineIl2220 2B5457, PHD Course Low-Power Analog & Mixed Signal IcsAnchit JainNessuna valutazione finora

- Chapter - 24-By DR Sajid Ali Ansari 2021Documento34 pagineChapter - 24-By DR Sajid Ali Ansari 202175wpt82qvyNessuna valutazione finora

- How To Make SMPS Pass Surge & Lightning TestDocumento10 pagineHow To Make SMPS Pass Surge & Lightning TestdcasdcasdcasdcNessuna valutazione finora