Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Cap9 Registros

Caricato da

Nanis PardoTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Cap9 Registros

Caricato da

Nanis PardoCopyright:

Formati disponibili

Captulo 9

Registros

9.1.

Introduccin

Un registro no es ms que un conjunto de biestables que almacenan una palabra. Los ms usados son los de entrada y salida en paralelo, que almacenan una palabra de n bits. No obstante en sistemas de comunicaciones son muy tiles los denominados registros de desplazamiento, que como veremos nos permiten enviar una palabra de n bits por un solo cable, enviando los bits en serie de uno en uno.

9.2.

Registros de entrada y salida en paralelo

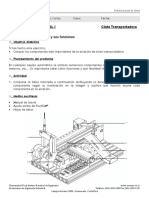

Estos registros estn compuestos por n biestables de tipo D y almacenan una palabra de n bits (uno por biestable obviamente). En la gura 9.1 se muestra un registro de 4 bits. Como se puede observar el registro no es ms que 4 biestables con las entradas de reloj y clear unidas. Por tanto, en cada anco de reloj la entrada de datos se copiar a la salida, donde permanecer estable hasta el siguiente anco de reloj. Descripcin en VHDL La descripcin en VHDL de un registro se realiza en un process, de una forma similar a como se han descrito los registros que almacenan el estado en las mquinas

d3 d2 d1 d0

clk reset_n q3 q2 q1 q0

Figura 9.1: Registro con entrada y salida en paralelo. 175

176

Registros

de estado del captulo anterior.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29

-- Registro de 4 bits library ieee; use ieee. std_logic_1164 .all; entity Registro is port ( clk reset_n d q

: : : :

in in in out

std_logic ; -- Entradas de control std_logic ; std_logic_vector (3 downto 0); -- datos std_logic_vector (3 downto 0));

end Registro ; architecture behavioral of Registro is begin -- behavioral

process (clk , reset_n , d) begin if reset_n = 0 then q <= ( others => 0); elsif clk event and clk = 1 then q <= d; end if; end process ; end behavioral ;

9.2.1.

Registros con control de carga

El registro anterior actualiza su salida en cada anco de reloj. No obstante existen numerosas aplicaciones en las que es necesario controlar mediante una seal de enable cuando ha de almacenarse un nuevo valor en el registro. En este caso el circuito resultante es el mostrado en la gura 9.2. Como puede observar se ha aadido un multiplexor que controla si cuando llegue el anco de reloj ha de cargarse en el registro el dato de entrada o el valor que est almacenado en el registro.

9 Registros

177

d3 0 1

d2 0 1

d1 0 1

d0 0 1

clk reset_n en q3 q2 q1 q0

Figura 9.2: Registro con entrada y salida en paralelo y control de carga.

Descripcin en VHDL En este caso se aade a la descripcin anterior un if (lneas 2628) para que la salida slo se actualice cuando la seal de enable (en) est activa:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

-- Registro de 4 bits con habilitacin de la carga library ieee; use ieee. std_logic_1164 .all; entity RegistroEn is port ( clk reset_n en d q

: : : : :

in in in in out

std_logic ; -- Entradas de control std_logic ; std_logic ; -- Habilitacin carga std_logic_vector (3 downto 0); -- datos std_logic_vector (3 downto 0));

end RegistroEn ; architecture behavioral of RegistroEn is begin -- behavioral

process (clk , reset_n , en , d) begin if reset_n = 0 then q <= ( others => 0); elsif clk event and clk = 1 then if en = 1 then q <= d; end if;

178

Registros

1 0 1 1 0 0 1 0 Paralelo

Sistema Digital

Sistema Digital

Sistema Digital

1 0 1 1 0 0 1 0

Serie

Figura 9.3: Transmisin paralelo y transmisin serie de datos.

29 30 31 32

end if; end process ; end behavioral ;

9.3.

Registros de desplazamiento

En un sistema digital se trabaja normalmente con palabras de n bits, sobre las que se hacen una serie de operaciones. Si se desea transmitir una de estas palabras a otro sistema una solucin es emplear n cables y por cada uno de ellos enviar un bit. Por ejemplo las primeras impresoras se conectaban al ordenador mediante un cable paralelo de 8 bits, por el que se poda enviar un byte de una vez. La otra alternativa es conectar los dos sistemas mediante un cable y por l enviar los n bits uno detrs de otro. Ambos mtodos se ilustran grcamente en la gura 9.3. La conversin de datos de paralelo a serie y de serie a paralelo se realiza mediante los denominados registros de desplazamiento, los cuales se estudian en esta seccin.

9.3.1.

Registro de entrada serie y salida en paralelo

Este registro permite convertir una secuencia de n bits que entran en serie en una palabra de n bits. El diagrama del circuito (para palabras de 4 bits) se muestra en la gura 9.4. Como puede observar, consta de 4 ipops en los que la salida de cada uno se conecta a la entrada del siguiente, de forma que en cada anco de reloj la palabra binaria que almacena se desplaza a la derecha. El hueco dejado por la palabra en el bit 3 se rellena con el valor de la entrada serie e_s y el bit 0 desaparece. En la gura 9.5 puede ver un diagrama de tiempos de la simulacin del funcionamiento del circuito. Descripcin en VHDL Para describir el registro de desplazamiento en VHDL lo primero que necesitamos es crear una seal interna para almacenar el registro (a la que se ha denominado precisamente registro), ya que el lenguaje impide obtener el valor de una seal de

Sistema Digital

9 Registros

179

e_s

clk reset_n s_p(3) s_p(2) s_p(1) s_p(0)

Figura 9.4: Registro serieparalelo.

salida y como podemos ver en el esquema del circuito las salidas de los ipops tambin se conectan a las entradas de los siguientes. La descripcin de registro propiamente dicha es similar a la del registro paralelo paralelo: cuando se activa el reset se pone el registro a cero y si el reset no est activo cuando se produce un anco de subida del reloj se desplaza el contenido del registro. La descripcin del desplazamiento se realiza en las lneas 26 y 27. En la primera se dice que la entrada serie se guarda en el bit tres del registro y en la segunda se dice que los bits 3 al 1 se guardan en los bits 2 al 0. Esta asignacin se hace en el mismo orden en el que se describe, es decir, el bit 3 se conecta al 2, el bit 2 al 1 y el 1 al 0. Por ltimo, en la lnea 31 se conecta el registro a la salida. Ntese que esta conexin se realiza fuera del process, aunque se podra haber realizado dentro obteniendo el mismo resultado. Se ha realizado as para dejar dentro del process solamente la descripcin del registro.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

-- Registro de desplazamiento con entrada serie y salida -- paralelo de 4 bits library ieee; use ieee. std_logic_1164 .all; entity RegSerPar is port ( clk reset_n e_s s_p

: : : :

in in in out

std_logic ; std_logic ; std_logic ; -- Entrada serie std_logic_vector (3 downto 0)); -- salida

end RegSerPar ; architecture behavioral of RegSerPar is signal registro : std_logic_vector (3 downto 0); begin -- behavioral

180

Registros

Figura 9.5: Simulacin del registro con entrada serie y salida en paralelo.

21 22 23 24 25 26 27 28 29 30

int main(void) { printf("Hola\n"); return 0; }

31 32

Reg: process (clk , reset_n , e_s , registro ) begin -- process Reg if reset_n = 0 then registro <= ( others => 0); elsif clk event and clk = 1 then registro (3) <= e_s; registro (2 downto 0) <= registro (3 downto 1); end if; end process Reg; -- Se copia el registro a la salida paralelo . s_p <= registro ; end behavioral ;

Una simulacin del circuito descrito se encuentra en la gura 9.5.

Realice el ejercicio 1

9.3.2.

Registro de entrada paralelo y salida en serie

Este registro realiza la funcin contraria al anterior: se carga una palabra en paralelo y se desplaza a la derecha en cada anco de reloj. El diagrama del circuito para un registro de 4 bits es el mostrado en la gura 9.6. En este registro existe una seal adicional denominada c_d que controla los multiplexores a la entrada de los ipops. As, cuando esta seal vale 0 se conectan las entradas paralelo (e_p) a las entradas de los ipops, por lo que cuando llegue el anco de subida del reloj se cargarn dichas entradas e_p en el registro. Cuando la seal c_d vale 1 se conecta a la entrada de cada ipop la salida del siguiente, excepto la entrada del ipop 3 que se conecta a tierra y la salida del ipop 0 que es la salida serie. De esta forma, en cada anco de subida del reloj se desplazar el contenido del registro a la derecha, introduciendo ceros por el bit ms signicativo. Una simulacin del circuito se muestra en la gura 9.7.

9 Registros

181

e_p(3) 0 1

e_p(2) 0 1

e_p(1) 0 1

e_p(0) 0 1 s_s

clk reset_n c_d

Figura 9.6: Registro paraleloserie.

Descripcin en VHDL La descripcin es similar a la del registro serieparalelo. La nica diferencia radica ahora en la descripcin de la carga paralelo que se realiza mediante el if de la lnea 27, de forma que cuando la seal c_d vale 0 se carga la entrada paralelo e_p en el registro y cuando vale 1 desplaza el contenido del registro, introduciendo un 0 por el bit 3.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

-- Registro de desplazamiento con entrada paralelo de 4 bits -- y salida serie library ieee; use ieee. std_logic_1164 .all; entity RegParSer is port ( clk reset_n c_d e_p s_s

: : : : :

in in in in out

std_logic ; std_logic ; std_logic ; -- Carga (0) o desplaza (1) std_logic_vector (3 downto 0); -- Entrada std_logic ); -- Salida serie

end RegParSer ; architecture behavioral of RegParSer is signal registro : std_logic_vector (3 downto 0); begin -- behavioral Reg: process (clk , reset_n , registro , e_p) begin if reset_n = 0 then registro <= ( others => 0); elsif clk event and clk = 1 then if c_d = 0 then -- Carga

182

Registros

Figura 9.7: Simulacin del registro con entrada paralelo y salida en serie.

28 29 30 31 32 33 34 35

int main(void) { printf("Hola\n"); return 0; }

registro <= e_p; else -- Desplaza registro (3) <= 0; -- Se introducen ceros . registro (2 downto 0) <= registro (3 downto 1); end if; end if; end process Reg; -- Se copia el bit menos significativo a la salida serie . s_s <= registro (0); end behavioral ;

36 37 38

Realice los ejercicios 2 y3

9.3.3.

Registro de desplazamiento universal

Este registro es una combinacin de los tres anteriores, en el que adems se aade la posibilidad de desplazar tambin a la izquierda. Para ello se usa ahora una seal de control c de dos bits que permite que el circuito tenga cuatro funcionalidades: desplazamiento a izquierda cuando la seal de control sea 00, mantenimiento cuando sea 01, carga paralelo cuando sea 10 y desplazamiento a derecha cuando sea 11. El circuito se muestra en la gura 9.8. Para seleccionar el modo de funcionamiento del registro se usa un multiplexor en el que la entrada 0 se conecta a la salida del ipop de la derecha para realizar el desplazamiento a la izquierda, la 1 a la salida del propio ipop para mantener el valor, la 2 a la entrada paralelo para almacenar un nuevo valor en el registro y por ltimo la 3 al ipop de la izquierda para realizar un desplazamiento a la derecha. En el caso de los desplazamientos a izquierda se introduce un nuevo bit en el registro mediante la entrada serie que est a la derecha (es_d) y la salida serie ss_i coincide con el bit ms signicativo de la salida paralelo (s_p(3)). Del mismo modo cuando se desplaza a derecha se introduce por la izquierda el bit presente en la entrada es_i y la salida serie se realiza por ss_d que coincide con el bit menos signicativo del registro.

9 Registros

183

e_p(3) esi c 3 2 1 0

e_p(2)

e_p(1)

e_p(0)

esd

3 2 1 0

3 2 1 0

3 2 1 0

clk reset_n ssi s_p(3) s_p(2) s_p(1) s_p(0) ssd

Figura 9.8: Registro de desplazamiento universal.

Descripcin en VHDL La descripcin en VHDL es similar a la del resto de registros, slo que ahora mediante el if de la lnea 34 se selecciona qu ha de hacer el circuito en el anco en funcin de la seal de control. As cuando es 00 se desplaza a izquierda, cuando es 10 se realiza la carga paralelo y cuando es 11 se desplaza a derecha. Ntese que no se ha incluido en el if el valor 01 ya que en este caso el registro mantiene su valor y por tanto no hay que hacer nada.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

------

Registro de desplazamiento con entrada paralelo de 4 bits y posibilidad de desplazar a izquierda y derecha . Mediante la entrada c se controla el funcionamiento del circuito : c=00 Desplaza a Izq., c=01 Mantenimiento , c=10 Carga , C=11 Desplaza a Der.

library ieee; use ieee. std_logic_1164 .all; entity RegDespl is port ( clk reset_n c esd esi e_p s_p

: : : : : : :

in in in in in in out

std_logic ; std_logic ; std_logic_vector (1 downto 0); -- Control std_logic ; -- entrada serie Der. std_logic ; -- entrada serie Izq. std_logic_vector (3 downto 0);-- E. paralelo std_logic_vector (3 downto 0);-- S. paralelo

184

Registros

20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53

ssd ssi

: out std_logic ; : out std_logic );

-- salida serie Der. -- salida serie Izq.

end RegDespl ; architecture behavioral of RegDespl is signal registro : std_logic_vector (3 downto 0); begin -- behavioral Reg: process (clk , reset_n , registro , e_p , c) begin if reset_n = 0 then registro <= ( others => 0); elsif clk event and clk = 1 then if c = "00" then -- Desplaza a Izq. registro (0) <= esd; registro (3 downto 1) <= registro (2 downto 0); elsif c = "10" then -- Carga registro <= e_p; elsif c = "11" then -- Desplaza a Der. registro (3) <= esi; registro (2 downto 0) <= registro (3 downto 1); end if; end if; end process Reg; -- Se copia el bit menos significativo a la salida serie -- Derecha . ssd <= registro (0); -- El ms significativo a la salida serie Izquierda ssi <= registro (3); -- Y el registro a la salida paralelo s_p <= registro ; end behavioral ;

9.4.

Ejercicios

1. Modique el registro de entrada serie y salida en paralelo mostrado en la seccin 9.3.1 para que el desplazamiento en lugar de realizarse en cada anco de reloj se realice slo cuando se indique mediante una seal de entrada, a la que se denominar enable. As, cuando esta seal valga 0 el registro mantendr su valor, incluso aunque lleguen ancos de reloj. Si por el contrario la seal vale 1 cuando llegue un anco de reloj el circuito realizar un desplazamiento

9 Registros

185

de un bit a la derecha. Realice en primer lugar un esquema del circuito y a continuacin descrbalo en VHDL. 2. Repita el ejercicio anterior para el registro de entrada en paralelo y salida en serie mostrado en la seccin 9.3.2. 3. Modique el cdigo del ejercicio anterior para que el nmero de bits del registro se especique mediante un genrico. 4. Se acaba de comprar un coche y para sorprender a sus amistades se le ocurre instalarle lo ltimo en tuning: un juego de luces en la parte delantera al estilo del coche fantstico. Para fardar todava ms, decide hacer usted mismo la electrnica de control. El circuito ser capaz de controlar 6 lmparas. Al inicializarlo con la seal de reset se iluminar solo la lmpara izquierda. Despus de medio segundo se apagar la lmpara izquierda y se encender la que le sigue. La secuencia completa ser la mostrada a continuacin:

100000 010000 001000 000100 000010 000001 000010 000100 001000 010000 100000

Para disear el circuito dispone de un reloj de 2 Hz. Realice en primer lugar un circuito usando puertas lgicas, ipops, multiplexores, etc. A continuacin describa el circuito diseado en VHDL. Nota: Es fcil implantar el circuito anterior mediante un registro de desplazamiento que pueda desplazar en los dos sentidos. 5. Despus del xito conseguido con el diseo del problema anterior, decide actualizar un poco el juego de luces para el tuning de su coche. El circuito ser capaz de controlar 6 lmparas. Al inicializarlo con la seal de reset se apagarn todas las lmparas. Despus de medio segundo se encender la lmpara izquierda, despus de otro medio segundo se encender la que sigue, continundose la secuencia hasta que se hayan encendido todas las luces. Entonces se continuar la secuencia apagando la luz derecha, luego la que est a su izquierda, etc. La secuencia completa ser la mostrada a continuacin:

186

Registros

000000 100000 110000 111000 111100 111110 111111 111110 111100 111000 110000 100000 000000

Para disear el circuito dispone de un reloj de 2 Hz. Realice en primer lugar un circuito usando puertas lgicas, ipops, multiplexores, etc. A continuacin describa el circuito diseado en VHDL. Nota: Es fcil implantar el circuito anterior mediante un registro de desplazamiento que pueda desplazar en los dos sentidos. 6. Disee un circuito digital para mostrar en dos displays la temperatura mxima y mnima. El valor de la temperatura lo proporciona un sensor en formato signo/magnitud de 7 bits. Adems de la entrada de temperatura, existir otra seal para inicializar el sistema poniendo la temperatura actual como mxima y mnima. Para disear el circuito suponga que dispone de comparadores para nmeros de 7 bits en formato signo/magnitud. Realice en primer lugar un diagrama de bloques del circuito y a continuacin describa el circuito en VHDL.

Potrebbero piacerti anche

- Diagrama Electronico Isx PDF Acelerador Tecnología de VehículosDocumento1 paginaDiagrama Electronico Isx PDF Acelerador Tecnología de Vehículosbryanchacon196Nessuna valutazione finora

- Lista de Precios-Stock General MSR Computers 27-12-22Documento58 pagineLista de Precios-Stock General MSR Computers 27-12-22Deivy ErickNessuna valutazione finora

- Construcciones RuralesDocumento9 pagineConstrucciones RuralesMENDOZADEXISNessuna valutazione finora

- CE UD6 Departamento ProduccionDocumento25 pagineCE UD6 Departamento ProduccionPrici Villa FuentesNessuna valutazione finora

- Líneas de Vida Horizontales para Trabajos en AlturaDocumento8 pagineLíneas de Vida Horizontales para Trabajos en Alturateo loeraNessuna valutazione finora

- Ingeniería Ambiental Trabajo FinalDocumento53 pagineIngeniería Ambiental Trabajo Finalbryan ojeda castilloNessuna valutazione finora

- Práctica #6 Potencia y Corrección de Factor de Potencia en Sistemas Trifásicos Balanceados Con Cargas Resistivas - Capacitivas - InductivasDocumento10 paginePráctica #6 Potencia y Corrección de Factor de Potencia en Sistemas Trifásicos Balanceados Con Cargas Resistivas - Capacitivas - InductivasFreddy SalasNessuna valutazione finora

- SensoresDocumento2 pagineSensoresMoisés BoderoNessuna valutazione finora

- Inspeccion VehicularDocumento16 pagineInspeccion VehicularSeguridad Topografia CuajoneNessuna valutazione finora

- Amod FB08 Cuaderno - de - Informes 03 Jhon HaroldDocumento15 pagineAmod FB08 Cuaderno - de - Informes 03 Jhon HaroldJhon AbellanedaNessuna valutazione finora

- Ejecutivo Comercial Oficina - Elias Rosas BlasDocumento2 pagineEjecutivo Comercial Oficina - Elias Rosas BlasRichard AlfaroNessuna valutazione finora

- Bomba de Infusion Infusomat FMS ESDocumento20 pagineBomba de Infusion Infusomat FMS ESSilvia LozanoNessuna valutazione finora

- Tatiana Rueda CVDocumento1 paginaTatiana Rueda CVSaday GuerreroNessuna valutazione finora

- Fichas Técnicas 2023 - 3Documento1 paginaFichas Técnicas 2023 - 3moises mendozaNessuna valutazione finora

- Cinta Transportadora Ejercicio 01Documento2 pagineCinta Transportadora Ejercicio 01Dvsergio97Nessuna valutazione finora

- Clase 12 - Firebase IDocumento62 pagineClase 12 - Firebase IEnergeiaNessuna valutazione finora

- Release-Notes EsDocumento52 pagineRelease-Notes EsAlexis Diaz del RiscoNessuna valutazione finora

- Prueba Evaluacion Soporte Tecnico v2Documento7 paginePrueba Evaluacion Soporte Tecnico v2Ivert CocaNessuna valutazione finora

- Informe de SenalizacionDocumento33 pagineInforme de SenalizacionArnold BiesNessuna valutazione finora

- Plan Estratégico Del SPL de La Joyería de CórdobaDocumento120 paginePlan Estratégico Del SPL de La Joyería de CórdobaMel Ps SzNessuna valutazione finora

- Formulario Material GastableDocumento4 pagineFormulario Material GastableCarla CaraballoNessuna valutazione finora

- Autotransportistas SMLDocumento11 pagineAutotransportistas SMLPercy Axel Cholan RoqueNessuna valutazione finora

- Comando de La Semana 1 TestSSLDocumento5 pagineComando de La Semana 1 TestSSLLuis Alejandro Cáceres FaúndezNessuna valutazione finora

- Compresor Silencioso L HP Ca Pro Cevik Pro 10962651 TechsheetsupDocumento3 pagineCompresor Silencioso L HP Ca Pro Cevik Pro 10962651 TechsheetsupDavid Iglesias SuárezNessuna valutazione finora

- Sistemas de Presurización y Acondicionamiento Del AireDocumento10 pagineSistemas de Presurización y Acondicionamiento Del AiremariaNessuna valutazione finora

- 7919-Texto Del Artículo-10789-1-10-20130221 PDFDocumento18 pagine7919-Texto Del Artículo-10789-1-10-20130221 PDFIsa RodriguezNessuna valutazione finora

- Guia Docente PDFDocumento32 pagineGuia Docente PDFJuliana PérezNessuna valutazione finora

- Yealink Sip t21p E2 Datasheet v81 EspañolDocumento3 pagineYealink Sip t21p E2 Datasheet v81 EspañolErick VargasNessuna valutazione finora

- TDR - Practicante Pre Profesional Oficina Zonal IcaDocumento2 pagineTDR - Practicante Pre Profesional Oficina Zonal IcaGERSON MIGUEL CABELLO RODRIGUEZNessuna valutazione finora

- Sysmac Studio NJ 5 VariablesDocumento8 pagineSysmac Studio NJ 5 VariablesMarcio MifaroNessuna valutazione finora