Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Tarea 1 Lab 2 Elc115

Caricato da

Jorge CarpioCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Tarea 1 Lab 2 Elc115

Caricato da

Jorge CarpioCopyright:

Formati disponibili

Tarea 1- Caractersticas de dispositivos MOSFET.

Subtarea 1A) Voltaje de umbral y parmetros de proceso de dispositivo NMOS.

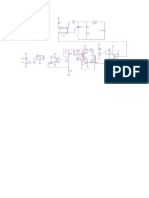

Fig.1 Circuito NMOS

Procedimiento.

a) Armar el circuito de la Fig.1 Pin 14 conectado a VDD y el pin 7 a Vss.

b) Ajustar el valor de VDD de 0 a 10 V DC.

c) Medir el voltaje VDS y la corriente ID y tabular los resultados en una tabla.

Lecturas tomadas para transistor pines 3,4,5,7.

TRANSISTOR NMOS

Vdd[V] VdS[V] Id[mA]

0 0.00 0.00

1 1.00 0.00

2 1.97 0.03

3 2.95 0.44

4 3.86 1.29

5 4.96 2.77

6 5.94 4.47

7 6.92 6.45

8 7.89 8.66

9 8.87 11.02

10 9.84 13.50

Tabla 1

Q1

VDD

CD4007

1

1

2

2

1

2

1

1

2

1 2

1

2

1

2

2

1

2

1

2

=

=

=

=

D

D

DS

D

D

DS

D

D

DS DS

D

D

DS

DS

DS

DS

D

D

i

i

V

i

i

V

Vt

i

i

Vt V Vt V

i

i

Vt V

Vt V

Vt V

Vt V

i

i

d) Graficar las mediciones obtenidas.

e) Calcular el valor del voltaje de umbral Vt y el parmetro de proceso K.

| |

| |

| |

| |

| |

| | | |

2

1

2

1

2

2

2

2

2

1

1

2

2

2

2

1

1

2

2 2

2

1 1

2

) ( ) (

) (

) (

) (

) (

) (

(

=

=

=

=

Vt V

Vt V

i

i

V V

i

V V

i

L

W

K

V V

i

L

W

K

V V

i

V V

L

W

K i

V V

L

W

K i

C K

V V

L

W

C i

DS

DS

D

D

t DS

D

t DS

D

t DS

D

t DS

D

t DS D

t DS D

OX n

t DS OX n D

Voltaje de umbral Vt

2

1

2

2

1

2

1

1

1

1

(

(

(

(

=

D

D

DS

D

D

DS

DS

D

i

i

V

i

i

V

V

i

L

W

K

| |

2

1

2

2

1

2

1

1

1

2

1

1

1

) (

(

(

(

(

(

=

=

D

D

DS

D

D

DS

DS

D

t DS

D

i

i

V

i

i

V

V

i

L

W

K

L

W

K

V V

i

Parmetro de proceso K.

Usando valores medidos de la tabla para NMOS.

Vds1= 4.96 V Id1=2.77mA Vds2=6.92 V Id2=6.45mA

V

x

x

x

x

i

i

V

i

i

V

Vt

D

D

DS

D

D

DS

22 . 1

1

10 77 . 2

10 45 . 6

92 . 6

10 77 . 2

10 45 . 6

96 . 4

1

3

3

3

3

1

2

2

1

2

1

=

2

2

3

3

3

3

3

/ 199 . 0

1

10 77 . 2

10 45 . 6

92 . 6

10 77 . 2

10 45 . 6

96 . 4

96 . 4

10 77 . 2

V mA

x

x

x

x

x

L

W

K =

(

(

(

(

2

1

2

2

1

2

1

1

1

1

(

(

(

(

=

D

D

DS

D

D

DS

DS

D

i

i

V

i

i

V

V

i

L

W

K

f) Son consistentes estos valores de Vt y K(W/L) con las mediciones de otros dos transistores

NMOS en el chip?

Lecturas tomadas para un segundo transistor pines 6, 7, 8.

Tomando los valores:

Vds1= 3.87 V Id1= 1.21mA

Vds2=5.94V Id2= 4.02mA

Tabla 2

V

x

x

x

x

i

i

V

i

i

V

Vt

D

D

DS

D

D

DS

35 . 1

1

10 21 . 1

10 02 . 4

94 . 5

10 21 . 1

10 02 . 4

87 . 3

1

3

3

3

3

1

2

2

1

2

1

=

Voltaje de umbral Vt

2

2

3

3

3

3

3

/ 190 . 0

1

10 21 . 1

10 02 . 4

94 . 5

10 21 . 1

10 02 . 4

87 . 3

87 . 3

10 21 . 1

V mA

x

x

x

x

x

L

W

K =

(

(

(

(

Parmetro de proceso K

Se observa que en ambas mediciones del NMOS existe consistencia en los valores de Vt y

K(W/L).

TRANSISTOR NMOS

Vdd[V] Vds[V] Id[mA]

0 0.00 0.00

1 1.00 0.00

2 1.97 0.03

3 2.95 0.43

4 3.87 1.21

5 4.97 2.53

6 5.94 4.02

7 6.92 5.73

8 7.90 7.63

9 8.88 9.64

10 9.86 11.76

Subtarea 1B) Voltaje de umbral y parmetros de proceso de dispositivo PMOS.

Fig.2 Circuito PMOS

Procedimiento.

a) Armar el circuito de la Fig.1 Pin 14 conectado a VDD y el pin 7 a Vss.

b) Ajustar el valor de VDD de 0 a 10 V DC.

c) Medir el voltaje VDS y la corriente ID y tabular los resultados en una tabla.

Lecturas tomadas para transistor pines 1,2,3.

TRANSISTOR PMOS

Vdd[V] VdS[V] Id[mA]

0.077 0.00 0

1 0.99 0.781

2 2.00 3.05

3 2.99 5.25

4 3.99 7.51

5 4.99 9.8

6 5.41 12.11

7 6.98 14.47

8 7.97 16.83

9 8.98 19.27

10 9.97 23.2

Tabla 3

VDD

Q2

CD4007

2

1

2

2

1

2

1

1

1

1

(

(

(

(

=

D

D

DS

D

D

DS

DS

D

i

i

V

i

i

V

V

i

L

W

K

d) Graficar las mediciones obtenidas.

e) Calcular el valor del voltaje de umbral Vt y el parmetro de proceso K.

Usando valores medidos de la tabla 3 para PMOS.

Vds1= 4.99 V Id1=9.8mA Vds2=5.41 V Id2=12.11mA

V

x

x

x

x

i

i

V

i

i

V

Vt

D

D

DS

D

D

DS

23 . 1

1

10 8 . 9

10 11 . 12

41 . 5

10 8 . 9

10 11 . 12

99 . 4

1

3

3

3

3

1

2

2

1

2

1

=

Voltaje de umbral

2

2

3

3

3

3

3

/ 69 . 0

1

10 8 . 9

10 11 . 12

41 . 5

10 8 . 9

10 11 . 12

99 . 4

99 . 4

10 8 . 9

V mA

x

x

x

x

x

L

W

K =

(

(

(

(

Parmetro K

f) Son consistentes estos valores de Vt y K(W/L) con las mediciones de otros dos transistores

NMOS en el chip?

Lecturas tomadas para un segundo transistor pines 6,13,14.

Tomando los valores:

Vds1=4.87V Id1= 8.88mA

Vds2=5.43V Id2= 12.19mA

Tabla 4

V

x

x

x

x

i

i

V

i

i

V

Vt

D

D

DS

D

D

DS

6 . 1

1

10 88 . 8

10 19 . 12

43 . 5

10 88 . 8

10 19 . 12

87 . 4

1

3

3

3

3

1

2

2

1

2

1

=

Voltaje de umbral Vt

TRANSISTOR PMOS

Vdd[V] VdS[V] Id[mA]

0.077 0.00 0

1 0.99 0.782

2 2.00 3.1

3 2.99 5.24

4 3.99 7.51

5 4.87 8.88

6 5.43 12.19

7 6.98 14.47

8 7.97 16.83

9 8.98 19.27

10 9.97 23.2

2

1

2

2

1

2

1

1

1

1

(

(

(

(

=

D

D

DS

D

D

DS

DS

D

i

i

V

i

i

V

V

i

L

W

K

2

2

3

3

3

3

3

/ 83 . 0

1

10 88 . 8

10 19 . 12

43 . 5

10 88 . 8

10 19 . 12

87 . 4

87 . 4

10 88 . 8

V mA

x

x

x

x

x

L

W

K =

(

(

(

(

Parmetro de proceso K

Se observa que en ambas mediciones del PMOS existe consistencia muy cercana en los

valores de Vt y K(W/L). Las diferencias se atribuyen a las condiciones de temperatura y la

precisin de los instrumentos de medicin a la hora de efectuar la prctica.

Potrebbero piacerti anche

- Problemas resueltos de Hidráulica de CanalesDa EverandProblemas resueltos de Hidráulica de CanalesValutazione: 4.5 su 5 stelle4.5/5 (7)

- Armónicas en Sistemas Eléctricos IndustrialesDa EverandArmónicas en Sistemas Eléctricos IndustrialesValutazione: 4.5 su 5 stelle4.5/5 (12)

- Dinámica De Fluidos Computacional Para IngenierosDa EverandDinámica De Fluidos Computacional Para IngenierosValutazione: 4 su 5 stelle4/5 (1)

- Letra de Cantos de VillancicosDocumento6 pagineLetra de Cantos de VillancicosJorge Carpio100% (1)

- Sistemas de Puesta A TierraDocumento41 pagineSistemas de Puesta A TierraFernando Nuno100% (13)

- Informe 3 Jfet y MosfetDocumento8 pagineInforme 3 Jfet y MosfetapusiqNessuna valutazione finora

- GUÍA DE LABORATORIO No 1 - Elementos de Circuito en Corriente AlternaDocumento15 pagineGUÍA DE LABORATORIO No 1 - Elementos de Circuito en Corriente AlternaJulioNessuna valutazione finora

- Problemas FETDocumento8 pagineProblemas FETIgreda Rojas Luis0% (1)

- Métodos Matriciales para ingenieros con MATLABDa EverandMétodos Matriciales para ingenieros con MATLABValutazione: 5 su 5 stelle5/5 (1)

- Aes - Manual ElectricistasDocumento40 pagineAes - Manual ElectricistasPablo Galdamez100% (2)

- Universidad Ricardo PalmaDocumento7 pagineUniversidad Ricardo PalmaAlejandroGersonGayosoAlfaroNessuna valutazione finora

- Requerimientos Instalacion ElectricaDocumento14 pagineRequerimientos Instalacion ElectricasalgoraNessuna valutazione finora

- Transistores de Efecto de CampoDocumento12 pagineTransistores de Efecto de Camponmmanya_973148340Nessuna valutazione finora

- 5 Ejercicios MOSFETDocumento8 pagine5 Ejercicios MOSFETAndres Reyes33% (3)

- Polarización de Transistores JFet yMosFetDocumento10 paginePolarización de Transistores JFet yMosFetByron CabreraNessuna valutazione finora

- Informe 4 - ML831Documento16 pagineInforme 4 - ML831Cesar VeraNessuna valutazione finora

- Ejercicios de TransistoresDocumento10 pagineEjercicios de TransistoresGerson ContrerasNessuna valutazione finora

- Folleto Del Ing. RubioDocumento269 pagineFolleto Del Ing. RubioCarlos Duran Salazar ✅Nessuna valutazione finora

- Electronica II-problemas Resueltos y Propuestos 7.1Documento242 pagineElectronica II-problemas Resueltos y Propuestos 7.1MaRiuxi Vaccaro100% (4)

- Informe Electrónica IIDocumento8 pagineInforme Electrónica IIOskitar UrbixNessuna valutazione finora

- Práctica FETDocumento10 paginePráctica FETPepe El Toro SanchezNessuna valutazione finora

- Practica 5Documento10 paginePractica 5geovannyNessuna valutazione finora

- 1.1 Circuitos Rectificadores de Onda Completa (Steven)Documento10 pagine1.1 Circuitos Rectificadores de Onda Completa (Steven)Alejo PtNessuna valutazione finora

- Prepa 10Documento4 paginePrepa 10Jorge MiñoNessuna valutazione finora

- Electronica Univ Cantabria-1Documento7 pagineElectronica Univ Cantabria-1jjurado183Nessuna valutazione finora

- Ejercicios 04 FetDocumento8 pagineEjercicios 04 FetKevin Cruz CcochaNessuna valutazione finora

- Prac 1Documento7 paginePrac 1Leo Ormaza SiguenzaNessuna valutazione finora

- Guia N°9 JfetDocumento7 pagineGuia N°9 JfetJonathan MartinezNessuna valutazione finora

- D09Documento9 pagineD09Benji Martell BernardoNessuna valutazione finora

- Laboratorio N°1-Condori Apaza Pavel EduardoDocumento13 pagineLaboratorio N°1-Condori Apaza Pavel EduardopavelNessuna valutazione finora

- Laboratorio #3 (Circuitos Con Transistores)Documento20 pagineLaboratorio #3 (Circuitos Con Transistores)Neko FireNessuna valutazione finora

- Informe 7 - C.Electronicos IDocumento11 pagineInforme 7 - C.Electronicos ILuis PLNessuna valutazione finora

- Trabajo Problemas Propuestos SemiconductoresDocumento10 pagineTrabajo Problemas Propuestos SemiconductoresDave ChecaNessuna valutazione finora

- Informe Laboratorio N08Documento6 pagineInforme Laboratorio N08Oscar AyalaNessuna valutazione finora

- CP Dispo 6Documento23 pagineCP Dispo 6Adrián CastroNessuna valutazione finora

- Ex. Final Ee532 - Fiee UniDocumento7 pagineEx. Final Ee532 - Fiee UniDavidNessuna valutazione finora

- Eb112 Student SPNDocumento64 pagineEb112 Student SPNFernandoNessuna valutazione finora

- Temas 6 y 7 - EjerciciosDocumento7 pagineTemas 6 y 7 - EjerciciosJuan RomanNessuna valutazione finora

- Práctica n3 Sem I-2018-1Documento5 paginePráctica n3 Sem I-2018-1DivarNessuna valutazione finora

- Lab Citro 1-2Documento6 pagineLab Citro 1-2JesusVilcaYepezNessuna valutazione finora

- Análisis de Un Amplificador OperacionalDocumento18 pagineAnálisis de Un Amplificador OperacionalFelipe GomezNessuna valutazione finora

- AE Tarea1 1T 2023Documento6 pagineAE Tarea1 1T 2023Jacinto OrtizNessuna valutazione finora

- Circuitos Electronicos 2 Labo1Documento9 pagineCircuitos Electronicos 2 Labo1ESPINOZA MONTESINOS ANGEL SAMUELNessuna valutazione finora

- Circuitos ElectronicosDocumento8 pagineCircuitos ElectronicosCesar GuuzNessuna valutazione finora

- 5 Ejercicios MOSFETDocumento8 pagine5 Ejercicios MOSFETfernandoalex16Nessuna valutazione finora

- GUÍA DE LABORATORIO No 1 - Elementos de Circuito en Corriente AlternaDocumento14 pagineGUÍA DE LABORATORIO No 1 - Elementos de Circuito en Corriente AlternaJulioNessuna valutazione finora

- Practica4 Amplificacion Ordoñez-Estrada-AbigailDocumento10 paginePractica4 Amplificacion Ordoñez-Estrada-AbigailTirone GonzálezNessuna valutazione finora

- L 01 MultiEtapaDocumento8 pagineL 01 MultiEtapaFlavio AndreéNessuna valutazione finora

- Lab - Circuito CDocumento6 pagineLab - Circuito CRENATO JUDA POLO AÑORGANessuna valutazione finora

- Universidad Nacional de Ingenieria Facultad de Ingeniera MecanicaDocumento23 pagineUniversidad Nacional de Ingenieria Facultad de Ingeniera MecanicaJhonny CruzadoNessuna valutazione finora

- Laboratorio 1 Adquisicion de DatosDocumento6 pagineLaboratorio 1 Adquisicion de DatosVictor RodriguezNessuna valutazione finora

- CS ElectronicaDocumento12 pagineCS ElectronicaMartin CazunNessuna valutazione finora

- Laboratorio #5 Fundamentos ElectronicosDocumento11 pagineLaboratorio #5 Fundamentos ElectronicosSamuel RodriguezNessuna valutazione finora

- PRÁCTICA DE LABORATORIO No 1Documento5 paginePRÁCTICA DE LABORATORIO No 1Elver GarciaNessuna valutazione finora

- Guia 4Documento5 pagineGuia 4diego.djezairNessuna valutazione finora

- Deflexion ElectricaDocumento4 pagineDeflexion Electricabrayan cardenas0% (1)

- Practica No.8 (El Integrador y Derivador)Documento5 paginePractica No.8 (El Integrador y Derivador)Alexis MuñozNessuna valutazione finora

- Diseño P3Documento18 pagineDiseño P3Luis EncinasNessuna valutazione finora

- 15 Ejercicios DispoDocumento18 pagine15 Ejercicios DispoEycol De La CruzNessuna valutazione finora

- Ejercicios de BJT y Fet ResueltosDocumento14 pagineEjercicios de BJT y Fet Resueltosangel_186873767100% (4)

- Practica 3 Circuitos ElectronicosDocumento7 paginePractica 3 Circuitos ElectronicosAlejandro BadilloNessuna valutazione finora

- Problemas de Circuitos ElectronicosDocumento8 pagineProblemas de Circuitos ElectronicosjeanNessuna valutazione finora

- Electronica Teoria de Circuitos BoylestadDocumento11 pagineElectronica Teoria de Circuitos BoylestadBolivar Gavilanez AcostaNessuna valutazione finora

- Introducción a la dinámica computacional de fluidos (CFD) en Ingeniería Química.Da EverandIntroducción a la dinámica computacional de fluidos (CFD) en Ingeniería Química.Nessuna valutazione finora

- Control neuronal y difuso para sistemas fotovoltaicosDa EverandControl neuronal y difuso para sistemas fotovoltaicosNessuna valutazione finora

- Grapas para Rieles Strut PDFDocumento1 paginaGrapas para Rieles Strut PDFJorge CarpioNessuna valutazione finora

- Diagrama Implementado Cerradura DigitalDocumento1 paginaDiagrama Implementado Cerradura DigitalJorge CarpioNessuna valutazione finora

- Folleto OI Electricos V12Documento8 pagineFolleto OI Electricos V12Jorge CarpioNessuna valutazione finora

- Calculo de Corriente de Un Transformador de Distribucion Monofasico PDFDocumento1 paginaCalculo de Corriente de Un Transformador de Distribucion Monofasico PDFJorge CarpioNessuna valutazione finora

- Tablas de Flip FlopsDocumento1 paginaTablas de Flip FlopsJorge CarpioNessuna valutazione finora

- CostosDocumento4 pagineCostosJorge CarpioNessuna valutazione finora

- BroshureDocumento2 pagineBroshureJorge CarpioNessuna valutazione finora

- Tierra en MaquinasDocumento3 pagineTierra en MaquinasClaudio CondoriNessuna valutazione finora

- Analisis de Costo de MaterialesDocumento5 pagineAnalisis de Costo de MaterialesJorge CarpioNessuna valutazione finora

- Esquema Nacional de Vacunacion El Salvador 2020Documento1 paginaEsquema Nacional de Vacunacion El Salvador 2020Jorge CarpioNessuna valutazione finora

- Arco ElectricoDocumento11 pagineArco ElectricoAriel CaresNessuna valutazione finora

- Capacitor de MarchaDocumento13 pagineCapacitor de Marchaocaolg73Nessuna valutazione finora

- CostosDocumento4 pagineCostosJorge CarpioNessuna valutazione finora

- Adviento 2016Documento11 pagineAdviento 2016Jorge CarpioNessuna valutazione finora

- MonseñorDocumento1 paginaMonseñorJorge CarpioNessuna valutazione finora

- Control de Potencia Triac y RTDDocumento1 paginaControl de Potencia Triac y RTDJorge CarpioNessuna valutazione finora

- CantosDocumento6 pagineCantosJorge CarpioNessuna valutazione finora

- Novena de A. Y Bailarán en Familia.Documento23 pagineNovena de A. Y Bailarán en Familia.Jorge CarpioNessuna valutazione finora

- CS en LLTTDocumento19 pagineCS en LLTTFJRVNessuna valutazione finora

- Diseño de Controlador Tipo PIDDocumento10 pagineDiseño de Controlador Tipo PIDJorge CarpioNessuna valutazione finora

- Instrumentacion RTDDocumento1 paginaInstrumentacion RTDJorge CarpioNessuna valutazione finora

- Secundaria y Bachillerato - Repara - Dehonianos - Oraciones 1º Al 3º Domingo de CuaresmaDocumento20 pagineSecundaria y Bachillerato - Repara - Dehonianos - Oraciones 1º Al 3º Domingo de CuaresmaJorge CarpioNessuna valutazione finora

- Tabla Convertidor DACDocumento3 pagineTabla Convertidor DACJorge CarpioNessuna valutazione finora

- Indiceshorarios (I) AulaDocumento4 pagineIndiceshorarios (I) AulaEfrain PerezNessuna valutazione finora

- Indiceshorarios (I) AulaDocumento4 pagineIndiceshorarios (I) AulaEfrain PerezNessuna valutazione finora

- Plano Electrico de La Casa-ModelDocumento1 paginaPlano Electrico de La Casa-ModelJorge CarpioNessuna valutazione finora

- Indiceshorarios (I) AulaDocumento4 pagineIndiceshorarios (I) AulaEfrain PerezNessuna valutazione finora

- Ejercicios FemDocumento20 pagineEjercicios FemDIANA CAROLINA LONDOÑO BUITRAGO100% (1)

- Practica 1 y 2 de FisicaDocumento6 paginePractica 1 y 2 de FisicaKenyi Erasmo Garcia ChilenoNessuna valutazione finora

- Actividad - Retie y Seguridad Electrica - CuestionarioDocumento5 pagineActividad - Retie y Seguridad Electrica - CuestionarioCesar Carlos Caballero CardenasNessuna valutazione finora

- Filtro Pasa AltasDocumento3 pagineFiltro Pasa AltasJavier CastañedaNessuna valutazione finora

- ENLACE QUÍMICO 2º Bachill 2010-2011Documento24 pagineENLACE QUÍMICO 2º Bachill 2010-2011Adolfo del CachoNessuna valutazione finora

- Aisladores: Qué Son, para Qué Sirven, Tipos Y ClasificaciónDocumento22 pagineAisladores: Qué Son, para Qué Sirven, Tipos Y ClasificaciónGio ZuñigaNessuna valutazione finora

- Leyes de KirchhoffDocumento5 pagineLeyes de KirchhoffRodrigo NolascoNessuna valutazione finora

- Practica 5 Amplificador DerivadorDocumento15 paginePractica 5 Amplificador DerivadorCarlos BalanNessuna valutazione finora

- Aisladores para SubestacionesDocumento76 pagineAisladores para SubestacionesJUAN PABLO100% (9)

- Tutorial IEEE Protección de Generadores SincrónicosDocumento88 pagineTutorial IEEE Protección de Generadores SincrónicosFreddy EscorzaNessuna valutazione finora

- Catalogo General - Lideres en Sistemas de Monitoreo de Subestaciones ElectricasDocumento25 pagineCatalogo General - Lideres en Sistemas de Monitoreo de Subestaciones ElectricasMac FloresNessuna valutazione finora

- Dosificación de Hormigón ConvencionalDocumento43 pagineDosificación de Hormigón ConvencionalDavid Rojas100% (2)

- Practica Lab1-Circuitos Marlon ParadaDocumento4 paginePractica Lab1-Circuitos Marlon ParadaMarlon Esteban Parada BolivarNessuna valutazione finora

- CARTILLA 1 2021 Modalidad ElectronicaDocumento20 pagineCARTILLA 1 2021 Modalidad ElectronicabrayanNessuna valutazione finora

- Práctica 7 Thevenin y NortonDocumento5 paginePráctica 7 Thevenin y NortonKevin Esteban SaenzNessuna valutazione finora

- Bp125-n Jac - Bcolllk - Bpanllk Mt8551 0402 6701 Sony OpuDocumento85 pagineBp125-n Jac - Bcolllk - Bpanllk Mt8551 0402 6701 Sony OpuSilviana Andreina Rangel Olaechea100% (2)

- Circuitos Electricos EquivalentesDocumento10 pagineCircuitos Electricos EquivalentesGeo Del Cid100% (1)

- 2020-2021 - Problemas - Hoja 8 - Introducción A Los Semiconductores (Enunciados)Documento2 pagine2020-2021 - Problemas - Hoja 8 - Introducción A Los Semiconductores (Enunciados)FritzNessuna valutazione finora

- Análisis de Circuitos RLC en ParaleloDocumento8 pagineAnálisis de Circuitos RLC en ParaleloAlexaNessuna valutazione finora

- Nte Inen 3046Documento25 pagineNte Inen 3046oscar16780Nessuna valutazione finora

- Cap 7 TransitoriosDocumento35 pagineCap 7 TransitoriosisaacNessuna valutazione finora

- Protector de Voltaje 120vac 60 HZ Con LM358N PDFDocumento1 paginaProtector de Voltaje 120vac 60 HZ Con LM358N PDFFreddyTorresS100% (4)

- Sistema de Puesta A TierraDocumento45 pagineSistema de Puesta A TierraAntonio Torres bautistaNessuna valutazione finora

- 3 1 Conductores PDFDocumento14 pagine3 1 Conductores PDFAlexander Solar AguilarNessuna valutazione finora

- Informe de Mantenimiento Sechura.Documento14 pagineInforme de Mantenimiento Sechura.Augusto More LopezNessuna valutazione finora

- Guia de La Prueba de Aislamiento ElectricoDocumento33 pagineGuia de La Prueba de Aislamiento Electricojuan galvanNessuna valutazione finora