Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Instruction Set

Caricato da

anuradha_sreekanthDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Instruction Set

Caricato da

anuradha_sreekanthCopyright:

Formati disponibili

TMS320C5x, TMS320LC5x DIGITAL SIGNAL PROCESSORS

SPRS030A APRIL 1995 REVISED APRIL 1996

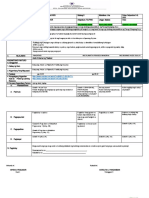

instruction set summary (continued) Table 6. Opcode Symbols

SYMBOL A ACC ACCB ARX BITX BMAR DBMR I II...II INTM INTR# N PREG PROG RPTC SHF, SHFT TC Address Accumulator Accumulator buffer Auxiliary register value (0 7) 4-bit field specifies which bit to test for the BIT instruction Block-move address register Dynamic bit-manipulation register Addressing-mode bit Immediate operand value Interrupt-mode flag bit Interrupt vector number Field for the XC instruction, indicating the number of instructions (one or two) to execute conditionally Product register Program memory Repeat counter 3/4 bit shift value Test-control bit Two bits used by the conditional execution instructions to represent the conditions TC, NTC, and BIO T P Meaning 00 BIO low 01 TC = 1 10 TC = 0 11 None of the above conditions Temporary register n (n = 0, 1, or 2) 4-bit field representing the following conditions: Z: ACC = 0 L: ACC < 0 V: Overflow C: Carry A conditional instruction contains two of these 4-bit fields. The 4-LSB field of the instruction is a 4-bit mask field. A 1 in the corresponding mask bit indicates that the condition is being tested. The second 4-bit field (bits 4 7) indicates the state of the conditions designated by the mask bits as being tested. For example, to test for ACC 0, the Z and L fields are set while the V and C fields are not set. The next 4-bit field contains the state of the conditions to test. The Z field is set to indicate testing the condition ACC = 0, and the L field is reset to indicate testing the condition ACC 0. The conditions possible with these 8 bits are shown in the BCND, CC, and XC instructions. To determine if the conditions are met, the 4-LSB bit mask is ANDed with the conditions. If any bits are set, the conditions are met. DESCRIPTION

TP

TREGn

ZLVC

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

37

TMS320C5x, TMS320LC5x DIGITAL SIGNAL PROCESSORS

SPRS030A APRIL 1995 REVISED APRIL 1996

instruction set summary (continued) Table 7. TMS320C5x Instruction Set Opcodes

ACCUMULATOR MEMORY REFERENCE INSTRUCTIONS INSTRUCTION Absolute value of ACC Add ACCB to ACC with carry Add to ACC with shift Add to low ACC short immediate Add to ACC long immediate with shift Add to ACC with shift of 16 Add ACCB to ACC Add to ACC with carry Add to low ACC with sign extension suppressed Add to ACC with shift specified by TREG1 [3 0] AND ACC with data value AND with ACC long immediate with shift AND with ACC long immediate with shift of 16 AND ACCB with ACC Barrel shift ACC right Complement ACC Store ACC in ACCB if ACC > ACCB Store ACC in ACCB if ACC< ACCB Exchange ACCB with ACC Load ACC with ACCB Load ACC with shift Load ACC long immediate with shift Load ACC with shift of 16 Load low word of ACC with immediate Load low word of ACC Load ACC with shift specified by TREG1 [3 0] Load ACCL with memory-mapped register Negate ACC Normalize ACC OR ACC with data value OR with ACC long immediate with shift OR with ACC long immediate with shift of 16 OR ACCB with ACC Rotate ACC 1 bit left Rotate ACCB and ACC left Rotate ACC 1 bit right Rotate ACCB and ACC right Store ACC in ACCB Store high ACC with shift Store low ACC with shift Store ACCL to memory-mapped register Shift ACC 16 bits right if TREG1 [4] = 0 Shift ACC0ACC15 right as specified by TREG1 [3 0] Subtract ACCB from ACC Subtract ACCB from ACC with borrow Shift ACC 1 bit left Shift ACCB and ACC left Shift ACC 1 bit right Shift ACCB and ACC right Subtract from ACC with shift Subtract from ACC with shift of 16 Subtract from ACC short immediate Subtract from ACC long immediate with shift MNEMONIC ABS ADCB ADD ADD ADD ADD ADDB ADDC ADDS ADDT AND AND AND ANDB BSAR CMPL CRGT CRLT EXAR LACB LACC LACC LACC LACL LACL LACT LAMM NEG NORM OR OR OR ORB ROL ROLB ROR RORB SACB SACH SACL SAMM SATH SATL SBB SBBB SFL SFLB SFR SFRB SUB SUB SUB SUB 1011 1011 0010 1011 1011 0110 1011 0110 0110 0110 0110 1011 1011 1011 1011 1011 1011 1011 1011 1011 0001 1011 0110 1011 0110 0110 0000 1011 1010 0110 1011 1011 1011 1011 1011 1011 1011 1011 1001 1001 1000 1011 1011 1011 1011 1011 1011 1011 1011 0011 0110 1011 1011 OPCODE 1110 1110 SHFT 1000 1111 0001 1110 0000 0010 0011 1110 1111 1110 1110 1111 1110 1110 1110 1110 1110 SHFT 1111 1010 1001 1001 1011 1000 1110 0000 1101 1111 1110 1110 1110 1110 1110 1110 1110 1SHF 0SHF 1000 1110 1110 1110 1110 1110 1110 1110 1110 SHFT 0101 1010 1111 0000 0001 IAAA IIII 1001 IAAA 0001 IAAA IAAA IAAA IAAA 1011 1000 0001 1110 0000 0001 0001 0001 0001 IAAA 1000 IAAA IIII IAAA IAAA IAAA 0000 IAAA IAAA 1100 1000 0001 0000 0001 0000 0001 0001 IAAA IAAA IAAA 0101 0101 0001 0001 0000 0001 0000 0001 IAAA IAAA IIII 1010 0000 0001 AAAA IIII SHFT AAAA 0000 AAAA AAAA AAAA AAAA SHFT 0001 0010 SHFT 0001 1011 1100 1101 1111 AAAA SHFT AAAA IIII AAAA AAAA AAAA 0010 AAAA AAAA SHFT 0010 0011 1100 0100 1101 0101 1110 AAAA AAAA AAAA 1010 1011 1000 1001 1001 0110 1010 0111 AAAA AAAA IIII SHFT WORDS 1 1 1 1 2 1 1 1 1 1 1 2 2 1 1 1 1 1 1 1 1 2 1 1 1 1 1 1 1 1 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 2 CYCLES 1 1 1 1 2 1 1 1 1 1 1 2 2 1 1 1 1 1 1 1 1 2 1 1 1 1 1 or 2 1 1 1 2 2 1 1 1 1 1 1 1 1 1 or 2 1 1 1 1 1 1 1 1 1 1 1 2

38

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

TMS320C5x, TMS320LC5x DIGITAL SIGNAL PROCESSORS

SPRS030A APRIL 1995 REVISED APRIL 1996

instruction set summary (continued) Table 7. TMS320C5x Instruction Set Opcodes (Continued)

ACCUMULATOR MEMORY REFERENCE INSTRUCTIONS (CONTINUED) INSTRUCTION Subtract from ACC with borrow Conditional subtract Subtract from ACC with sign extension suppressed Subtract from ACC, shift specified by TREG1 [3 0] XOR ACC with data value XOR with ACC long immediate with shift XOR with ACC long immediate with shift of 16 XOR ACCB with ACC Zero ACC, load high ACC with rounding Zero ACC and product register MNEMONIC SUBB SUBC SUBS SUBT XOR XOR XOR XORB ZALR ZAP 0110 0000 0110 0110 0110 1011 1011 1011 0110 1011 OPCODE 0100 1010 0110 0111 1100 1111 1110 1110 1000 1110 IAAA IAAA IAAA IAAA IAAA 1101 1000 0001 IAAA 0101 AAAA AAAA AAAA AAAA AAAA SHFT 0011 1010 AAAA 1001 WORDS 1 1 1 1 1 2 2 1 1 1 CYCLES 1 1 1 1 1 2 2 1 1 1

AUXILIARY REGISTERS AND DATA PAGE POINTER INSTRUCTIONS INSTRUCTION Add to AR short immediate Compare AR with CMPR Load AR from addressed data Load AR short immediate Load AR long immediate Load data page pointer with addressed data Load data page immediate Modify auxiliary register Store AR to addressed data Subtract from AR short immediate MNEMONIC ADRK CMPR LAR LAR LAR LDP LDP MAR SAR SBRK 0111 1011 0000 1011 1011 0000 1011 1000 1000 0111 OPCODE 1000 1111 0ARX 0ARX 1111 1101 110I 1011 0ARX 1100 IIII 0100 IAAA IIII 0000 IAAA IIII IAAA IAAA IIII IIII 01CM AAAA IIII 1ARX AAAA IIII AAAA AAAA IIII WORDS 1 1 1 1 2 1 1 1 1 1 CYCLES 1 1 1 1 2 2 2 1 1 1

BRANCH INSTRUCTIONS INSTRUCTION Branch unconditional with AR update Branch addressed by ACC Branch addressed by ACC delayed Branch AR 0 with AR update Branch AR 0 with AR update delayed Branch conditional Branch conditional delayed Branch unconditional with AR update delayed Call subroutine addressed by ACC Call subroutine addressed by ACC delayed Call unconditional with AR update Call unconditional with AR update delayed Call conditional Call conditional delayed Software interrupt Nonmaskable interrupt Return Return conditional Return conditionally, delayed Return, delayed Return from interrupt with enable Return from interrupt Trap Execute next one or two INST on condition MNEMONIC B BACC BACCD BANZ BANZD BCND BCNDD BD CALA CALAD CALL CALLD CC CCD INTR NMI RET RETC RETCD RETD RETE RETI TRAP XC 0111 1011 1011 0111 0111 1110 1111 0111 1011 1011 0111 0111 1110 1111 1011 1011 1110 1110 1111 1111 1011 1011 1011 111N OPCODE 1001 1110 1110 1011 1111 00TP 00TP 1101 1110 1110 1010 1110 10TP 10TP 1110 1110 1111 11TP 11TP 1111 1110 1110 1110 01TP 1AAA 0010 0010 1AAA 1AAA ZLVC ZLVC 1AAA 0011 0011 1AAA 1AAA ZLVC ZLVC 011 I 0101 0000 ZLVC ZLVC 0000 0011 0011 0101 ZLVC AAAA 0000 0001 AAAA AAAA ZLVC ZLVC AAAA 0000 1101 AAAA AAAA ZLVC ZLVC NTR# 0010 0000 ZLVC ZLVC 0000 1010 1000 0001 ZLVC WORDS 2 1 1 2 2 2 2 2 1 1 2 2 2 2 1 1 1 1 1 1 1 1 1 1 CYCLES 4 4 2 2 or 4 2 2 or 4 2 2 4 2 4 2 2 or 4 2 4 4 4 2 or 4 2 2 4 4 4 1

instruction set summary (continued) Table 7. TMS320C5x Instruction Set Opcodes (Continued)

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

39

TMS320C5x, TMS320LC5x DIGITAL SIGNAL PROCESSORS

SPRS030A APRIL 1995 REVISED APRIL 1996

I/O AND DATA MEMORY OPERATIONS INSTRUCTION Block move from data to data memory Block move data to data DEST long immediate Block move data to data with source in BMAR Block move data to data with DEST in BMAR Block move data to PROG with DEST in BMAR Block move from program to data memory Block move PROG to data with source in BMAR Data move in data memory Input external access Load memory-mapped register Out external access Store memory-mapped register Table read Table write INSTRUCTION AND DBMR with data value AND long immediate with data value Compare DBMR to data value Compare data with long immediate OR DBMR to data value OR long immediate with data value Store long immediate to data XOR DBMR to data value XOR long immediate with data value INSTRUCTION Add PREG to ACC Load high PREG Load TREG0 Load TREG0 and accumulate previous product Load TREG0, accumulate previous product, and move data Load TREG0 and load ACC with PREG Load TREG0 and subtract previous product Multiply/accumulate Multiply/accumulate with data shift Mult/ACC w/source ADRS in BMAR and DMOV Mult/ACC with source address in BMAR Multiply data value times TREG0 Multiply TREG0 by 13-bit immediate Multiply TREG0 by long immediate Multiply TREG0 by data, add previous product Multiply TREG0 by data, ACC PREG Multiply unsigned data value times TREG0 Load ACC with product register Subtract product from ACC Store high product register Store low product register Set PREG shift count Data to TREG0, square it, add PREG to ACC Data to TREG0, square it, ACC PREG Zero product register MNEMONIC BLDD BLDD BLDD BLDD BLDP BLPD BLPD DMOV IN LMMR OUT SMMR TBLR TBLW MNEMONIC APL APL CPL CPL OPL OPL SPLK XPL XPL MNEMONIC APAC LPH LT LTA LTD LTP LTS MAC MACD MADD MADS MPY MPY MPY MPYA MPYS MPYU PAC SPAC SPH SPL SPM SQRA SQRS ZPR 1011 0111 0111 0111 0111 0111 0111 1010 1010 1010 1010 0101 110I 1011 0101 0101 0101 1011 1011 1000 1000 1011 0101 0101 1011 0101 0101 0101 0101 0101 0101 1010 0101 0101 1010 1010 1010 1010 0101 1010 1010 0111 1010 1000 0000 0000 1010 1010 OPCODE 1000 1001 1100 1101 0111 0101 0100 0111 1111 1001 1100 1001 0110 0111 IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA WORDS 2 2 1 1 1 2 1 1 2 2 2 2 1 1 WORDS AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA 1 2 1 2 1 2 2 1 2 WORDS 0100 AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA AAAA IIII 0000 AAAA AAAA AAAA 0011 0101 AAAA AAAA 00PM AAAA AAAA 1000 1 1 1 1 1 1 1 1 2 2 1 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 CYCLES 3 3 2 2 2 3 2 1 2 2 or 3 3 2 or 3 3 3 CYCLES 1 2 1 2 1 2 2 1 2 CYCLES 1 1 1 1 1 1 1 1 3 3 3 3 1 1 2 1 1 1 1 1 1 1 1 1 1 1

PARALLEL LOGIC UNIT INSTRUCTIONS OPCODE 1010 1110 1011 1111 1001 1101 1110 1000 1100 IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA

T REGISTER, P REGISTER, AND MULTIPLY INSTRUCTIONS OPCODE 1110 0101 0011 0000 0010 0001 0100 0010 0011 1011 1010 0100 IIII 1110 0000 0001 0101 1110 1110 1101 1100 1111 0010 0011 1110 0000 IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IAAA IIII 1000 IAAA IAAA IAAA 0000 0000 IAAA IAAA 0000 IAAA IAAA 0101

40

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

TMS320C5x, TMS320LC5x DIGITAL SIGNAL PROCESSORS

SPRS030A APRIL 1995 REVISED APRIL 1996

instruction set summary (continued) Table 7. TMS320C5x Instruction Set Opcodes (Continued)

CONTROL INSTRUCTIONS INSTRUCTION Test bit specified immediate Test bit in data value as specified by TREG2 [3 0] Reset overflow mode Reset sign extension mode Reset hold mode Reset TC bit Reset carry Reset CNF bit Reset INTM bit Reset XF pin Idle Idle until interrupt low-power mode Load status register 0 Load status register 1 No operation Pop PC stack to low ACC Pop stack to data memory Push data memory value onto PC stack Push low ACC to PC stack Repeat instruction as specified by data Repeat next INST specified by long immediate Repeat INST specified by short immediate Block repeat Clear ACC/PREG and repeat next INST long immediate Set overflow mode Set sign extension mode Set hold mode Set TC bit Set carry Set XF pin high Set CNF bit Set INTM bit Store status register 0 Store status register 1 MNEMONIC BIT BITT CLRC CLRC CLRC CLRC CLRC CLRC CLRC CLRC IDLE IDLE2 LST LST NOP POP POPD PSHD PUSH RPT RPT RPT RPTB RPTZ SETC SETC SETC SETC SETC SETC SETC SETC SST SST 0100 0110 1011 1011 1011 1011 1011 1011 1011 1011 1011 1011 0000 0000 1000 1011 1000 0111 1011 0000 1011 1011 1011 1011 1011 1011 1011 1011 1011 1011 1011 1011 1000 1000 OPCODE BITX 1111 1110 1110 1110 1110 1110 1110 1110 1110 1110 1110 1110 1111 1011 1110 1010 0110 1110 1011 1110 1011 1110 1110 1110 1110 1110 1110 1110 1110 1110 1110 1110 1111 IAAA IAAA 0100 0100 0100 0100 0100 0100 0100 0100 0010 0010 IAAA IAAA 0000 0011 IAAA IAAA 0011 IAAA 1100 IIII 1100 1100 0100 0100 0100 0100 0100 0100 0100 0100 IAAA IAAA AAAA AAAA 0010 0110 1000 1010 1110 0100 0000 1100 0010 0011 AAAA AAAA 0000 0010 AAAA AAAA 1100 AAAA 0100 IIII 0110 0101 0011 0111 1001 1011 1111 1101 0101 0001 AAAA AAAA WORDS 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 2 1 2 2 1 1 1 1 1 1 1 1 1 1 CYCLES 1 1 1 1 1 1 1 1 1 1 1 1 2 2 1 1 1 1 1 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1

development support

Texas Instruments offers an extensive line of development tools for the C5x generation of DSPs, including tools to evaluate the performance of the processors, generate code, develop algorithm implementations, and fully integrate and debug software and hardware modules. The following products support development of C5x-based applications: Software Development Tools: Assembler/Linker Simulator Optimizing ANSI C compiler Application algorithms C/Assembly debugger and code profiler

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

41

Potrebbero piacerti anche

- Kanthar Sashti KavasamDocumento26 pagineKanthar Sashti KavasamSOWMYANessuna valutazione finora

- Electrical MachinesDocumento9 pagineElectrical MachinesskumaraneeeNessuna valutazione finora

- DSP Lab ManualDocumento54 pagineDSP Lab Manualkpsvenu100% (1)

- Basics of MPEG: Picture Sizes: Up To 4095 X 4095 Most Algorithms Are For The CCIR 601 Format For Video FramesDocumento15 pagineBasics of MPEG: Picture Sizes: Up To 4095 X 4095 Most Algorithms Are For The CCIR 601 Format For Video Framesanuradha_sreekanthNessuna valutazione finora

- 10-2 - Morphological Image ProcessingDocumento24 pagine10-2 - Morphological Image Processinganuradha_sreekanthNessuna valutazione finora

- Image ProDocumento95 pagineImage Proanuradha_sreekanthNessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Offered CoursesDocumento12 pagineOffered CoursesHasnain KhanNessuna valutazione finora

- Literary Quiz BeeDocumento4 pagineLiterary Quiz BeeMinnie Delos Santos100% (4)

- Chisac 15-19Documento5 pagineChisac 15-19IDL_ReporterosNessuna valutazione finora

- MongoDB and Mongoose in NodeJSDocumento35 pagineMongoDB and Mongoose in NodeJSGuarded Tablet100% (2)

- Auxiliaries As Main VerbsDocumento27 pagineAuxiliaries As Main VerbslhotazNessuna valutazione finora

- Fusion 8 Scripting GuideDocumento217 pagineFusion 8 Scripting GuideAvinash JagarlamudiNessuna valutazione finora

- Basics of Direct Indirect Speech For SSC Banking ExamsDocumento9 pagineBasics of Direct Indirect Speech For SSC Banking Examskamran imtiazNessuna valutazione finora

- Lesson 3 ListeningDocumento2 pagineLesson 3 ListeningANITA A/P SILVARAJOO MoeNessuna valutazione finora

- GUIDE 1 OUR LIFE - SolucionadoDocumento3 pagineGUIDE 1 OUR LIFE - SolucionadoPipe HenaoNessuna valutazione finora

- Online Hand Gesture Recognition &2016Documento4 pagineOnline Hand Gesture Recognition &2016sruthi 98Nessuna valutazione finora

- Artificial Intelligence Module 5Documento23 pagineArtificial Intelligence Module 5Neelesh ChandraNessuna valutazione finora

- Predicative ComplementsDocumento3 paginePredicative Complementsquestion questionNessuna valutazione finora

- T L 6189 Finding Adjectives Activity Sheet - Ver - 3 PDFDocumento3 pagineT L 6189 Finding Adjectives Activity Sheet - Ver - 3 PDFLara Vigil GonzálezNessuna valutazione finora

- LogicalDocumento8 pagineLogicalMharlone Chopap-ingNessuna valutazione finora

- Kolak - Wittgenstein's Tractatus, Mayfield 1998, OCRDocumento92 pagineKolak - Wittgenstein's Tractatus, Mayfield 1998, OCRThái Hồng100% (3)

- Sample Study SkillsDocumento15 pagineSample Study SkillsSamira FfNessuna valutazione finora

- EAP I4 Unit 9 Quiz Answer Sheet V4.0919Documento3 pagineEAP I4 Unit 9 Quiz Answer Sheet V4.0919Camilo DIAZ PARDONessuna valutazione finora

- Written and Spoken LanguageDocumento6 pagineWritten and Spoken LanguagenoorNessuna valutazione finora

- Sigil MagicDocumento27 pagineSigil Magic꧁?Ꮆเεɠυε’ร Ꮆเ૨l?꧂95% (44)

- Speech & Language Therapy in Practice, Summer 2005Documento32 pagineSpeech & Language Therapy in Practice, Summer 2005Speech & Language Therapy in PracticeNessuna valutazione finora

- Karthik CV MDocumento2 pagineKarthik CV MHarinath SwargamNessuna valutazione finora

- 1íó +-+++ + - +t+s P ++Documento9 pagine1íó +-+++ + - +t+s P ++Thao Ngan HoNessuna valutazione finora

- Week 2-Sept. 5-9, 2022Documento2 pagineWeek 2-Sept. 5-9, 2022Myra Barcellano PescadorNessuna valutazione finora

- 3rd Grade Maths HomeworkDocumento196 pagine3rd Grade Maths HomeworkIsaiah D Zizi80% (5)

- 00-01 2nd Midterm Exam Lise 2Documento3 pagine00-01 2nd Midterm Exam Lise 2arsoyardaNessuna valutazione finora

- Conceptual System of World Reflection - 2. Universal MetaphorsDocumento23 pagineConceptual System of World Reflection - 2. Universal MetaphorsNazerke AbdrahmanovaNessuna valutazione finora

- Sekolah Menengah Dato' Klana Putra Lenggeng 2020 Yearly Planner For English Language PanelDocumento11 pagineSekolah Menengah Dato' Klana Putra Lenggeng 2020 Yearly Planner For English Language PanelSabaRajooNessuna valutazione finora

- Collins Workplace - Business CommunicationDocumento99 pagineCollins Workplace - Business CommunicationHoàng Ngọc Dương 15TAC 001Nessuna valutazione finora

- English Quarter 2 Week 1Documento4 pagineEnglish Quarter 2 Week 1Sinen ErmitaNessuna valutazione finora

- TURKISH GRAMMAR UPDATED ACADEMIC EDITION YÜKSEL GÖKNEL 2013-SignedDocumento441 pagineTURKISH GRAMMAR UPDATED ACADEMIC EDITION YÜKSEL GÖKNEL 2013-Signedyukselgoknel93% (15)