Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Sop

Caricato da

Niranjan ReddyDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Sop

Caricato da

Niranjan ReddyCopyright:

Formati disponibili

http://www.cse.hcmut.edu.

vn/~tnthinh/DS1

dce

2007

dce

2009

Introduction

Basic logic gate functions will be combined in combinational logic circuits. Simplification of logic circuits will be done using Boolean algebra and a mapping technique. Troubleshooting of combinational circuits will be introduced. PLD structures will be explained.

Digital Logic Design 1

Tran Ngoc Thinh HCMC University of Technology http://www.cse.hcmut.edu.vn/~tnthinh

BK

TP.HCM

dce

2009

Sum-of-Products Form

A Sum-of-products (SOP) expression will appear as two or more AND terms ORed together.

ABC + ABC AB + ABC + C D + D

dce

2009

Simplifying Logic Circuits

The circuits below both provide the same output, but the lower one is clearly less complex.

A Product-of-sums(POS) expression is sometimes used in logic design.

( A + B + C )( A + B + C )

We will study simplifying logic circuits using Boolean algebra and Karnaugh mapping

dce

2009

Algebraic Simplification

Place the expression in SOP form by applying DeMorgans theorems and multiplying terms. Check the SOP form for common factors and perform factoring where possible. Note that this process may involve some trial and error to obtain the simplest result.

dce

2009

Designing Combinational Logic Circuits

To solve any logic design problem:

Interpret the problem and set up its truth table. Write the AND (product) term for each case where the output equals 1. Combine the terms in SOP form. Simplify the output expression if possible. Implement the circuit for the final, simplified expression.

Digital Logic Design 1

http://www.cse.hcmut.edu.vn/~tnthinh/DS1

dce

2009

Karnaugh Map Method

A graphical method of simplifying logic equations or truth tables. Also called a K map. Theoretically can be used for any number of input variables, but practically limited to 5 or 6 variables.

dce

2009

Karnaugh Map Method

The truth table values are placed in the K map. Adjacent K map square differ in only one variable both horizontally and vertically. The pattern from top to bottom and left to right must be in the form AB, AB, AB, AB A SOP expression can be obtained by ORing all squares that contain a 1.

dce

2009

Karnaugh Map Method

Looping adjacent groups of 2, 4, or 8 1s will result in further simplification. When the largest possible groups have been looped, only the common terms are placed in the final expression. Looping may also be wrapped between top, bottom, and sides.

dce

2009

Karnaugh Map for 2, 3 variables

Looping adjacent groups of 2, 4, or 8 1s will result in further simplification.

dce

2009

Karnaugh Map for 4 variables

Looping adjacent groups of 2, 4, or 8 1s will result in further simplification.

dce

2009

Minimization Technique

Minimization is done by spotting patterns of 1's and 0's Simple theorems are then used to simplify the Boolean description of the patterns Pairs of adjacent 1's

remember that adjacent squares differ by only one variable hence the combination of 2 adjacent squares has the form P ( A + A ) this can be simplified (from before) to just P

Digital Logic Design 1

http://www.cse.hcmut.edu.vn/~tnthinh/DS1

dce

2009

Example of pairs of adjacent of 1s

Minimization is done by spotting patterns of 1's and 0s

dce

2009

Example of grouping of fours 1s (quads)

Minimization is done by spotting patterns of 1's and 0s

dce

2009

Example of grouping of eight 1s (octals)

Minimization is done by spotting patterns of 1's and 0s

dce

2009

Complete Simplification Process

Complete K map simplification process:

Construct the K map, place 1s as indicated in the truth table. Loop 1s that are not adjacent to any other 1s. Loop 1s that are in pairs Loop 1s in octets even if they have already been looped. Loop quads that have one or more 1s not already looped. Loop any pairs necessary to include 1st not already looped. Form the OR sum of terms generated by each loop.

dce

2009

Dont Care Conditions

In certain cases some of the minterms may never occur or it may not matter what happens if they do

In such cases we fill in the Karnaugh map with and X

meaning don't care

dce

2009

Exclusive-OR

The exclusive OR (XOR) produces a HIGH output whenever the two inputs are at opposite levels.

When minimizing an X is like a "joker"

X can be 0 or 1 - whatever helps best with the minimization

Dont care conditions should be changed to either 0 or 1 to produce K-map looping that yields the simplest expression.

Digital Logic Design 1

http://www.cse.hcmut.edu.vn/~tnthinh/DS1

dce

2009

Exclusive-NOR

The exclusive NOR (XNOR) produces a HIGH output whenever the two inputs are at the same level. XOR and XNOR outputs are opposite.

dce

2009

Parity Generator and Checker

XOR and XNOR gates are useful in circuits for parity generation and checking.

dce

2009

Enable/Disable Circuits

A circuit is enabled when it allows the passage of an input signal to the output. A circuit is disabled when it prevents the passage of an input signal to the output. Situations requiring enable/disable circuits occur frequently in digital circuit design.

dce

2009

Enable/Disable Circuits

AND gate function act as enable/disable circuits

dce

2009

Basic Characteristics of Digital ICs

IC chips consist of resistors, diodes, and transistors fabricated on a piece of semiconductor material called a substrate. Digital ICs may be categorized according to the number of logic gates on the substrate:

SSI less than 12 MSI 12 to 99 LSI 100 to 9999 VLSI 10,000 to 99,999 ULSI 100,000 to 999,999 GSI 1,000,000 or more

dce

2009

Basic Characteristics of Digital ICs

The first package we will examine is the dual in line package (DIP).

Digital Logic Design 1

http://www.cse.hcmut.edu.vn/~tnthinh/DS1

dce

2009

Basic Characteristics of Digital ICs

ICs are also categorized by the type of components used in their circuits.

Bipolar ICs use NPN and PNP transistors Unipolar ICs use FET transistors.

dce

2009

Basic Characteristics of Digital ICs

The TTL family consists of subfamilies as listed in the table.

The transistor-transistor logic (TTL) and the complementary metal-oxide semiconductor (CMOS) families will both be examined.

dce

2009

Basic Characteristics of Digital ICs

dce

2009

Basic Characteristics of Digital ICs

Power (referred to as VCC) and ground connections are required for chip operation. VCC for TTL devices is normally +5 V. VDD for CMOS devices can be from +3 to +18 V.

The CMOS family consists of several series, some of which are shown in the table.

dce

2009

Basic Characteristics of Digital ICs

Inputs that are not connected are said to be floating. The consequences of floating inputs differ for TTL and CMOS.

Floating TTL input acts like a logic 1. The voltage measurement may appear in the indeterminate range, but the device will behave as if there is a 1 on the floating input. Floating CMOS inputs can cause overheating and damage to the device. Some ICs have protection circuits built in, but the best practice is to tie all unused inputs either high or low.

dce

2009

Troubleshooting Digital Systems

3 basic steps

Fault detection, determine operation to expected operation. Fault isolation, test and measure to isolate the fault. Fault correction, repair the fault.

Good troubleshooting skills come through experience in actual hands-on troubleshooting. The basic troubleshooting tools used here will be: the logic probe, oscilloscope, and logic pulser. The most important tool is the technicians brain.

Digital Logic Design 1

http://www.cse.hcmut.edu.vn/~tnthinh/DS1

dce

2009

Troubleshooting Digital Systems

The logic probe will indicate the presence or absence of a signal when touched to a pin as indicated below.

dce

2009

Internal Digital IC Faults

Most common internal failures:

Malfunction in the internal circuitry. Inputs or outputs shorted to ground or VCC Inputs or outputs open-circuited Short between two pins (other than ground or VCC)

dce

2009

Internal Digital IC Faults

Malfunction in internal circuitry

Outputs do not respond properly to inputs. Outputs are unpredictable. The input will be stuck in LOW or HIGH state. Output will be stuck in LOW or HIGH state. Floating input in a TTL device will result in a HIGH output. Floating input in a CMOS device will result in erratic or possibly destructive output. An open output will result in a floating indication. The signal at those pins will always be identical.

dce

2009

External Faults

Open signal lines signal is prevented from moving between points. Some causes:

Broken wire Poor connections (solder or wire-wrap) Cut or crack on PC board trace Bent or broken IC pins. Faulty IC socket

Input internally shorted to ground or supply

Output internally shorted to ground or supply Open-circuited input or output

Detect visually and verify with an ohmmeter.

Short between two pins

dce

2009

External Faults

Shorted signal lines the same signal will appear on two or more pins. VCC or ground may also be shorted. Some causes:

Sloppy wiring Solder bridges Incomplete etching

dce

2009

External Faults

Faulty power supply ICs will not operate or will operate erratically.

May lose regulation due to an internal fault or because circuits are drawing too much current. Always verify that power supplies are providing the specified range of voltages and are properly grounded. Use an oscilloscope to verify that AC signals are not present.

Detect visually and verify with an ohmmeter.

Digital Logic Design 1

http://www.cse.hcmut.edu.vn/~tnthinh/DS1

dce

2009

External Faults

Output loading caused by connecting too many inputs to the output of an IC.

Causes output voltage to fall into the indeterminate range. This is called loading the output. Usually a result of poor design or bad connection.

dce

2009

Programmable Logic Devices

PLDs allow the design process to be automated. Designers identify inputs, outputs, and logical relationships. PLDs are electronically configured to form the defined logic circuits.

dce

2009

Programmable Logic Devices

PLD ICs can be programmed out of system or in system. Logic circuits can be described using schematic diagrams, logic equations, truth tables, and HDL. PLD development software can convert any of these descriptions into 1s and 0s and loaded into the PLD.

dce

2009

Programmable Logic Devices

Hierarchical design small logic circuits are defined and combined with other circuits to form a large section of a project. Large sections can be combined and connected for form a system. Top-down design requires the definition of sub sections that will make up the system, and definition of the individual circuits that will make up each sub section. Each level of the hierarchy can be designed and tested individually.

dce

2009

Programmable Logic Devices

A system is built from the bottom up.

Each block is described by a design file. The designed block is tested After testing it is compiled using development software. The compiled block is tested using a simulator for verify correct operation. A PLD is programmed to verify correct operation.

Digital Logic Design 1

Potrebbero piacerti anche

- Introduction to Digital Logic Design Appendix ADocumento22 pagineIntroduction to Digital Logic Design Appendix AXaid IbrahimNessuna valutazione finora

- Chapter 3 - Implementation TechnologyDocumento31 pagineChapter 3 - Implementation TechnologyAhmed YasserNessuna valutazione finora

- Handouts DSD 13 PLD FPGA PDFDocumento15 pagineHandouts DSD 13 PLD FPGA PDFNabajit ChatterjeeNessuna valutazione finora

- Lec 11 Introduction To Digital ElectronicsDocumento43 pagineLec 11 Introduction To Digital ElectronicsDassintakashimaNessuna valutazione finora

- Digital Electronics - ArunDocumento45 pagineDigital Electronics - ArunArun ANessuna valutazione finora

- EECS150 - Digital Design Outline: Lecture 2 - ReviewDocumento6 pagineEECS150 - Digital Design Outline: Lecture 2 - ReviewDuc DucNessuna valutazione finora

- L10 - Combinational & SequentialDocumento59 pagineL10 - Combinational & Sequentialitheachtholly1227Nessuna valutazione finora

- CS301Y22 Chapter 2 Boolean Algebra and Logic Gates HandoutDocumento27 pagineCS301Y22 Chapter 2 Boolean Algebra and Logic Gates HandoutNoah LiknawNessuna valutazione finora

- Digital Electronics 1Documento138 pagineDigital Electronics 1krishnakumaranNessuna valutazione finora

- Chapter01b - Intro To Digital Logic DesignDocumento47 pagineChapter01b - Intro To Digital Logic Designriel_ylayaNessuna valutazione finora

- CCR204 - Lec04Documento38 pagineCCR204 - Lec04Moni SharmaNessuna valutazione finora

- mod3 part 1Documento36 paginemod3 part 1Sherine SebastianNessuna valutazione finora

- ppt on Logic circuits :combinational By dushyant kumarDocumento27 pagineppt on Logic circuits :combinational By dushyant kumarDushyant KumarNessuna valutazione finora

- IC Integrated Circuits Explained: Types, Logic Families & Digital Logic GatesDocumento24 pagineIC Integrated Circuits Explained: Types, Logic Families & Digital Logic GatesmuktikantaNessuna valutazione finora

- ch4 Combinational Logic CircuitsDocumento90 paginech4 Combinational Logic CircuitsMinh Mẫn NguyễnNessuna valutazione finora

- Chapter 1: Introduction To CMOS Circuits: 1.1 MOS (Metal Oxide Silicon) Transistor HistoryDocumento35 pagineChapter 1: Introduction To CMOS Circuits: 1.1 MOS (Metal Oxide Silicon) Transistor HistoryJyotika AggarwalNessuna valutazione finora

- Combinational Logic Design ProcessDocumento21 pagineCombinational Logic Design ProcessILikeScribd5050Nessuna valutazione finora

- 3.important Short Questions and Answers - Combinational CircuitsDocumento6 pagine3.important Short Questions and Answers - Combinational CircuitsDevisriNessuna valutazione finora

- Digital Techniques: Combinational Logic CircuitDocumento21 pagineDigital Techniques: Combinational Logic CircuitGiang ĐặngNessuna valutazione finora

- Logic Synthesis at MITDocumento8 pagineLogic Synthesis at MITkumarguptav91Nessuna valutazione finora

- Unit 8: Cmos TestingDocumento23 pagineUnit 8: Cmos Testingramsrr289617Nessuna valutazione finora

- Switching Circuits & Logic Design: MUX Decoder and PLDDocumento33 pagineSwitching Circuits & Logic Design: MUX Decoder and PLD555-193614Nessuna valutazione finora

- FPGA Design Flow: Muthuswamy@msoe - EduDocumento32 pagineFPGA Design Flow: Muthuswamy@msoe - EduissayedNessuna valutazione finora

- KTMT HN - ch03.DigitalCircuitDesignDocumento42 pagineKTMT HN - ch03.DigitalCircuitDesignNguyênNessuna valutazione finora

- Programmable Logic Devices: PLDs, FPGAs, and Their ArchitecturesDocumento22 pagineProgrammable Logic Devices: PLDs, FPGAs, and Their ArchitecturesJames Henry DannattNessuna valutazione finora

- Cmos Design MethodsDocumento69 pagineCmos Design MethodsPuneet PatilNessuna valutazione finora

- PLC (Programmable Logic Control)Documento57 paginePLC (Programmable Logic Control)sunilNessuna valutazione finora

- Seminar Topic:-Programming of PLC (Ladder Programming) : Presented By: - Guided ByDocumento14 pagineSeminar Topic:-Programming of PLC (Ladder Programming) : Presented By: - Guided ByShubam SharmaNessuna valutazione finora

- DLD Lab 04-BCD To Seven SegmentDocumento6 pagineDLD Lab 04-BCD To Seven SegmentMuhammad RafayNessuna valutazione finora

- ETU 07322 Lecture 3 - Combinational Logic CircuitDocumento43 pagineETU 07322 Lecture 3 - Combinational Logic CircuitFrancis LubangoNessuna valutazione finora

- ECE 301 - Digital Electronics: NAND and NOR Circuits, Multi-Level Logic Circuits, and Multiple-Output Logic CircuitsDocumento30 pagineECE 301 - Digital Electronics: NAND and NOR Circuits, Multi-Level Logic Circuits, and Multiple-Output Logic CircuitsVIKH33Nessuna valutazione finora

- Unit 1 3Documento30 pagineUnit 1 3Prabhav NandanNessuna valutazione finora

- Fundamentals of PLCs ReviewDocumento65 pagineFundamentals of PLCs ReviewPatrickSchardt100% (2)

- Introduction To Microcontrollers Final1Documento43 pagineIntroduction To Microcontrollers Final1Ferdie SelgaNessuna valutazione finora

- Chapter 1 of Textbook by John F Wakerly - The Materials in This Chapter Will Not Be CoveredDocumento26 pagineChapter 1 of Textbook by John F Wakerly - The Materials in This Chapter Will Not Be CoveredEric LeeNessuna valutazione finora

- Ch03 Digital LogicDocumento53 pagineCh03 Digital LogicKarthikeyan RamajayamNessuna valutazione finora

- Boolean-Algebra&logic gates-1Documento36 pagineBoolean-Algebra&logic gates-1birukmes2309Nessuna valutazione finora

- MATLAB Tutorial II: Power Electronics and SimulinkDocumento31 pagineMATLAB Tutorial II: Power Electronics and SimulinkMohd Helmy Hakimie RozlanNessuna valutazione finora

- Ee 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EduDocumento41 pagineEe 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EduRanganadh MvNessuna valutazione finora

- EECS 150 - Counters for Digital Systems DesignDocumento11 pagineEECS 150 - Counters for Digital Systems Designjatanbhatt89100% (1)

- Ddco 1Documento104 pagineDdco 1samanthd2004Nessuna valutazione finora

- Digital LOGIC DESIGN Chapter 5,6,7Documento32 pagineDigital LOGIC DESIGN Chapter 5,6,7abdishakurNessuna valutazione finora

- Module 1Documento55 pagineModule 1vishesh panchalNessuna valutazione finora

- Lab Manual Logic Design 1-2Documento23 pagineLab Manual Logic Design 1-2akahNessuna valutazione finora

- 07 DecodersDocumento21 pagine07 DecodersRafena17Nessuna valutazione finora

- L02 FaultModelingDocumento15 pagineL02 FaultModelingAmit RohillaNessuna valutazione finora

- EE1024 - Chapter 1 Day 1Documento22 pagineEE1024 - Chapter 1 Day 1flaviaNessuna valutazione finora

- Lecture 10 Combinational Circuits Decoder Part-IIDocumento12 pagineLecture 10 Combinational Circuits Decoder Part-IIHaris AliNessuna valutazione finora

- Combinational Logic Circuit Decoder and MultiplexDocumento29 pagineCombinational Logic Circuit Decoder and Multiplexram5nath-3Nessuna valutazione finora

- Practical DTDocumento19 paginePractical DTKundan BhartiNessuna valutazione finora

- Testing For CmosDocumento11 pagineTesting For Cmossree2728Nessuna valutazione finora

- PCS405 VLSI DESIGN AND EMBEDDED SYSTEMS UNIT 1 COMPONENTSDocumento11 paginePCS405 VLSI DESIGN AND EMBEDDED SYSTEMS UNIT 1 COMPONENTSkumar_9583Nessuna valutazione finora

- ArduinoDocumento44 pagineArduinojocansino4496Nessuna valutazione finora

- Digital Logic Level: Ms - Chit Su MonDocumento74 pagineDigital Logic Level: Ms - Chit Su MonAjharuddin AnsariNessuna valutazione finora

- Ch1 of Digital Logic and DesignDocumento91 pagineCh1 of Digital Logic and DesignAbdul RehmanNessuna valutazione finora

- Ueeneeh148A Design and Develop Advanced Digital Systems Navjot SinghDocumento19 pagineUeeneeh148A Design and Develop Advanced Digital Systems Navjot SinghAmandeep KarwalNessuna valutazione finora

- CSE211: Course Assessment, Lectures, BooksDocumento83 pagineCSE211: Course Assessment, Lectures, BooksJosh AmbatiNessuna valutazione finora

- Microprocessor System Design: A Practical IntroductionDa EverandMicroprocessor System Design: A Practical IntroductionNessuna valutazione finora

- CMR Institute of Technology: Hyderabad: 17EC3101PC H.T.No R 0Documento1 paginaCMR Institute of Technology: Hyderabad: 17EC3101PC H.T.No R 0Niranjan ReddyNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Doping and Doping Less III-V Tunnel Field Effect Transistors (TFET) : Investigation On Reasons For ON Current ImprovementDocumento4 pagineDoping and Doping Less III-V Tunnel Field Effect Transistors (TFET) : Investigation On Reasons For ON Current ImprovementNiranjan ReddyNessuna valutazione finora

- Bharat-22 Paper 40Documento6 pagineBharat-22 Paper 40Niranjan ReddyNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Bharat-22 Paper 40Documento6 pagineBharat-22 Paper 40Niranjan ReddyNessuna valutazione finora

- Bharat-22 Paper 10Documento6 pagineBharat-22 Paper 10Niranjan ReddyNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Ldic Final Set2Documento1 paginaLdic Final Set2Niranjan ReddyNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- Advanced Computer ArchitectureDocumento1 paginaAdvanced Computer ArchitecturesanurNessuna valutazione finora

- CMR Institute of Technology: Hyderabad: 17EC3101PC/EC-PCC-222 H.T.No R 0Documento2 pagineCMR Institute of Technology: Hyderabad: 17EC3101PC/EC-PCC-222 H.T.No R 0Niranjan ReddyNessuna valutazione finora

- Stick DiagramsDocumento18 pagineStick DiagramsAbhiram Kramadhati GopiNessuna valutazione finora

- Ldic Final Set2Documento1 paginaLdic Final Set2Niranjan ReddyNessuna valutazione finora

- Strain-Engineered Biaxial Tensile Epitaxial Germanium For High-Performance Ge/Ingaas Tunnel Field-Effect TransistorsDocumento10 pagineStrain-Engineered Biaxial Tensile Epitaxial Germanium For High-Performance Ge/Ingaas Tunnel Field-Effect TransistorsNiranjan ReddyNessuna valutazione finora

- Gate - DigitalsnotesDocumento98 pagineGate - DigitalsnotesNiranjan ReddyNessuna valutazione finora

- CMR Institute of Technology: Hyderabad: Code No.Documento1 paginaCMR Institute of Technology: Hyderabad: Code No.Shruti BiradarNessuna valutazione finora

- Ldic Final Set2Documento1 paginaLdic Final Set2Niranjan ReddyNessuna valutazione finora

- 1.electronics Device Circuit PDFDocumento274 pagine1.electronics Device Circuit PDFAbhijeet AwasthiNessuna valutazione finora

- Engineering Workshop Lab ManualDocumento97 pagineEngineering Workshop Lab ManualNiranjan ReddyNessuna valutazione finora

- Engineering Workshop Lab ManualDocumento97 pagineEngineering Workshop Lab ManualNiranjan ReddyNessuna valutazione finora

- Lambda RuleDocumento8 pagineLambda RuleAshish UpadhyayaNessuna valutazione finora

- 2-Bit Magnitude Comparator Design Using Logic StylesDocumento12 pagine2-Bit Magnitude Comparator Design Using Logic StylesSunith CkNessuna valutazione finora

- EE2001 Design Project Technical MaterialDocumento40 pagineEE2001 Design Project Technical MaterialMattNessuna valutazione finora

- DiDocumento10 pagineDipakojidastavimNessuna valutazione finora

- Analog Circuits & DesignDocumento2 pagineAnalog Circuits & Designlalitkumar bannagareNessuna valutazione finora

- The Multiplexer: Basic Multiplexing SwitchDocumento8 pagineThe Multiplexer: Basic Multiplexing SwitchJohn Brix BalisterosNessuna valutazione finora

- Small Signal Model: MOS Field-Effect TransistorsDocumento100 pagineSmall Signal Model: MOS Field-Effect Transistorsraja_ramalingam07Nessuna valutazione finora

- DDP SscjeDocumento2 pagineDDP Sscjebinit ranjanNessuna valutazione finora

- EEE101 Lab Report on Verifying Thevenin's TheoremDocumento8 pagineEEE101 Lab Report on Verifying Thevenin's TheoremGaffar KhanNessuna valutazione finora

- Circuit Theory - Solved Assignments - Semester Fall 2005Documento18 pagineCircuit Theory - Solved Assignments - Semester Fall 2005Muhammad Umair50% (2)

- Circuit Analysis 2 - PS2Documento5 pagineCircuit Analysis 2 - PS2BlueNova VortexNessuna valutazione finora

- Digital Logic LAB Manual KL-300 (Shorted)Documento66 pagineDigital Logic LAB Manual KL-300 (Shorted)s_afwan78% (9)

- Unit-5 EE3402 LIC (R-2021)Documento84 pagineUnit-5 EE3402 LIC (R-2021)Jishnuraj KubandrarajNessuna valutazione finora

- ICD Lecture 8Documento3 pagineICD Lecture 8MaheshwaranNessuna valutazione finora

- PAL007A Pioneer PDFDocumento1 paginaPAL007A Pioneer PDFWillian Jose Rosas MartinezNessuna valutazione finora

- 555 ModesDocumento2 pagine555 ModesWaqas Khalid MughalNessuna valutazione finora

- Forced CommutationDocumento2 pagineForced CommutationKireety MandavilliNessuna valutazione finora

- Lecture 2 IO Ports and 8051 CircuitDocumento3 pagineLecture 2 IO Ports and 8051 Circuit12343567890Nessuna valutazione finora

- Abstract SAR ADCDocumento2 pagineAbstract SAR ADCabhishekNessuna valutazione finora

- Class F: ©james BuckwalterDocumento33 pagineClass F: ©james Buckwalterts bulganNessuna valutazione finora

- 國立臺灣大學電機工程學系期末考電路學Documento3 pagine國立臺灣大學電機工程學系期末考電路學黃元湛Nessuna valutazione finora

- Interfacing Between ECL / LVECL / PECL / Lvpecl - To - TTL / LVTTL / Cmos / LvcmosDocumento6 pagineInterfacing Between ECL / LVECL / PECL / Lvpecl - To - TTL / LVTTL / Cmos / LvcmosSirsendu DuttaNessuna valutazione finora

- Banba - BandgapDocumento5 pagineBanba - BandgapAldo BottelliNessuna valutazione finora

- Gateeasy D To A PDFDocumento3 pagineGateeasy D To A PDFShubham kumarNessuna valutazione finora

- Kenwood Kvt-819 - 829 - 839 Monitor With DVD ReceiverDocumento80 pagineKenwood Kvt-819 - 829 - 839 Monitor With DVD ReceiverpromexbrailaNessuna valutazione finora

- 78S40Documento0 pagine78S40Pravin MevadaNessuna valutazione finora

- The Theorem of Mesh and Nodal - DC circuit analysisDocumento2 pagineThe Theorem of Mesh and Nodal - DC circuit analysisJerry Arthur MartinezNessuna valutazione finora

- CountersDocumento19 pagineCounterslakraniNessuna valutazione finora

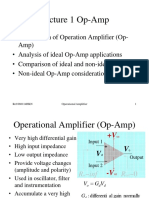

- L01 Operational AmplifierDocumento27 pagineL01 Operational AmplifierSylvester Delali DordziNessuna valutazione finora

- Engineering Physics Laboratory - PHY119: Experiment Number - 9Documento21 pagineEngineering Physics Laboratory - PHY119: Experiment Number - 9Sabjit SinghNessuna valutazione finora