Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

MCP A2 MicroZ80 Descricao

Caricato da

dearaujo4Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

MCP A2 MicroZ80 Descricao

Caricato da

dearaujo4Copyright:

Formati disponibili

AULA 10 SUMRIO

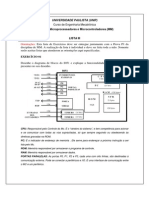

UNIVERSIDADE EDUARDO MONDLANE

FACULDADE DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELECTROTCNICA CAPTULO 2 - INTRODUO AO MICROPROCESSADOR Z80

2.1. Arquitectura Geral do Micro Z80 2.2. Descrio Fsica do Micro Z80

2.3. Dispositivos de Entrada e Sada

Bibliografia principal: 1. Zilog - Z80 Family CPU User Manual - UM008005-0205, 2004, San Jose 2. Zilog Z80 PIO User Manual 3. Bradley, John - Introduction to Microprocessors Micamaster 980 & 960, Feedback, England

(P)(C) A.B.Cuinhane 2 UEM - Digital

Electrnica Digital II

Eng. Albino B Cuinhane

(P)(C) A.B.Cuinhane

1 UEM - Digital

Captulo 2

2.1. Arquitectura Geral

Microprocessador Z80

(P)(C) A.B.Cuinhane 3 UEM - Digital

NOTA: O estudante deve ler a informao adicional no livro 1 da bibliografia recomendada, Pginas 1 6

(P)(C) A.B.Cuinhane

4 UEM - Digital

2.1. Arquitectura Geral

2.1. Arquitectura Geral

Para comearmos a entender o Z80 convm iniciar pela arquitectura geral mostrada no diagrama funcional a seguir.

Sinais de controle do sistema

A Unidade Central de Processamento, ou CPU, tem disponvel 208bits de memria de escrita e leitura (R/W) que so agrupados para formarem 18 registadores de 8 bits e 4 de 16 e so de uso geral para o utente. So feitos base de memrias estticas RAM.

REGISTOS PRINCIPAIS REGISTOS ALTERNATIVOS D E H L Acumulador FLAGs A' F' B' C' D' E' H' L' Acumulador FLAGs A F B C

Decodificador De Instrues

Controle da CPU

Fig.A10.1

Registo de instrues Sinais de controle

REGISTO I REGISTO INDEXADO (IX) STACK POINTER (SP) REGISTOS ESPECIAIS REGISTO R REGISTO INDEXADO (IY) PROGRAM COUNTER (PC)

Fig.A10.2

Controle do barramento de dados barramento de dados

ALU

Registadores da CPU

Controle de endereos

barramento de endereos

(P)(C) A.B.Cuinhane

5 UEM - Digital

Este grupo de registos inclui 6 de uso geral que podem ser usados individualmente como registos de 8 bits ou emparelhados formando os pares BC, DE e HL de 16 bits.

(P)(C) A.B.Cuinhane

6 UEM - Digital

Electrnica Digital II

2.1. Arquitectura Geral

ALU - Aritmetic Logic Unit (Unidade Lgica e Aritmtica) Esta unidade tem a funo de executar diversas operaes lgicas e aritmticas. Tem acesso aos registos e ao barramento de dados. As funes realizadas pela ALU so : Subtrao Adio

Set bit (colocar um bit em 1)

2.1. Arquitectura Geral

REGISTO DE INSTRUES/CONTROLE DA CPU A cada ciclo de instruo uma instruo trazida da memria, pela via de dados, para o registos de instrues onde decodificada. Com base nesta decifrao, a unidade de controle fornece os sinais de controle necessrios para ler ou escrever dados num registo, na memria ou num dispositivo de entrada e sada, controlar a ALU e fornecer todos os sinais externos de controle ACUMULADOR E FLAGS Todas as operaes lgicas e aritmticas de 8 bits so executadas na ALU e o resultado mantido no acumulador. Enquanto o registo de flags(bandeiras) indica condies especficas para cada operao

Testar bit Incrementar Decrementar

Comparao AND OR XNOR Shift right, shift left Rotaes Reset bit(zerar um bit)

(P)(C) A.B.Cuinhane

7 UEM - Digital

(P)(C) A.B.Cuinhane

8 UEM - Digital

2.1. Arquitectura Geral

STACK POINTER, SP (Ponteiro de Pilha, PP) O SP ou ponteiro de pilha, um registo de 16 bits inicializado pelo usurio com o endereo inicial de um campo da RAM usado para a pilha. A pilha organizada como um arquivo LIFO e os dados podem ser buscados ou enviados para esta pilha. Esta pilha permite uma simples implementao de mltiplos nveis de interrupo, subrotinas e manipulao de dados PROGRAM COUNTER, PC (Contador de Programa, CP) O contador de programa formado por um registo de 16 bits no qual mantido o endereo da ltima instruo que est sendo acedida na memria. O PC automaticamente incrementado em 1 aps a transferncia do seu contedo para as linhas de endereamento. Num caso de salto(Jump) o refrescamento feito com novo valor

(P)(C) A.B.Cuinhane 9 UEM - Digital

2.1. Arquitectura Geral

REGISTOS INDEXADOS IX e IY So registo independentes de 16 bits usados para o endereamaneto indexado. Apontam para uma regio especfica da memria na qual pode ser armazenado ou retirado uma informao. Eles contm a referncia do endereo ao qual se adiciona um valor(um byte) contido na instruo que pretende que se aponte pa a algum endereo REGISTO DE REFRESCAMENTO DA MEMRIA R O registo R usado para refrescar a memria dinmica, que tem tendncia de perder os dados ao longo do tempo. Contm 8 bits mas so incrementados automaticamente apenas os 7 bms. O registo R usado com o I que fornece o BMS dos 2 Bytes necessrios para endereamanto. O referescamento da memria acontece enquanto a CPU est ocupada com a decodificao e execuo duma instruo

(P)(C) A.B.Cuinhane 10 UEM - Digital

2.1. Arquitectura Geral

REGISTO I usado para o endereamento indirecto da memria em face duma interrupo. O registo I contem o BMS do endereo enquanto o solicitante da interrupo entrega o Bms.

2.2. Descrio Fsica (pinos)

NOTA: O estudante deve ler a informao adicional no livro 1 da bibliografia recomendada, Pginas 7 10

(P)(C) A.B.Cuinhane

11 UEM - Digital

(P)(C) A.B.Cuinhane

12 UEM - Digital

Electrnica Digital II

2.2. Descrio Fsica (pinos)

A Figura ao lado mostra o pinaout do Z-80. Os sinais de controle so activos em LOW. Os barramentos de endereo e de dados so activos nos dois estados. Na descrio a seguir indica-se entre parnteses se o sinal de entrada ou de sada e se tem trs estados(atravs dum T)

2.2. Descrio fsica (pinos)

A0 - A15 (SADA-T) ADDRESS BUS: 16 pinos que compem as linhas de endereamento. Esta via de endereos permite a locao de memria assim como dos dispositivos de I/O. Com as 16 linhas pode-se enderear 256 dispositivos atravs dos 8 bits menos significativos. No entanto podese enderear 62.536 localidades de memria. D0 - D7 (ENTRADA/SADA-T) DATA BUS: 8 linhas bidireccionais para troca de dados entre a UCP e os dispositivos I/O e memria. ___ M1 (SADA) MACHINE CYCLE ONE: Indica que a UCP est realizando um ciclo de busca. Para instrues de 2 bytes, este sinal gerado para cada byte que for buscado. Este sinal usado em conjunto com o IORQ para indicar o reconhecimento de interrupo.

(P)(C) A.B.Cuinhane

BUSRQ

(P)(C) A.B.Cuinhane

13 UEM - Digital

14 UEM - Digital

_____ MREQ (SADA-T) MEMORY REQUEST: Indica que a via de endereos possui um endereo para efectuar leitura ou gravao na memria _____ RFSH (SADA) REFRESH: Indica que os 7 bits menos significativos do barramento de endereo contem a posio da memria a ser restaurada ___ WR (SADA-T) MEMORY WRITE: Indica que o barramento de dados contem dados a enviar para a memria ou dispositivo de I/O ___ RD(SADA-T) MEMORY READ: Indica que a UCP vai ler dados na memria ou num dispositivo de I/O

(P)(C) A.B.Cuinhane

2.2. Descrio fsica (pinos)

2.2. Descrio fsica (pinos)

_____ IORQ (SADA-T) INPUT/OUTPUT REQUEST: Indica que os 8 bms do barramento de endereos possuem o endereo dum dispositivo I/O no qual ser feita uma leitura ou gravao de dados _____ WAIT (ENTRADA) WAIT: Indica UCP que a memria ou perifrico endereado no est pronto para a transferncia de dados. Este sinal possibilita a sincronizao entre a UCP e outros elementos ___ INT (ENTRADA) INTERRUPT REQUEST: gerado por perifricos para pedir uma

interrupo. Este sinal ser reconhecido no fim da instruo que de momento esteja sendo executado, a menos que o BUSRQ esteja activo. Quando o pedido de interrupo aceite pela UCP, esta envia o IORQ e M1

(P)(C) A.B.Cuinhane 16 UEM - Digital

15 UEM - Digital

_____ HALT (SADA) HALT STATE: Indica que a UCP est parado por instruo de software aguardando uma interrupo ____ NMI (ENTRADA) NON MASKABLE INTERRUPT: Este sinal tem prioridade superior ao INT e faz com que o CP v para o endereo 0066 H. O contedo do CP armazenado na pilha por forma a poder retornar-se ao programa original no ponto onde NMI foi gerado ______ RESET (ENTRADA) RESET: Este sinal carrega o CP com o endereo 0000H que inicializa a UCP. Durante este sinal, todos os sinais ficam inactivos e os dois barramentos ficam em alta impedncia

(P)(C) A.B.Cuinhane 17 UEM - Digital

2.2. Descrio fsica (pinos)

2.2. Descrio fsica (pinos)

_______ BUSRQ (ENTRADA) BUS REQUEST: Requisita UCP os barramentos de dados, de endereo e de controle fazendo com que a UCP os coloque em tri-state. Deste modo a UCP deixa de os usar permitindo que os perifricos o faam _______ BUSAK(SADA): BUS ACKNOWLEDGE: Indica o sinal BUSRQ foi reconhecido e que os perifricos podem controlar os trs barramentos solicitados ____ CLK (ENTRADA) CLOCK PHASE: Entrada de relgio requerendo um resistor de 330 Ohm para servir de pull-up ligado Vcc

(P)(C) A.B.Cuinhane

18 UEM - Digital

Electrnica Digital II

2.3.1 PIO Parallel Input/Outup Device Input/Outup

A entrada e sada de dados para o ambiente do Z80 feita atravs de portas paralelas ou seriais A memria ROM e RAM (no nvel Cache e Principal) so os utentes principais dos barramentos de dados e de endereo. Funcionam alta velocidade e facilmente dialogam com a CPU. Por este motivo a entrada e sada de dados para estes dispositivos feita directamente. Alis, deve ser feita desta maneira pois esta parte da memria usada para conservar os dados de uso temporrio Quando se trata de receber ou entregar dados a questo muda. Porque lidar com dispositivos perifricos necessrio encontrar uma forma de adaptar tanto as velocidades como a forma de transporte (se paralelo ou serial) de dados.

19 UEM - Digital 20 UEM - Digital

2.3. Dispositivos de Entrada e Sada

NOTA: O estudante deve ler a informao adicional nos livros 2 e 3 da bibliografia recomendada

(P)(C) A.B.Cuinhane

(P)(C) A.B.Cuinhane

2.3.1 PIO Parallel Input/Outup Device Input/Outup

2.3.1 PIO Parallel Input/Outup Device Input/Outup

Caractersticas da PIO

Todas as entradas e sadas so compatveis com TTL Alimentado a 5V e uma nica fase de Ck Possui dois portos completamente independentes com o linhas bidirecionais cada um, para inteface com perifricos Possui um controle de transferncia de dados com linhas handshake controlando o fluxo de dados em ambos os sentidos simultaneamente Possui uma interrupo em srie (Daisy Chain) em que se programa um vector que coloca os perifricos em srie conforme a prioridade Pode ser programa para operar em 4 modos: MODO 0 Byte de sada MODO 1 Byte de entrada MODO 2 Byte bidirecional MODO 3 Bit controlado

(P)(C) A.B.Cuinhane 22 UEM - Digital

A PIO programvel pela UCP para ser interfacear um grande nmero de perifricoas com impressoras, teclado, mostradores, etc. A entrada/sada de dados feita atravs do circuito PIO Perallel Input Output que comporta duas portas de 8 bits cada. Como a PIO funciona no modo paralelo, todos os 8 bits so recebido/entregues ao mesmo tempo Uma das caracteristicas de destaque da PIO o circuito de controle de interrupes que permite uma interao eficaz entre a UCP e os perifricos sem necessidade de circuitos externos adicionais. Alm disso, depedendo da preprogramao, a PIO pode interromper a UCP se condies especiais pr-fixadas ocorrem no dispositivo perifrico (por exemplo uma tecla premida, pode levar a UCP a atender o teclado)

(P)(C) A.B.Cuinhane 21 UEM - Digital

2.3.1 PIO Parallel Input/Outup Device Input/Outup

Arquitectura Geral Da PIO

Linhas de dados

2.3.1 PIO Parallel Input/Outup Device Input/Outup

Arquitectura Geral Da PIO A PIO consiste internamente dum circuito de interface com o baramento de dados, um de controle interno, um circuito de controle de interrupes e os circuitos dos portos em si. A PIO pode interfacear a UCP directamente com qualquer perifrico mas se a quantidade destes for elevado poder ser necessrio circuitos externos adicionais como descodificadores de endereo ou registos temporrios(buffer).

Interface para o barramento de dados

Linhas de controle

Linhas de controle de interrupo

Controle interno

Controle de interrupo

Porto A

Linhas de dados/ controle Linhas de handshake

Porto B

Linhas de dados/ controle

(P)(C) A.B.Cuinhane

23 UEM - Digital

(P)(C) A.B.Cuinhane

24 UEM - Digital

Electrnica Digital II

2.3.1 PIO Parallel Input/Outup Device Input/Outup

Arquitectura Interna Do Porto

2.3.1 PIO Parallel Input/Outup Device Input/Outup

Arquitectura Interna Do Porto Os dois portos so completamente idnticos e so compostos por 6 registos gerais e um circuito hand-shake: 1 registo de 8 bits para entrada de dados 1 registo de 8 bits para sada de dados 1 registo de 8 bits para o vector da mscara 1 registo de 8 bits para gesto do sentido(saida/entrada) 1 registo de 2 bits para controle do modo e 1 registo de 2 bits para controle de mscara

Registador de Controle de Mscara

Registador de Controle de Modo

Registador de Mscara

Registador de Seleo Entrada/Sada

Registador de Entrada de dados

Registador de Sada de dados

Controle handshake

Linhas de dados/ controle do perifrico

Strob

Ready

(P)(C) A.B.Cuinhane

25 UEM - Digital

(P)(C) A.B.Cuinhane

26 UEM - Digital

2.3.1 PIO Parallel Input/Outup Device Input/Outup

Arquitectura Interna Do Porto Registos de Entrada e Sada de Dados: A transferencia de dados entre o a UCP e o perifrico feita atravs destes registos. Quando a UCP quer entregar dados ao perifrico, escreve-os no registo de sada. Quando o perifrico quer entregar dados UCP escreve-os no registo de entrada. Registo Direccional (gesto do sentido): usado no modo 3 para definir o sentido em cada Bit. Cada bit deste registo correponde uma linha do barramento de dados. Se o bit deste registo for 0 a linha correspondente sada, se for 1 a linha ser entrada. Controle handshake Determina a estrutura de interupes no sistema UCP-Perifrico atravs da gerao da cadeia de prioriade de interruptores. O dispositivos prioritrios podem atrair para si a ateno dos menos. 27

(P)(C) A.B.Cuinhane UEM - Digital

2.3.1 PIO Parallel Input/Outup Device Input/Outup

Arquitectura Interna Do Porto Registo Mscara/Controle da Mscara: O registo Mscara tambm usado no modo 3 juntamente com a interrupo que tem sua ocorrncia relacionada com condies especiais do perifrico. Neste registo pragramado a palvra (ou vector) que corresponde condio que se deseja observar. Se um bit, ou conjunto de bit, satisfazer uma condio ser gerada uma interrupo. A gerao da interrupo pode ser no modo AND, quando todos os bits forem activos ou modo OR, quando pelo menos um estiver activo

Registo de Controle de Modo: programada pela UCP de modo a seleccionar um dos 4 modos de funcionamento da PIO

(P)(C) A.B.Cuinhane 28 UEM - Digital

2.3.2 CTC Counter Timer Circuit

CTC um circuito Contador/Marcador do tempo composto por 4 canais independentes e que tm a funo de contar ou marcar o tempo em sistemas que usam microprocessadores. programado pela UCP e tema as eseguintes caractersticas: Entradas e sadas compatveis com TTL No preciso circuito extra para controle das interrupes Certas condies podem ser programadas quando num canal a contagem decresce at Zero Cada canal pode ser programado para funcionar no modo contador (Counter) ou temporizador(Timer)

2.3.3 Programao das Entradas e Sadas

O sistema utilisado no laboratrio de Digital, o MIC960/MAT980 usa o dispositivo Z8536 que comporta alm do PIO o CTC A entrada e sada de dados feita atravs das portas A e B que so vistas como locais de memria pelo processador. Portanto tm endereos Os pinos das portas so bidirecionais. Mas apontam para uma direo de cada vez e possvel program-los individualmente como foi visto na descrio da PIO. Normalemente so todas entradas. Destaquemos em cada porta dois registos: o Registo de dados e o Direcional (Fig.6.5). O registo Direcional determina quais pinos so entrada e quais so sada O registo de dados guarda dados que entram/saem da porta. um registo bidirecional

(P)(C) A.B.Cuinhane 30 UEM - Digital

(P)(C) A.B.Cuinhane

29 UEM - Digital

Electrnica Digital II

2.3.3 Programao das Entradas e Sadas

End=02

Pinos da Porta A

2.3.3 Programao das Entradas e Sadas

End=23 Fig.6.5

Registo da porta Registo Direccional A da porta A

A programao feita atravs do Registo de Controle cujo endereo 03

De/Para Pinos da Porta B Registo da porta Registo Direccional B da porta B

Dois Passos para configurar uma porta 1. Escrever o endereo do Registo Direcional (23 ou 2B) no Registo de Controle (03). Isto faz com que Registo de Controle aponte para o Registo Direcional desejado (23 ou 2B). 2. O valor que se deseja escrever no Registo Direcional (23 ou 2B) escrito no Registo de Controle (03) o que na verdade coloca os dados no Registo Direcional (23 ou 2B) e programa os pinos.

A programao dos pinos bidirecionais funciona de acordo com o seguinte critrio: Sada: Bit correspondente no Registo de Controle = 0 Entrada: Bit correspondente no Registo de Controle = 1

(P)(C) A.B.Cuinhane 32 UEM - Digital

End=01

(P)(C) A.B.Cuinhane

End=2B

31 UEM - Digital

2.3.3 Programao das Entradas e Sadas

Exemplo: Programar o porto A como sada nos 4 bMs e entradas nos 4 bms (ou seja 0000 1111) Instruo Comentrio LD A,23 Carrega o Acumulador com um dado (23) que corresponde ao endereo do registo direcional do porto A (RDA) Envia para o Registo de Controle (03) o nmero 23. isto aponta para o RDA Carrega o Acumulador com um dado (0F) Envia para o Registo de Controle (03) o numero que est no acumulador (0F)

OUT (03),A LD A,0F OUT (03),A

Lembrar que no projecto do Registo universal temos o selector de direco. Pois ento o Registo Direcional actua nos bits selectores de direco. 33

(P)(C) A.B.Cuinhane UEM - Digital

Electrnica Digital II

Potrebbero piacerti anche

- Introdução Assembly MIPSDocumento22 pagineIntrodução Assembly MIPSapenasscribdNessuna valutazione finora

- Relatorio PIC 16F690 Rev01Documento19 pagineRelatorio PIC 16F690 Rev01faeduardoNessuna valutazione finora

- S7 300 Cpu 315 2DPDocumento35 pagineS7 300 Cpu 315 2DPRolando PedreiraNessuna valutazione finora

- Apostila 8051Documento86 pagineApostila 8051Beatriz MariotoNessuna valutazione finora

- PLC Estudo DirigidoDocumento5 paginePLC Estudo DirigidoL BragaNessuna valutazione finora

- Simulado MicroprocessadoresDocumento3 pagineSimulado MicroprocessadoresandkavalheiroNessuna valutazione finora

- Microcontrolador 8051Documento55 pagineMicrocontrolador 8051Eduardo EduardoNessuna valutazione finora

- Ed2 - Lab Z80Documento10 pagineEd2 - Lab Z80Paulo MoreiraNessuna valutazione finora

- Lista 2Documento5 pagineLista 2FrânsciVieiraNessuna valutazione finora

- Apontamentos Teoricos e Praticos de TAC - 2009 - 2010V7Documento101 pagineApontamentos Teoricos e Praticos de TAC - 2009 - 2010V7Ricardo Santo AntonioNessuna valutazione finora

- Calculadora DigitalDocumento4 pagineCalculadora DigitalAdrian AlanNessuna valutazione finora

- 1b - Apostila Curso PLC - Automação PDFDocumento18 pagine1b - Apostila Curso PLC - Automação PDFMarcelo SouzaNessuna valutazione finora

- Micro ProcessadorDocumento5 pagineMicro ProcessadorAdriel MatieloNessuna valutazione finora

- Técnica de Multiplexação Com ArduinoDocumento23 pagineTécnica de Multiplexação Com ArduinoAlfredo Meurer JuniorNessuna valutazione finora

- Microcontroladores e MicroprocessadoresDocumento9 pagineMicrocontroladores e MicroprocessadoresRenato Monteiro BatistaNessuna valutazione finora

- Microcontrolador PIC16F877ADocumento40 pagineMicrocontrolador PIC16F877AMarcelo_Donisete100% (3)

- Conhecendo CuscopicDocumento4 pagineConhecendo CuscopicRafael Pereira Silva0% (1)

- LISTA ExemploDocumento8 pagineLISTA ExemploslytheriNessuna valutazione finora

- Apostila - Microcontrolador PIC16F84 PDFDocumento116 pagineApostila - Microcontrolador PIC16F84 PDFDaniel HenriqueNessuna valutazione finora

- Trabalho Microcontrolador UnipDocumento12 pagineTrabalho Microcontrolador UnipPedro MaruggiNessuna valutazione finora

- CLP Apostila Siemes S7 300Documento159 pagineCLP Apostila Siemes S7 300Darlan Leite100% (10)

- Arquitectura e Princípio de Funcionamento Do 8085Documento52 pagineArquitectura e Princípio de Funcionamento Do 8085Stanislau Escondido CadeadoNessuna valutazione finora

- Projetos Com Stm8s103f3 Programado Em Arduino - Parte XxxDa EverandProjetos Com Stm8s103f3 Programado Em Arduino - Parte XxxNessuna valutazione finora

- Projetos Com Arm Programado Em Arduino Com Base No Modelo Stm32f103c8 Parte LxiiiDa EverandProjetos Com Arm Programado Em Arduino Com Base No Modelo Stm32f103c8 Parte LxiiiNessuna valutazione finora

- Actividade 3 de Intrimentacao-1Documento9 pagineActividade 3 de Intrimentacao-1nicotembe7Nessuna valutazione finora

- Sap 2 PDFDocumento38 pagineSap 2 PDFdeapledNessuna valutazione finora

- UC-Unidade2-2 - Representação Dos Dados e Portas LógicasDocumento24 pagineUC-Unidade2-2 - Representação Dos Dados e Portas LógicasEmanuel BarcelosNessuna valutazione finora

- Micro Control Ad orDocumento44 pagineMicro Control Ad orpissini-1Nessuna valutazione finora

- Apostila de PLC AC500 Módulo IDocumento38 pagineApostila de PLC AC500 Módulo IdepimentaNessuna valutazione finora

- Apostila de CLP - Blocos LogicosDocumento32 pagineApostila de CLP - Blocos Logicosjucadosb100% (4)

- Clpcompleta 120821073625 Phpapp01Documento45 pagineClpcompleta 120821073625 Phpapp01CARLOS BARBOSANessuna valutazione finora

- Z-80 - ApresentaçãoDocumento108 pagineZ-80 - ApresentaçãoWallace Teixeira100% (1)

- Projetos Com Arm Programado Em C No Cubeide Com Base No Modelo Stm32f103c8 Parte ViDa EverandProjetos Com Arm Programado Em C No Cubeide Com Base No Modelo Stm32f103c8 Parte ViNessuna valutazione finora

- MICROCONTROLADORES 3 16f887Documento15 pagineMICROCONTROLADORES 3 16f887Pablo RodasNessuna valutazione finora

- ESTAÇÃO PendriveDocumento29 pagineESTAÇÃO PendriveRicardoNessuna valutazione finora

- Projetos No Vb Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IxDa EverandProjetos No Vb Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IxNessuna valutazione finora

- Lista de Exercícios II - V1Documento13 pagineLista de Exercícios II - V1nastaciabrNessuna valutazione finora

- Projeto HCS08Documento15 pagineProjeto HCS08pedrohr6789Nessuna valutazione finora

- Exercicios M1 2019Documento6 pagineExercicios M1 2019EduardoNessuna valutazione finora

- Microcontrolador 01 PDFDocumento21 pagineMicrocontrolador 01 PDFlidiomar10Nessuna valutazione finora

- Aula 01 - Introducao e Arquitetura Basica Do CLPDocumento29 pagineAula 01 - Introducao e Arquitetura Basica Do CLPPedro Vieira100% (2)

- Apostila Siemes S7 300Documento159 pagineApostila Siemes S7 300murilo monteiroNessuna valutazione finora

- Microcontrolador 8031Documento5 pagineMicrocontrolador 8031idalmirNessuna valutazione finora

- Projetos No Vc# Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IxDa EverandProjetos No Vc# Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IxNessuna valutazione finora

- Projetos Com Stm8s103f3 Programado Em Arduino - Parte XxvDa EverandProjetos Com Stm8s103f3 Programado Em Arduino - Parte XxvNessuna valutazione finora

- Z80 PIO FuncionamentoDocumento25 pagineZ80 PIO FuncionamentoAlfredo Meurer JuniorNessuna valutazione finora

- Slide Do Microcontrolador Pic 16F628 - Aula1Documento38 pagineSlide Do Microcontrolador Pic 16F628 - Aula1NandoNessuna valutazione finora

- Apostila C PICDocumento276 pagineApostila C PICClovis RodriguesNessuna valutazione finora

- Capitulo 6.introducao Aos ComputadoresDocumento18 pagineCapitulo 6.introducao Aos ComputadoresEsselino Luis RaimundoNessuna valutazione finora

- Lista 3 - Marcone Gabriel Da SilvaDocumento6 pagineLista 3 - Marcone Gabriel Da SilvaMARCONE GABRIEL DA SILVANessuna valutazione finora

- Estrutura de Um CLPDocumento12 pagineEstrutura de Um CLPSebastiao SilvaNessuna valutazione finora

- S7 AvançadoDocumento372 pagineS7 AvançadoIvanir Ferreira da SilvaNessuna valutazione finora

- Manual x99 P4.en - PTDocumento45 pagineManual x99 P4.en - PTDenis BrussaNessuna valutazione finora

- Aula 2013 PDFDocumento89 pagineAula 2013 PDFJosias Josias CordeiroNessuna valutazione finora

- Apostila de Conceitos Basicos em TIDocumento5 pagineApostila de Conceitos Basicos em TICris67% (3)

- CSI 3301 - Introdução Aos Sistemas OperativosDocumento100 pagineCSI 3301 - Introdução Aos Sistemas OperativoszeferinoNessuna valutazione finora

- Microcontrolador 8051 - Detalhado (Scan) PDFDocumento233 pagineMicrocontrolador 8051 - Detalhado (Scan) PDFPaulo RiosNessuna valutazione finora

- Arquitetura e Organização - 1 PDFDocumento21 pagineArquitetura e Organização - 1 PDFEduardo TedeschiNessuna valutazione finora

- Hardware e SoftwareDocumento88 pagineHardware e SoftwareNalberth SilvaNessuna valutazione finora

- Cap - 01 CLPDocumento15 pagineCap - 01 CLPWagner RibeiroNessuna valutazione finora

- Catálogo Max LíderDocumento4 pagineCatálogo Max LíderEdson Francisco Querino JuniorNessuna valutazione finora

- 2 Ano Leec GDocumento24 pagine2 Ano Leec GCarla CarneiroNessuna valutazione finora

- Apostila UFMG Programação de ComputadoresDocumento220 pagineApostila UFMG Programação de ComputadoresRafael Gomes100% (1)

- Python Learn (Portuguese) PDFDocumento258 paginePython Learn (Portuguese) PDFBárbara F. AlmeidaNessuna valutazione finora

- Estudo de Performance Das Arquiteturas Risc e CiscDocumento6 pagineEstudo de Performance Das Arquiteturas Risc e CiscGeraldo Rabelo JúniorNessuna valutazione finora

- OSDocumento24 pagineOSneobuxbrNessuna valutazione finora

- Arquitetura e Organização de Computadores Conceitos Básicos de Arquitetura e Organização de ComputadoresDocumento9 pagineArquitetura e Organização de Computadores Conceitos Básicos de Arquitetura e Organização de ComputadoresSafa dadaNessuna valutazione finora

- 1794 Um002 - FR PDocumento74 pagine1794 Um002 - FR Phmltdt9221Nessuna valutazione finora

- (Org e Arq) Aula 08 - Implementação MulticicloDocumento50 pagine(Org e Arq) Aula 08 - Implementação MulticicloValdir JuniorNessuna valutazione finora

- Aula - ProcessadoresDocumento51 pagineAula - ProcessadoresmjvelardeNessuna valutazione finora

- 03 Apostila Versao Digital Nocoes de Informatica 020.676.151!14!1611765338Documento541 pagine03 Apostila Versao Digital Nocoes de Informatica 020.676.151!14!1611765338Josué Leal MouraNessuna valutazione finora

- Módulo I - Fundamentos de Sistemas MicroprocessadosDocumento98 pagineMódulo I - Fundamentos de Sistemas Microprocessadosendersonbh100% (1)

- Sony Ms70 Mbx-160 - Rev 0.30Documento53 pagineSony Ms70 Mbx-160 - Rev 0.30habeloskasNessuna valutazione finora

- FortiGate - Security - 6.4 - Study - Guide Online 1 100 1 50.en - PTDocumento50 pagineFortiGate - Security - 6.4 - Study - Guide Online 1 100 1 50.en - PTMarceloeKeila TrindadeNessuna valutazione finora

- Arquitetura e Organização de ComputadoresDocumento3 pagineArquitetura e Organização de ComputadoresXavier JoaquimNessuna valutazione finora

- Lan House PDFDocumento57 pagineLan House PDFDaniel SammarcoNessuna valutazione finora

- Desenho Auxiliado Por ComputadorDocumento84 pagineDesenho Auxiliado Por ComputadormrcrowleyyyNessuna valutazione finora

- Programação C para Microcontroladores 8051 (WWW - Mecatronicadegaragem.blogspot - Com)Documento335 pagineProgramação C para Microcontroladores 8051 (WWW - Mecatronicadegaragem.blogspot - Com)maril3Nessuna valutazione finora

- 50 Questoes de Informatica Basica (50 Questões Básicas de Informática)Documento6 pagine50 Questoes de Informatica Basica (50 Questões Básicas de Informática)Rodrigo Duarte84% (92)

- Funções Do Sistema OperativoDocumento5 pagineFunções Do Sistema OperativoCarlos PaivaNessuna valutazione finora

- Apostila AssemblyDocumento70 pagineApostila AssemblyMarcio Eiji TamuraNessuna valutazione finora

- Manual MetrovalDocumento23 pagineManual MetrovalJânio AnselmoNessuna valutazione finora