Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Signal Integrity: Signal Integrity or SI Is A Set of Measures of The Quality of An

Caricato da

Tony LeeDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Signal Integrity: Signal Integrity or SI Is A Set of Measures of The Quality of An

Caricato da

Tony LeeCopyright:

Formati disponibili

Signal integrity

Signal integrity or SI is a set of measures of the quality of an electrical signal. In digital electronics, a stream of binary values is represented by a voltage (or current) waveform. However, digital signals are fundamentally analog in nature, and all signals are subject to effects such as noise, distortion, and loss. Over short distances and at low bit rates, a simple conductor can transmit this with sufficient fidelity. At high bit rates and over longer distances or through various mediums, various effects can degrade the electrical signal to the point where less-than-ideal conditions (errors) occur, and the system or device fails. Signal integrity engineering is the task of analyzing and mitigating these effects. Some of the main issues of concern for signal integrity are ringing, crosstalk, ground bounce, distortion, signal loss, and power supply noise.

Finding IC signal integrity problems

Typically, an IC designer would take the following steps for SI verification:

Perform a layout extraction to get the parasitics associated with the layout. Usually worst-case parasitics and best-case parasitics are extracted and used in the simulations. For ICs, unlike PCBs, physical measurement of the parasitics is almost never done, since in-situ measurements with external equipment are extremely difficult. Furthermore, any measurement would occur after the chip has been created, which is too late to fix any problems observed. Create a list of expected noise events, including different types of noise, such as coupling and charge sharing. Create a model for each noise event. It is critical that the model be as accurate as possible. For each signal event, decide how to excite the circuit so that the noise event will occur.

Create a SPICE (or another circuit simulator) netlist that represents the desired excitation, to include as many effects (such as parasitic inductance and capacitance, and various distortion effects) as possible. Run SPICE simulations. Analyze the simulation results and decide whether any re-design is required. It is common to analyze the results with an eye pattern and by calculating a timing budget[3].

Modern signal integrity tools for IC design perform all these steps automatically, producing reports that give a design a clean bill of health, or a list of problems that must be fixed. However, such tools generally are not applied across an entire IC, but only selected signals of interest.

Fixing IC signal integrity problems

Once a problem is found, it must be fixed. Typical fixes for IC on-chip problems include:

Removing impedance discontinuities. Finding places where significant shifts in the impedance exist and adjusting the geometry of the path to shift the impedance to better match the rest of the path. Driver optimization. You can have too much drive, and also not enough. Buffer insertion. In this approach, instead of upsizing the victim driver, a buffer is inserted at an appropriate point in the victim net. Aggressor downsizing. This works by increasing the transition time of the attacking net by reducing the strength of its driver. Add Shielding. Add shielding of critical nets or clock nets using GND and VDD shields to reduce the effect of Crosstalk. (This technique may lead to routing overhead.) Routing changes. Routing changes can be very effective in fixing noise problems, mainly by reducing the most troublesome coupling effects via separation.

Each of these fixes may possibly cause other problems. This type of issue must be addressed as part of design flows and design closure. Re-analysis after design changes is a prudent measure.

Potrebbero piacerti anche

- Areva&hvdc PDFDocumento167 pagineAreva&hvdc PDFAbdallah Salem100% (1)

- FVofDiffOpAmp WPDocumento51 pagineFVofDiffOpAmp WPmarius260Nessuna valutazione finora

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsDa EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsNessuna valutazione finora

- SM6 - 24 - CT CatalogueDocumento20 pagineSM6 - 24 - CT Catalogueluutrudulieu3100% (2)

- Ee403 배현민 교수님 2013 봄Documento3 pagineEe403 배현민 교수님 2013 봄박철준Nessuna valutazione finora

- ME Notes Unit 4 Part 3 Low Power IC and RFICsDocumento5 pagineME Notes Unit 4 Part 3 Low Power IC and RFICssayan.transcuratorsNessuna valutazione finora

- Density Based Traffic Control SYSTEM..... : RishiDocumento23 pagineDensity Based Traffic Control SYSTEM..... : RishiStenil AntonyNessuna valutazione finora

- !!!! Signal Integrity Considerations For High Speed Digital HardwareDocumento12 pagine!!!! Signal Integrity Considerations For High Speed Digital HardwarePredrag PejicNessuna valutazione finora

- Introduction To The Design of Analogs by Allen and HollbergDocumento14 pagineIntroduction To The Design of Analogs by Allen and HollbergKiran KirruNessuna valutazione finora

- In-Fixture Measurements Using Vector Network Analyzers: Keysight TechnologiesDocumento33 pagineIn-Fixture Measurements Using Vector Network Analyzers: Keysight TechnologiesPaulo Tibúrcio PereiraNessuna valutazione finora

- What Is Signal Integrity A Comprehensive OverviewDocumento9 pagineWhat Is Signal Integrity A Comprehensive OverviewjackNessuna valutazione finora

- Signal Integrity Analysis - Digital Backend Timing Analysis-CSDN BlogDocumento2 pagineSignal Integrity Analysis - Digital Backend Timing Analysis-CSDN BlogAgnathavasiNessuna valutazione finora

- AP0107 Impedance-Controlled RoutingDocumento6 pagineAP0107 Impedance-Controlled RoutingdrakenhavenNessuna valutazione finora

- Signal Integrity Analysis in PCB For High Speed Digital Circuit Design T.S. Srinivasan, J. Uma, V. PrabhuDocumento8 pagineSignal Integrity Analysis in PCB For High Speed Digital Circuit Design T.S. Srinivasan, J. Uma, V. PrabhusalehNessuna valutazione finora

- PPTDocumento8 paginePPTMD IshakNessuna valutazione finora

- SIMULIA EM EMC For Electonics DatasheetDocumento3 pagineSIMULIA EM EMC For Electonics Datasheetkutlu küçükvuralNessuna valutazione finora

- Cad PD AssignmentDocumento19 pagineCad PD AssignmentRadhika KalawatNessuna valutazione finora

- High Speed Digital Design PrinciplesDocumento16 pagineHigh Speed Digital Design PrinciplesXiaofang ChenNessuna valutazione finora

- ASIC Interview Questions 1Documento5 pagineASIC Interview Questions 1ramNessuna valutazione finora

- Design Techniques For EMC CompleteDocumento156 pagineDesign Techniques For EMC Completec_rodolfo_rodrigues5109Nessuna valutazione finora

- Altium WP Adopting Signal Integrity in High Speed Design WEBDocumento4 pagineAltium WP Adopting Signal Integrity in High Speed Design WEBjagadees21Nessuna valutazione finora

- Tutorial-Advanced Digital Design Using Sonnet GK 3Documento44 pagineTutorial-Advanced Digital Design Using Sonnet GK 3Srinivasa Rao SankrantiNessuna valutazione finora

- ASIC Interview QuestionsDocumento6 pagineASIC Interview QuestionsNandeesh VeerannaNessuna valutazione finora

- Final Project Report E3390 Electronic Circuits Design Lab: Brian Lambson Andrew HsuDocumento9 pagineFinal Project Report E3390 Electronic Circuits Design Lab: Brian Lambson Andrew HsuVvb SatyanarayanaNessuna valutazione finora

- School of Electronics and Communication Engineering B.TECH (2018-2019) VII SemesterDocumento28 pagineSchool of Electronics and Communication Engineering B.TECH (2018-2019) VII SemesterVikas BhatiNessuna valutazione finora

- (TI) Frequency Response Measurements For Switching Power SuppliesDocumento13 pagine(TI) Frequency Response Measurements For Switching Power Suppliesdsshin_psNessuna valutazione finora

- ENOB Overall AccuracyDocumento8 pagineENOB Overall Accuracybrqj6nNessuna valutazione finora

- Lab1-Introduction To DSO ND FGDocumento11 pagineLab1-Introduction To DSO ND FGHamza AliNessuna valutazione finora

- Introduction To High-Speed Digital Design Principles: BackgroundDocumento10 pagineIntroduction To High-Speed Digital Design Principles: BackgroundGuilherme AFNessuna valutazione finora

- From Sand To Silicon "An Eagle View of Chip Making"Documento36 pagineFrom Sand To Silicon "An Eagle View of Chip Making"DHANAGOPAL R DHANAGOPAL RNessuna valutazione finora

- Vlsi Cmos Interview Q&A Part-3Documento7 pagineVlsi Cmos Interview Q&A Part-3harshaNessuna valutazione finora

- Managing Ground PowerDocumento4 pagineManaging Ground PowerOTTONessuna valutazione finora

- AP2402630 EMC Guidelines 1Documento63 pagineAP2402630 EMC Guidelines 1Tuấn Nguyễn TrungNessuna valutazione finora

- Electronic Test Instrument Voltages Potential Differences: Cathode-Ray Oscilloscope (CRO)Documento7 pagineElectronic Test Instrument Voltages Potential Differences: Cathode-Ray Oscilloscope (CRO)Vijay KothaleNessuna valutazione finora

- ESC 201A ExpDocumento9 pagineESC 201A Expanshikamittal2626Nessuna valutazione finora

- Techniques Troubleshooting: .Implication Note 163-1Documento30 pagineTechniques Troubleshooting: .Implication Note 163-1JC ZuletNessuna valutazione finora

- Batch 4 Major Project PPT WaveletDocumento27 pagineBatch 4 Major Project PPT WaveletAdluri srikarNessuna valutazione finora

- Fault Detection in TM LineDocumento25 pagineFault Detection in TM Linenaveen gNessuna valutazione finora

- 2A2 Signal Conditioning L1 Notes CollinsDocumento138 pagine2A2 Signal Conditioning L1 Notes CollinsKev107Nessuna valutazione finora

- Pc-Based Digital Oscilloscope Using Pic Microcontroler: Main Project Report OnDocumento34 paginePc-Based Digital Oscilloscope Using Pic Microcontroler: Main Project Report OnBini Joy100% (2)

- EMC Design Guidelines For Microcontroller Board Layout: Never Stop ThinkingDocumento63 pagineEMC Design Guidelines For Microcontroller Board Layout: Never Stop ThinkingMr CdtNessuna valutazione finora

- What Is Metal Fill? Why The Metal Fill Is Required?Documento8 pagineWhat Is Metal Fill? Why The Metal Fill Is Required?Sai KumarNessuna valutazione finora

- Functions of Image PlanesDocumento5 pagineFunctions of Image PlanesSanket PatilNessuna valutazione finora

- Choosing The Right Electronics Manufacturing Testing EquipmentDocumento6 pagineChoosing The Right Electronics Manufacturing Testing EquipmentjackNessuna valutazione finora

- Short Circuit Detection With ArduinoDocumento20 pagineShort Circuit Detection With ArduinoAung MyatNessuna valutazione finora

- Electrical Project1234Documento35 pagineElectrical Project1234Sahil SinghNessuna valutazione finora

- The Digital Circuit Design Process and Its AdvantagesDocumento7 pagineThe Digital Circuit Design Process and Its AdvantagesjackNessuna valutazione finora

- Comparison of Common Encoder Output SignalsDocumento12 pagineComparison of Common Encoder Output Signalssaberleffi1Nessuna valutazione finora

- Tanner ManualDocumento60 pagineTanner ManualFahim Ahmed100% (1)

- Experiment 1 Familiarization With Laboratory Instruments: Oscilloscope, Function Generator, Digital Multimeter, and DC Power SupplyDocumento7 pagineExperiment 1 Familiarization With Laboratory Instruments: Oscilloscope, Function Generator, Digital Multimeter, and DC Power Supplypappuyadav1996Nessuna valutazione finora

- Numerical RelayingDocumento49 pagineNumerical RelayingBhargav PandyaNessuna valutazione finora

- Signal Integrity PDFDocumento21 pagineSignal Integrity PDFmosa totahNessuna valutazione finora

- Project25 Design ReviewDocumento11 pagineProject25 Design Reviewnegrea_c8079Nessuna valutazione finora

- A Low Noise Power 45 NM Technology Based Simultaneous Switching Noise (SSN) Reduction Model For Mixed Signal VLSI CircuitsDocumento7 pagineA Low Noise Power 45 NM Technology Based Simultaneous Switching Noise (SSN) Reduction Model For Mixed Signal VLSI Circuitsdwie2254Nessuna valutazione finora

- LAB01Documento23 pagineLAB01زياد عبدالله عبدالحميدNessuna valutazione finora

- Introduction To Circuit SimulationDocumento15 pagineIntroduction To Circuit SimulationArryshah Dahmia0% (2)

- Underground Cable Fault ReportDocumento38 pagineUnderground Cable Fault ReportNagendra S100% (1)

- He XR2206 Function Generator DIY Kit & Other GoodiesDocumento8 pagineHe XR2206 Function Generator DIY Kit & Other Goodiesluis cortelezziNessuna valutazione finora

- Testing StrategiesDocumento8 pagineTesting StrategiesJohnny Pancito Rodriguez100% (1)

- Hall-Effect Sensors: Theory and ApplicationDa EverandHall-Effect Sensors: Theory and ApplicationValutazione: 5 su 5 stelle5/5 (1)

- Digsilent Powerfactory: Technical Reference DocumentationDocumento29 pagineDigsilent Powerfactory: Technical Reference DocumentationHar HarNessuna valutazione finora

- Total Power Demand Calculation For ABD Ranchi Smart City PDFDocumento4 pagineTotal Power Demand Calculation For ABD Ranchi Smart City PDFthumula.rameshNessuna valutazione finora

- Past Jun - 18MDocumento4 paginePast Jun - 18MTucciy Alentine MaeNessuna valutazione finora

- Specifications: Varistor GNR20DDocumento5 pagineSpecifications: Varistor GNR20DjuniorNessuna valutazione finora

- Murata MA40 SERIESDocumento2 pagineMurata MA40 SERIESMiltonAlvaradoPonceNessuna valutazione finora

- Chapter5 PDFDocumento128 pagineChapter5 PDFTonmoyNessuna valutazione finora

- EIC Basic - 2 - Curriculum Basic Elektonika (Resisitor)Documento14 pagineEIC Basic - 2 - Curriculum Basic Elektonika (Resisitor)endayNessuna valutazione finora

- Isc N-Channel MOSFET Transistor 75N08: INCHANGE Semiconductor Product SpecificationDocumento2 pagineIsc N-Channel MOSFET Transistor 75N08: INCHANGE Semiconductor Product Specificationmateus santosNessuna valutazione finora

- ABB Ring Main Unit For The Secondary Distribution NetworkDocumento80 pagineABB Ring Main Unit For The Secondary Distribution NetworkVIJAY MOHAN DAVE67% (3)

- Electric Drives and Their ControlDocumento3 pagineElectric Drives and Their ControlNaren Singh TanwarNessuna valutazione finora

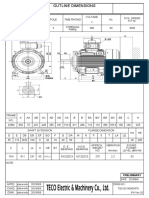

- 2019/9/9 Sales-Indo Sales-Indo Sales-Indo PN Ver:02: PreliminaryDocumento4 pagine2019/9/9 Sales-Indo Sales-Indo Sales-Indo PN Ver:02: PreliminaryCV buanaindahNessuna valutazione finora

- Digital Multimeter Selection GuideDocumento3 pagineDigital Multimeter Selection GuideThomas VargheseNessuna valutazione finora

- 02 SpectrophotometerDocumento40 pagine02 SpectrophotometerHassan GillNessuna valutazione finora

- Sony Klv-22ex300 Klv-26ex300 Klv-32ex300 Klv-32ex400 Klv-40ex400 Klv-46ex400 B L RDocumento67 pagineSony Klv-22ex300 Klv-26ex300 Klv-32ex300 Klv-32ex400 Klv-40ex400 Klv-46ex400 B L RDinuka MalinthaNessuna valutazione finora

- Aluminium Cantilever OCS3 - Brochure - EnglishDocumento29 pagineAluminium Cantilever OCS3 - Brochure - EnglishBee Jin Sook VerguetNessuna valutazione finora

- Solar Panel Sys WPS OfficeDocumento15 pagineSolar Panel Sys WPS OfficeFrank HayagNessuna valutazione finora

- JustAccepted EML 12 109Documento22 pagineJustAccepted EML 12 109Shridhar MathadNessuna valutazione finora

- Sirco M - Load Break Switches & Manual Change Over SwitchesDocumento2 pagineSirco M - Load Break Switches & Manual Change Over SwitchesThilinaNessuna valutazione finora

- Powe Electronics Unit 1Documento65 paginePowe Electronics Unit 1Ajju K AjjuNessuna valutazione finora

- Liebert Hipulse D Data SheetDocumento6 pagineLiebert Hipulse D Data SheetDharmesh ChanawalaNessuna valutazione finora

- VLF-60 DS EN EN Rev4 24Documento3 pagineVLF-60 DS EN EN Rev4 24juaan figueroaNessuna valutazione finora

- iPCB - Compair - 132RS - Delcos XLDocumento2 pagineiPCB - Compair - 132RS - Delcos XLAli Raza100% (1)

- Operacion y Mantenimiento de ReconectadoresDocumento5 pagineOperacion y Mantenimiento de ReconectadoresCUAL QUIERANessuna valutazione finora

- OS-5020 NewDocumento2 pagineOS-5020 Newadak avijitNessuna valutazione finora

- Chapter - 15: Some Natural PhenomenaDocumento28 pagineChapter - 15: Some Natural PhenomenaKrishnaveni Subramani SNessuna valutazione finora

- GZRW 30splextremeDocumento2 pagineGZRW 30splextremekamil palbickiNessuna valutazione finora

- Birwelco HT IgnitionDocumento4 pagineBirwelco HT Ignitioncharleselitb92Nessuna valutazione finora