Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Tut2 Toolflow

Caricato da

rakesherDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Tut2 Toolflow

Caricato da

rakesherCopyright:

Formati disponibili

Bits and Pieces of CS250s Toolow

CS250 Tutorial 2 (Version 092509a) September 25, 2009 Yunsup Lee

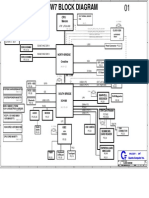

In this tutorial you will learn what each VLSI tools used in class are meant to do, how they ow, le extensions of their inputs and outputs. Figure 1 shows the CS250 toolow you will be using for the class. You will use Synopsys VCS (vcs) to simulate and debug your RTL design. After you get your design right, you will use Synopsys Design Compiler (dc shell-xg-t) to synthesize the design. Synthesis is the process of transforming an RTL model into a gate-level netlist. You will use Synopsys Formality (fm shell) to formally verify that the RTL model and the gate-level model match. VCS is used again to simulate the synthesized gate-level netlist. After obtaining a working gate-level netlist, you will use Synopsys IC Compiler (icc shell) to place and route the design. Placement is the process by which each standard cell is positioned on the chip, while routing involves wiring the cells together using various metal layers. The tools will provide feedback on the performance and area of your design after both synthesis and place and route. The results from place and route are more realistic but require much more time to generate. After place and route, you will generate and simulate the nal gate-level netlist using VCS. Finally you will use this gate-level simulation as a nal test for correctness and to generate transition counts for every net in the design. Synopsys PrimeTime PX (pt shell) takes these transition counts as input and correlate them with the capacitance values in the nal layout to produce estimated power measurements. Each section or subsection has a list of documents which are provided from Synopsys. The documents are located in the cs250 course locker (~cs250/docs/manuals) which can be accessed through the instructional machines.

Tools

Synopsys VCS

VCS is used to simulate your design. The design could be expressed in several dierent languages, however, we encourage you to use Verilog for this class. For more information on Verilog, take a look at the Language section in this tutorial. VCS takes a set of Verilog les as input and produces a simulator. When you execute the simulator you need some way to observe your design so that you can measure its performance and verify that it is working correctly. You can instruct the simulator to automatically write transition information about each signal in your design to a le. There is a standard text format for this type of signal transition trace information called the Value Change Dump format (VCD). Unfortunately, these textual trace les can become very large quickly, so Synopsys uses a proprietary compressed binary trace format called VCD Plus (VPD). You can view VPD les using a waveform viewer called Synopsys Discover Visual Environment (DVE). vcs-user-guide.pdf - VCS User Guide vcs-quick-reference.pdf - VCS Quick Reference

CS250 Tutorial 2 (Version 092509a), Fall 2009

Verilog Source (Behav)

Verilog Source (RTL)

Constraints

Std Cell Lib

VCS

VCS

Design Compiler

Behav Sim

RTL Sim

Guidance File

Gate Level Netlist

Constraints File

Timing Area

Execute Sim

Execute Sim

Formality

Design Vision GUI

VPD

Test Outputs

VPD

Test Outputs

Verification Resuls

IC Compiler (DP)

TLUplus Files

DVE GUI DVE GUI VCS

Floor Plan

Post Syn. Sim

IC Compiler (PAR)

Execute Sim

Gate Level Netlist

Timing Area

Layout

Constraints Parasitics File File

VPD

Test Outputs

VCS

IC Compiler GUI

Post PAR Sim

DVE GUI

Execute Sim

VPD

Test Outputs

DVE GUI

VPD2VCD

VCD

PrimeTime

Power Estimates

Figure 1: CS250 Toolow

CS250 Tutorial 2 (Version 092509a), Fall 2009 vcs dve-user-guide.pdf - Discovery Visual Environment User Guide vcs ucli-user-guide.pdf - Unied Command Line Interface User Guide

Synopsys Design Compiler

Design Compiler takes an RTL hardware description, timing constraints, and a standard cell library as input and produces a gate-level netlist as output. To take a closer look at the standard cell library you are using for the class, consult the Process section of this tutorial. Internally, a synthesis tool performs many steps including high-level RTL optimizations, RTL to unoptimized Boolean logic, technology independent optimizations, and nally technology mapping to the available standard cells. A synthesis tool is only as good as the standard cells which it has at its disposal. You get reports about the critical path of your synthesized design, area and power estimates, and resource mapping. You can also take advantage of Design Vision to visualize critical paths of your synthesis results, and schematics of the gate-level netlist. dc-user-guide.pdf - Design Compiler User Guide dc-quick-reference.pdf - Design Compiler Quick Reference dc-user-guide-cli.pdf - Design Compiler Command-Line Interface Guide dc-user-guide-tcl.pdf - Using Tcl With Synopsys Tools dc-user-guide-tco.pdf - Synopsys Timing Constraints and Optimization User Guide dc-reference-manual-opt.pdf - Design Compiler Optimization Reference Manual dc-reference-manual-presto-verilog.pdf - HDL Compiler Reference Manual dc-application-note-sdc.pdf - Synopsys Design Constraints Format Application Note dc dv-user-guide.pdf - Design Vision User Guide dc dv-tutorial.pdf - Design Compiler Tutorial Using Design Vision

Synopsys Formality

Formality is used to formally verify whether or not your RTL implementation and the synthesized gate-level netlist match. Formal verication utilizes mathematical techniques to compare the logic to be veried against either a logical specication or a reference design. Unlike verication through simulation, formal verication does not require input vectors. As it considers only logical functions during comparisons, it is independent of the designs physical properties, such as its layout and timing. fm-user-guide.pdf - Formality User Guide fm-quick-reference.pdf - Formality Quick Reference

Synopsys IC Compiler

IC Compiler takes as input a gate-level netlist, timing constraints, physical and timing libraries, and it generates as output a layout. It rst determines how each gate should be placed on the

CS250 Tutorial 2 (Version 092509a), Fall 2009

chip. Then it uses several heuristic algorithms to group related gates together and thus hopefully minimize routing congestion and wire delay. This tool will focus its eort on minimizing the delay through the critical path. To this end, it can resize gates, insert new buers, and even perform local resynthesis. icc-user-guide.pdf - IC Compiler Implementation User Guide icc-quick-reference.pdf - IC Compiler Quick Reference icc dp-user-guide.pdf - IC Compiler Design Planning User Guide

Synopsys PrimeTime PX

PrimeTime PX is an add-on feature to PrimeTime that accurately analyzes power dissipation of cell-based designs. PrimeTime PX supports two types of power analysis modes: averaged mode and time-based mode. Averaged mode calculates averaged power based on toggle rates. Timebased mode lets you know the peak power as well as the veraged power using gate-level simulation activity. pt px-user-guide.pdf - PrimeTime PX User Guide pt-quick-reference.pdf - PrimeTime Suite Quick Reference

Libraries and Process

You are using the Synopsys 90nm educational library for the class. It is a 1P9M (1 poly, 9 metal layers) 1.2V/2.5V process. The standard cells and other cells have been built using this design rules. The standard cell library has been created aimed at optimizing the main characteristics of designed ICs by its help. The cell library includes typical miscellaneous combinational and sequential logic cells for dierent drive strengths. Besides, the cell library contains the cells (isolation cells, level shifters, retention ipops, always-on buers, and power gating cells) which are required for dierent styles of low power (multi-voltage, multi-threshold) designs. The presence of all these cells provides the support of IC design with dierent core voltages to minimize dynamic and leakage power. The library comes with several static RAMs cells. SRAMs included in the library are synchronous dual-port SRAMs with write enable, output enable, and chip select on each port. The library also includes some megacells to support the open sparc design. They include various register les, translation lookaside buer (TLB), content-addressable memory (CAM), level 2 cache, and arrays. However, these cells are still in the process of development, so not many are currently available. Consult the databook for further information. synopsys-90nm-databook-stdcells.pdf - Digital Standard Cell Library Databook synopsys-90nm-databook-memories.pdf - Memory Databook synopsys-90nm-databook-opensparc.pdf - OpenSparc Megacell Databook

CS250 Tutorial 2 (Version 092509a), Fall 2009

DesignWare

DesignWare library is a collection of reusable circuit-design building blocks (components) that are tightly integrated into the Synopsys synthesis environment. DesignWare components that implement many of the built-in HDL operators are provided by Synopsys. These operators include +, , , <, >, <=, >=, and the operations dened by if and case statements. designware-intro.pdf - DesignWare Building Block IP Documentation Overview designware-user-guide.pdf - DesignWare Building Block IP designware-quick-reference.pdf - DesignWare Building Block IP Quick Reference designware-datasheets - Directory containing datasheets on each DW component

Language

You should use Verilog for the class. The CS250 ow only supports Verilog ocially at this moment. For language specications consult the following documents. verilog-language-spec-1995.pdf - Language specication for the original Verilog-1995 verilog-language-spec-2001.pdf - Language specication for Verilog-2001

File Extensions

*.v - Verilog source le. Normally its a source le your write. Design Compiler, and IC Compiler can use this format for the gate-level netlist. *.vg, .g.v - Verilog gate-level netlist le. Sometimes people use these le extension to dierentiate source les and gate-level netlists. *.svf - Automated setup le. This le helps Formality process design changes caused by other tools used in the design ow. Formality uses this le to assist the compare point matching and verication process. This information facilitates alignment of compare points in the designs that you are verifying. For each automated setup le that you load, Formality processes the content and stores the information for use during the name-based compare point matching period. *.ddc - Synopsys internal database format. This format is recommended by Synopsys to hand gate-level netlists. *.vcd - Value Change Dump format. This format is used to save signal transition trace information. This format is in text format, therefore, the trace le in this format can get very large quickly. There are tools like vcd2vpd, vpd2vcd, and vcd2saif switch back and forth between dierent formats. *.vpd - VCD Plus. This is a proprietary compressed binary trace format from Synopsys. This le format is used to save signal transition trace information as well. *.saif - Switching Activity Interchange Format. Its another format to save signal transition trace information. SAIF les support signals and ports for monitoring as well as constructs such as generates, enumerated types, records, array of arrays, and integers. *.tcl - Tool Command Language (Tcl) scripts. Tcl is used to drive Synopsys tools.

CS250 Tutorial 2 (Version 092509a), Fall 2009

*.sdc - Synopsys Design Constraints. SDC is a Tcl-based format. All commands in an SDC le conform to the Tcl syntax rules. You use an SDC le to communicate the design intent, including timing and area requirements between EDA tools. An SDC le contains the following information: SDC version, SDC units, design constraints, and comments. Consult dc-application-note-sdc.pdf for further information. *.lib - Technology Library source le. Technology libraries contain information about the characteristics and functions of each cell provided in a semiconductor vendors library. Semiconductor vendors maintain and distribute the technology libraries. In our case the vendor is Synopsys. Cell characteristics include information such as cell names, pin names, area, delay arcs, and pin loading. The technology library also denes the conditions that must be met for a functional design (for example, the maximum transition time for nets). These conditions are called design rule constraints. In addition to cell information and design rule constraints, technology libraries specify the operating conditions and wire load models specic to that technology. *.db - Technology Library. This is a compiled version of *.lib in Synopsys database format. *.plib - Physical Library source le. Physical libraries contain process information, and physical layout information of the cells. This information is required for oor planning, RC estimation and extraction, placement, and routing. *.pdb - Physical Library. This is a compiled version of *.plib in Synopsys database format. *.slib - Symbol Library source le. Symbol libraries contain denitions of the graphic symbols that represent library cells in the design schematics. Semiconductor vendors maintain and distribute the symbol libraries. Design Compiler uses symbol libraries to generate the design schematic. You must use Design Vision to view the design schematic. When you generate the design schematic, Design Compiler performs a one-to-one mapping of cells in the netlist to cells in the symbol library. *.sdb - Symbol Library. This is a compiled version of *.slib in Synopsys database format. *.sldb - DesignWare Library. This le contains information about DesignWare libraries. *.def - Design Exchange Format. This formats is often used in Cadence tools to represent physical layout. Synopsys tools normally use Milkyway format to save designs. *.lef - Library Exchange Format. Standard cells are often saved in this format. Cadence tools also often uses this format. Synopsys tools normally use Milkyway format for standard cells. *.rpt - Reports. This is not a proprietary format, its just a text format which saves generated reports by the tools when you use the automated makeles and scripts. *.tf - Vendor Technology File. This le contains technology-specic information such as the names, characteristics (physical and electrical) for each metal layer, and design rules. These information are required to route a design. *.itf - Interconnect Technology File. This le contains a description of the process crosssection and connectivity section. It also describes the thicknesses and physical attributes of the conductor and dielectric layers. *.map - Mapping le. This le aligns names in the vendor technology le with the names in the process *.itf le. *.tluplus - TLU+ le. These les are generated from the *.itf les. TLUPlus models are a set of models containing advanced process eects that can be used by the parasitic extractors in Synopsys place-and-route tools for modeling.

CS250 Tutorial 2 (Version 092509a), Fall 2009

*.spef - Standard Parasitic Exchange Format. File format to save parasitic information extracted by the place and route tool. *.sbpf - Synopsys Binary Parasitic Format. A Synopsys proprietary compressed binary format of the *.spef. Size of the le shrinks quite a bit using this format. Milkyway database The Milkyway database consists of libraries that contain information about your design. Libraries contain information about design cells, standard cells, macro cells, and so on. They contain physical descriptions, such as metal, diusion, and polygon geometries. Libraries also contain logical information (functionality and timing characteristics) for every cell in the library. Finally, libraries contain technology information required for design and fabrication. Milkyway provides two types of libraries that you can use: reference libraries and design libraries. Reference libraries contain standard cells and hard or soft macro cells, which are typically created by vendors. Reference libraries contain physical information necessary for design implementation. Physical information includes the routing directions and the placement unit tile dimensions, which is the width and height of the smallest instance that can be placed. A design library contains a design cell. The design cell might contain references to multiple reference libraries (standard cells and macro cells). Also, a design library can be a reference library for another design library. The Milkyway library is stored as a UNIX directory with subdirectories, and every library is managed by the Milkyway Environment. The top-level directory name corresponds to the name of the Milkyway library. Library subdirectories are classied into dierent views containing the appropriate information relevant to the library cells or the designs. In a Milkyway library there are dierent views for each cell, for example, NOR1.CEL and NOR1.FRAM. This is unlike a .db formatted library where all the cells are in a single binary le. With a .db library, the entire library has to be read into memory. In the Milkyway Environment, the Synopsys tool loads the library data relevant to the design as needed, reducing memory usage. The most commonly used Milkyway views are CEL and FRAM. CEL is the full layout view, and FRAM is the abstract view for place and route operations. simv - Compiled simulator. This is the output of vcs. In order to simulate, run the simulator by ./simv at the command line. alib-52 - characterized target technology library. A pseudo library which has mappings from Boolean functional circuits to actual gates from the target library. This library provides Design Compiler with greater exibility and a larger solution space to explore tradeos between area and delay during optimization.

Bonus: A Glossary from Design Compiler

The Design Compiler User Guide (Chapter GL) has a good glossary on general VLSI stu. If you are not familiar with the following keywords, we encourage you to take a look. You will see these terminologies in the labs and the tutorials a lot. annotation back-annotate

CS250 Tutorial 2 (Version 092509a), Fall 2009 cell clock clock gating clock latency clock skew clock source clock tree clock uncertainty core critical path datapath current design current instance design constraints false path fanin fanout fanout load atten forward-annotate generated clock hold time ideal clock ideal net input delay instance leaf cell link library multicycle path netlist operating conditions optimization output delay pad cell path group pin propagated clock real clock reference RTL setup time

CS250 Tutorial 2 (Version 092509a), Fall 2009 slack structuring synthesis symbol library target library technology library timing exception timing path transition delay ungroup uniquify virtual clock wire load model

Review

In this tutoiral you have learned what each VLSI tools are meant to do, how they ow, le extensions of their inputs and outputs. vcs-sim-behav vcs-sim-rtl dc-syn dc-syn vcs-sim-gl-syn icc-par vcs-sim-gl-par pt-pwr Synopsys Synopsys Synopsys Synopsys Synopsys Synopsys Synopsys Synopsys VCS VCS Design Compiler Formality VCS IC Compiler VCS PrimeTime PX Behavioral simulation RTL simulation Synthesis; RTL to gate-level netlist Formal verication Post synthesis gate-level simulation Place and Route; gate-level netlist to layout Post place and route gate-level simulation Power analysis

Acknowledgements

Many people have contributed to versions of this tutorial over the years. The tutorial was originally developed for CS250 VLSI Systems Design course at University of California at Berkeley by Yunsup Lee. Contributors include: Krste Asanovi, Christopher Batten, John Lazzaro, and John c Wawrzynek. Versions of this tutorial have been used in the following courses: CS250 VLSI Systems Design (2009) - University of California at Berkeley

Potrebbero piacerti anche

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Parasound HCA 1200Documento8 pagineParasound HCA 1200theaNessuna valutazione finora

- Layout LPDocumento6 pagineLayout LPAndrea BautistaNessuna valutazione finora

- TI Space Products GuideDocumento39 pagineTI Space Products GuideYze Shiuan YNessuna valutazione finora

- Irjet V7i3986Documento5 pagineIrjet V7i3986Vasu ThakurNessuna valutazione finora

- Measuring Laser Power and Energy OutputDocumento5 pagineMeasuring Laser Power and Energy OutputBilel KrayniNessuna valutazione finora

- Material Specifications Cell: Technical Specification OFDocumento8 pagineMaterial Specifications Cell: Technical Specification OFkajale.shrikantNessuna valutazione finora

- Hasee HP500 Laptop SchematicsDocumento41 pagineHasee HP500 Laptop SchematicsbrunnofranklinNessuna valutazione finora

- Features Description: Deep Sea Electronics Ats / Mains ControllerDocumento2 pagineFeatures Description: Deep Sea Electronics Ats / Mains Controllerabduallah muhammadNessuna valutazione finora

- Voice Over LTEDocumento19 pagineVoice Over LTEGabriele Spina100% (2)

- Introduction The Smart AlarmDocumento4 pagineIntroduction The Smart AlarmHafiz San0% (1)

- LT3743 Demo Board Rev2Documento6 pagineLT3743 Demo Board Rev2tosraj7001Nessuna valutazione finora

- An Introduction To Digital Signal Processing: Edmund M-K. LaiDocumento224 pagineAn Introduction To Digital Signal Processing: Edmund M-K. LaiSalam ArifNessuna valutazione finora

- Innodisk m5s0 Bgm2oavp-3317554Documento22 pagineInnodisk m5s0 Bgm2oavp-3317554ManunoghiNessuna valutazione finora

- CI Series Multi-Function Counter / Timer User Manual: FeaturesDocumento12 pagineCI Series Multi-Function Counter / Timer User Manual: FeaturesXavier Jesus0% (1)

- AlokDocumento5 pagineAlokAlok KumarNessuna valutazione finora

- SLD QMT 8djh R-R-T (15kv)Documento3 pagineSLD QMT 8djh R-R-T (15kv)Manuel MassidiNessuna valutazione finora

- 1 RADWIN 2000 C PTP SE1Documento85 pagine1 RADWIN 2000 C PTP SE1Vero DuranNessuna valutazione finora

- Arm7 FamilyDocumento4 pagineArm7 FamilydanielNessuna valutazione finora

- Dong, Roy - Application NoteDocumento7 pagineDong, Roy - Application Notepritam kalaimaniNessuna valutazione finora

- BSC Course ContentsDocumento4 pagineBSC Course ContentsAns MehmoodNessuna valutazione finora

- Datasheet PDFDocumento2 pagineDatasheet PDFAknova TsaniataNessuna valutazione finora

- 451.48 Win10 Win8 Win7 Release NotesDocumento42 pagine451.48 Win10 Win8 Win7 Release NotesIbond Muhammad MulyaNessuna valutazione finora

- METAMATERIALS:Engheta & Ziolkowski or Rahmat-Samii & Yang Text BookDocumento3 pagineMETAMATERIALS:Engheta & Ziolkowski or Rahmat-Samii & Yang Text BookbaburaokodavatiNessuna valutazione finora

- Yosef Final ThesisDocumento97 pagineYosef Final ThesisTsega TeklewoldNessuna valutazione finora

- ZVEX Fuzz Factory InstructionsDocumento1 paginaZVEX Fuzz Factory InstructionsMat DowerNessuna valutazione finora

- TV2KR SchematicDocumento3 pagineTV2KR SchematicFilipe SequeiraNessuna valutazione finora

- Electronic Parts Symbols Labeling and ApplicationDocumento23 pagineElectronic Parts Symbols Labeling and ApplicationRonald ConstantinoNessuna valutazione finora

- Amateur Radio Guide To DMR 2nd Edition 20190506Documento36 pagineAmateur Radio Guide To DMR 2nd Edition 20190506Jack RodriguezNessuna valutazione finora

- Mux 2700Documento16 pagineMux 2700obioji100% (1)

- Loru SBR Rakha KarDocumento9 pagineLoru SBR Rakha KarPython SolutionsNessuna valutazione finora