Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Assignment 1

Caricato da

Sumeyra TamaDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Assignment 1

Caricato da

Sumeyra TamaCopyright:

Formati disponibili

Summer 2011 CME 2006 - CPU Design Project

A CPU which is similar to Manos Basic Computer is to be designed, verified using Max Plus II or Quartus II software from Altera (Bonus (+10): implementation on the DE0 FPGA board). The project is given as four assignments. It is advised that you read problem definitions of all of them before actually starting with assignment-1, i.e., Common Bus and Registers. Please submit zipped All Files (dont forget to submit wave format of the results) of the simulations for all assignments. ASSIGNMENT I

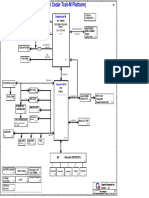

Common Bus System (Reference to Figure 5-4)

Memory 32x8

Code Segment (16x8) Address Range: : 0-15 Data Segment (8x8) Address Range: 16-23 Stack Segment (8x8) Address Range 24-31

s2 s0 s1

Bus

m 1m 0

ReadWrite PC (4-bits)

LD

INR

CLR

SP(3-bits) LD LD INR DCR AR(3-bits) INR CLR CLR

1 4 3 5 6

Clock

DR (4-bits) LD INR IR (8-bits) LD AC (4-bits) LD INR CLR CLR

4-bit common bus

Figure-1 Basic Computer Common-Bus System

Data[4 bits]

LD INR CLR DCR ReadWrite [m1m0 ] CLK

[r2 r1r0] [r2 r1r0] ] 2 r1r0] [r

Data[4 bits]

Common_Bus_System

S0

S1 S2

Figure-2 Block-Diagram of Common-Bus System, where r2r1r0 refers to register selection index, m1m0 refers to segment selection index

You are expected to implement the common bus architecture designed in Figure 1 in Altera and save it as a block diagram (symbol file) with the name, Common_Bus_System as shown in Figure 2. Finally test and simulate your implementation by loading (transferring) data from Program memory and Data memory to registers and applying INR and CLR operations on them. Details are listed below;

There is one memory unit consisting of Code Segment, Data Segment and Stack Segment. Unit selections are as follows

S2S1S0 000

m1m0 00 01 10

Register / Memory Segment

001 010 011 100 101 110

Code segment Data segment Stack segment SP PC DR AR IR AC

Each bus control inputs of the bus block diagram (figure-2) indicated by r2r1r0 are encoded same as unit selections. That is, LD [r2r1r0 = 1] indicates SP s LD input LD [r2r1r0 = 2] indicates PC s LD input

.

CLR [r2r1r0 = 1] indicates SP s CLR input CLR [r2r1r0 = 2] indicates PC s CLR input

.

INR [r2r1r0 = 1] indicates SP s INR input INR [r2r1r0 = 2] indicates PC s INR input

.

DCR applies only to SP. ReadWrite and m1m0 applies only to memory unit

Registers have 5 inputs which are data inputs, load input, clear input, clock input and increment input (additionally decrement in SP) Register sizes are given on the figure. IR has 8 data bits. So system bus must have 4 data bits. Memory is 32x8 bits consisting of Code Segment 16x8 bits with the address range [0-15], Data segment 8x8 bits with the address range [16-23] and Stack Segment 8x8 bits with the address range [24-31].. Memory unit must be initialized with pre loaded test image (memory.mif). The image file is also included in memory.zip file. When you open the gdf file, you have to configure memory component to load initial values from image file. This can be done by Edit Ports/Parameters command from Utilities menu or right click menu. You have to configure LPM_FILE parameter to point the initialization image file. ! Your project will be tested using this image file, so do not change it !

Potrebbero piacerti anche

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- STM32 F103 XXDocumento123 pagineSTM32 F103 XXporoi7Nessuna valutazione finora

- Lansoft Arlista 2015 03 23Documento6 pagineLansoft Arlista 2015 03 23proba947Nessuna valutazione finora

- ConfigDocumento3 pagineConfigLuis Angel Vos DomingoNessuna valutazione finora

- 3 02-Peripheral-DevicesDocumento7 pagine3 02-Peripheral-Devicesapi-298810403Nessuna valutazione finora

- DDI0243C Adk r3p0 TRMDocumento226 pagineDDI0243C Adk r3p0 TRMdraksunilNessuna valutazione finora

- Data Prepairation NOC IOH TEAM 2023Documento22 pagineData Prepairation NOC IOH TEAM 2023ukat hidayatNessuna valutazione finora

- Quanta Ze7 r1b SchematicsDocumento41 pagineQuanta Ze7 r1b SchematicsOleg DrozdovNessuna valutazione finora

- Pengenalan Komputer & Teknologi Maklumat Ch. 8Documento41 paginePengenalan Komputer & Teknologi Maklumat Ch. 8محمد شكري عبد الحليمNessuna valutazione finora

- Single 2-Input Nand Gate: PD CC oDocumento7 pagineSingle 2-Input Nand Gate: PD CC oStuxnetNessuna valutazione finora

- 2 Mbit SPI Serial Flash: FeaturesDocumento27 pagine2 Mbit SPI Serial Flash: FeaturesBrahimiNessuna valutazione finora

- Tcbook WeDocumento145 pagineTcbook Wedany weinfeldNessuna valutazione finora

- Design of Logic Circuits S3 SyllabusDocumento3 pagineDesign of Logic Circuits S3 Syllabussethu0% (1)

- Automatic Irrigation SystemDocumento3 pagineAutomatic Irrigation SystemVijay MNessuna valutazione finora

- Switches, Lights, and Multiplexers: UNIT4Documento49 pagineSwitches, Lights, and Multiplexers: UNIT4Trần Ngọc LâmNessuna valutazione finora

- Digital Circuits - Shift RegistersDocumento7 pagineDigital Circuits - Shift RegistersB.Prashant JhaNessuna valutazione finora

- Ug949 Vivado Design Methodology PDFDocumento306 pagineUg949 Vivado Design Methodology PDFIvan AlyaevNessuna valutazione finora

- Computer Organization and Architecture: Internal MemoryDocumento49 pagineComputer Organization and Architecture: Internal MemoryCông PhạmNessuna valutazione finora

- Flash Stock Rom No LG K5 - Ultimate GuideDocumento9 pagineFlash Stock Rom No LG K5 - Ultimate GuideCristóvão RodriguesNessuna valutazione finora

- 8086 Min Max Mode Operations ModifiedDocumento78 pagine8086 Min Max Mode Operations ModifiedRitu RathiNessuna valutazione finora

- ES FinalDocumento26 pagineES FinalBilal AhmedNessuna valutazione finora

- BC-2800 - Service Manual V1.1 PDFDocumento109 pagineBC-2800 - Service Manual V1.1 PDFMarcelo Ferreira CorgosinhoNessuna valutazione finora

- MP3 Player, How To Use The STA013 MP3 Decoder ChipDocumento13 pagineMP3 Player, How To Use The STA013 MP3 Decoder ChipMini Veiga AlbánNessuna valutazione finora

- I2C ProtocolDocumento17 pagineI2C ProtocolAditya BarveNessuna valutazione finora

- Dell Inspiron M102Z - Compal LA-7161P PLM00Documento43 pagineDell Inspiron M102Z - Compal LA-7161P PLM00Toni SetyawanNessuna valutazione finora

- Can We Build A Finite Automaton For Every Regular Expression?, - Build FA Based On The Definition of Regular ExpressionDocumento66 pagineCan We Build A Finite Automaton For Every Regular Expression?, - Build FA Based On The Definition of Regular ExpressiontariqravianNessuna valutazione finora

- TS6. Memory OrganizationDocumento5 pagineTS6. Memory Organization黄佩珺Nessuna valutazione finora

- Unit VI Parallel Programming ConceptsDocumento90 pagineUnit VI Parallel Programming ConceptsPrathameshNessuna valutazione finora

- University of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSDocumento3 pagineUniversity of Ghana: This Paper Contains Two Parts (PART I and PART II) Answer All Questions From Both PARTSPhilip Pearce-PearsonNessuna valutazione finora

- A/D Converter For Robots: Tilo GockelDocumento1 paginaA/D Converter For Robots: Tilo GockelAg Cristian100% (1)

- It8512e IteDocumento335 pagineIt8512e Itecsanchez_242623Nessuna valutazione finora