Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

16 AUV Motor Controller

Caricato da

Ghazal IraniDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

16 AUV Motor Controller

Caricato da

Ghazal IraniCopyright:

Formati disponibili

Kyle Graves, Carl Spurgers, Chase Johnson, Chris Drew, Patryk Smieciuszewki

kyle.graves@student.utdallas.edu, carl.spurgers@student.utdallas.edu, chase.johnson@student.utdallas.edu, christopher.drew@student.utdallas.edu, patch@utdallas.edu

Department of Electrical Engineering Erik Jonsson School of Engineering & Computer Science University of Texas at Dallas Richardson, Texas 75083-0688, U.S.A.

Project Goals:

System will provide propulsion control and monitoring aboard the UT Dallas Autonomous Underwater Vehicle. System will be controlled over USB and will interface with existing structures aboard the vehicle. System will enable rapid PWM switching of large currents. System design will accommodate 8 independent channels. This will be accomplished by designing a single logic board to control up to 4 dual-channel motor driver boards. Embedded software will possess the capability to perform self-test routines and self-diagnosis of error states. System will provide thrust feedback data to enhance position awareness. System will accommodate loads up to 12 amps per channel and will be easily adaptable for 28V to 50V operation depending on application.

Project Results:

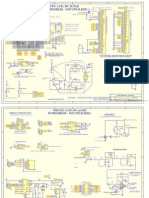

The logic board is assembled and functional. The high current board design has been proven experimentally as illustrated to the right. Design implements an H-bridge topology with IC FET drivers and optically isolated logic-level inputs. Hardware logic protects board from damage in case of incorrect inputs. High current board has been submitted to PCB manufacturer for milling. Thrust sense feedback implemented with Hall-effect current sensor. Software in development in conjunction with sonar team with the expectation of code sharing among systems.

High Current Board Prototype Under Test

Completed Logic Board

Project Overview:

Hardware

USB

Test Successful! Clean output at 28V, 10A 80% Duty Cycle 1KHz PWM

System Schematics

1 2 3 4 5 6 7

1 2 3 4 5 6 7 1 2 3 4 5 6 7

DP1

Vcc c

R4 .2

R3 .2

R2 .2

GND

R4 .1

R3 .1

R2 .1

R1 .1

U1 6

93C56

1 CS SK DI DO VCC NC ORG G ND 8 7 6 GND GND GND GND 5 GND AGND 47 TEST

BCBUS3 SI/WUB PWREN#

P1 .0 /ACL 1 K

8 4 8 5 8 6 GND GND

R4 1 7 5

R4 0 75

PWM frequency of 1 KHz

PWR

Reset

PRCSR

7-Seg Driver

7-Seg

E 1

3 4

41

P1 1 .1 CL K /M P1 1 .2 /SM CL K

L ED D2 R0 8 0 5 1 2 5 2 6 2 7 2 8 2 9 3 0 3 1 3 2

Du a N-CHFET l Q2 S1 G1 D2 D1 G2 S2 6 5 4

L ED D1 R0 8 5 0

45

9 18

C1 6 .1 u F R5 10 k

GND

25 34

P2 .0 / A 1 K/MCL K T CL

R6 2 .2 k G ND

GND

EEPROM

Title USB Conv ersion A uthor Chase Johnson, P atryck S miecuiszews ki Chr s Drew , i A UV 2009 F il e Document C:\Users\K yle Graves\Doc uments\Classes 2008\S pring 2009\A UV \2ND SE ME STE R TURN I \A UV _S 09_LOGI _V 1_3-3.dsn N C Rev ision Dat e S heets 1.0 2/ 24/09

7

Note s GND -For all nets the number co nventi on is as follo ws -The nu mb er afte r e ach ne t name tells wh at bo ard # and wha t H-Bri dge it b elo ngs to Exampl e:FWD_3 4 is o n board # 3, H-b ridge #4 If the re i s o nly a sin gle number then there i s o nly one o f these ne ts pe r bo ard

E

P2 .1 /TA1 .0 P2 .2 /TA1 .1 P2 .3 /TA1 .2 P2 .4 /RTCCL K

F WD_11 P WM_1 1 F WD_12 F WD_23 F WD_24 F WD_35 F WD_36 F WD_47

Red

2 3

Gree n

Title MSP 430F5419

E E

P2 .5 P2 .6 /ACL K P2 .7 / DC1 2 CL K/DMAE0 A

Title MSP 430F5419

GND

10

AT9 C5 6 3 EEP

EEDATA

28 27 26

3 .3 V

P5 .3 /XT2 UT O

9 0

5V

A uthor Chase Johnson, K yle Graves, Chris Drew AUV2009 File C:\ Users\ Kyle Graves\Docu ments\Cl s ses 2008\S pring 2009\A UV \2ND S EM ES TER TURN IN\AUV_S 09_LOGIC_V 1_3-3.dsn a Rev ision Date 1.0

1 2 3 4 5 6

Document S heets 4

1 2 3 4

A uthor Chase Johnson, K yle Graves, Chris Drew AUV 200 9 File C:\ Users\ Kyle Graves\Docu ments\Cl s ses 2008\S pring 2009\A UV \2ND S EM ES TER TURN IN\AUV_S 09_LOGIC_V 1_3-3.dsn a Rev ision Date 1.0

5 6

Document S heets 4

1 of 1

2/24/09

7

2/24/09

7

Minimized thermal dissipation facilitating use in sealed, submerged enclosures

H-Bridge 1 H-Bridge 2

2 V 8 28V R1 4 100 A G ND R1 5 100 G ND 2 x 1 L g i c Bu f e r 0 o U4 1 3 .3 V TH- 1 x3 1 1 GND 2 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 8 1 2 1 1 9 10 B TP1 1 1 11 GND 5 TP3 1 1 9 10 GND 5 V 6 7 3 TP1 0 4 4 5 1 2 2 x1 0 L o g c Bu ffe r i U6 2 20 19 18 17 16 15 14 13 8 12 GND 11 9 10 B B B 11 B GND GND G ND GND G ND G ND GND G ND C1 8 .4 u 7 GND 5V 6 7 C2 6 6 n 8 f R2 3 9 .9 K 0 3 5 TP3 4 0 4 GND 5 4 ININ+ 3 R2 4 47K 2 1 x1 1 C o n e to n c r B1 R1 8 10 0 GND R1 9 10 0 3 .3 V TH -1 x3 1 1 A A A Vmc u TL V2 7 1 3 U8 VCC OUT Vmc u TL V2 3 1 7 U1 0 VCC OUT GND Vm cu TL V2 3 7 1 U1 2 VCC OUT GND A 1 1 Co n e cto r x 1 n B3 C1 .4 7 u 15V R2 6 10k R2 7 1 k 0 C4 1 u 0 C5 1n A 2 V 8 1 V 5

OE 1 I0 I1 I2 I3 I4 I5 I6 I7 GND

V cc OE 2 O0 O1 O2 O3 O4 O5 O6 O7

OE1 I0 I1 I2 I3 I4 I5 I6 I7 GN D

V cc OE 2 O0 O1 O2 O3 O4 O5 O6 O7

Qu a d AND CD4 0 1 BME4 8 U4 GND 1 2 3 R3 1 90 K .9 R3 2 4 K 7

J3

J5

1 2

FWD_11 P WM_11 R V _11 E FWD_12 P WM_12 R V _12 E

TP1 0 1 TP1 0 2 TP1 0 3 TP1 0 8 TP1 0 9 TP1 1 0

2 3 4 5 6 7 8 9 10

C RNT_ SNS _11h P resence_ 1

FWD 5 _3 P WM_ 35 RE V_ 35 FWD 6 _3 P WM_ 36 RE V_ 36

TP3 0 1 TP3 0 2 TP3 0 3 TP3 0 8 TP3 0 9 TP3 1 0

2 3 4 5 6 7 8

CRNT_S NS_1 1m

1 2 3

CRNT_ SNS _23m

CRNT_ SNS _35m

1 2 3

Vd d

14 13 12

HS1 1 HS2 1

1 2

CRNT_S NS_3 5h Pre sence_3

2 x4 -FET Dri e r v M CP1 0 3 -E/ N 4 S U5 NC INA GND INB NC O UT A Vc c O UT B 8 7 6 5

G ND R9 10

GND

CRNT_ SNS _11h

IN-

IN+

C2 8 68nf

R2 7 90 K .9

R2 8 4 K 7

CRNT _S NS _23h

IN-

IN+

CRNT _S NS _35h

28V

28 V

4 5 6 7 Vss

11 10

LS 21

R1 0 10

3 4

C3 0 68nf

R4 10k

R5 10 k

LS 11

R1 1 1 k R1 2 1 k

9 8 GND

C1 9 .4 u 7 Vmc u TL V2 7 1 3 U9 VCC OUT GND 4 ININ+ Vmc u TL V2 3 1 7 U1 1 VCC OUT GND Vm cu TL V2 3 7 1 U1 3 VCC OUT GND TP1 R1 2K GND 4 Ph o to o u l e rCh i p c p PC8 4 XJ 0 0 0 F 7 0 U1 2 x7 He x I v e r n rte CD4 0 6 9 UBM U2 1 16 2 2 3 R2 5 9 .9 K 0 R2 6 47K 4 2 3 R2 9 90 K .9 R3 0 4 K 7 4 2 3 R3 3 90 K .9 R3 4 4 K 7 TP2 R2 2K 2 3 4 5 TP3 GND GND GND G ND GND G ND G ND GND G ND R3 499 6 7 8 15 3 14 4 13 5 12 11 10 G ND 9 GND R8 1k GND_ M Vm cu TL 3 7 1 V2 U1 4 VCC O UT G ND G ND 1 1 2 3 R3 5 9 0 .9 K R3 6 47K Q u d AND a CD4 0 8 1 BM E4 U3 Vd d 14 13 12 3 4 4 ININ+ 11 DO - 1 4 AC 2 10 2 2 5 6 9 Vss 8 C9 10 n G ND_ M 15 V 15 V Q1 DO-2 1 AC 4 G ND 2 .4 u 7 C3 5V C 28 V G ND 1 V 5 R7 10k R6 10k 6 7 9 10 4 5 6 11 GND 12 Vcc 14 13 28 V C2 .4 7 u 15V GND GND

C RNT_ SNS _12h

G ND

CRNT_S NS_3 6h

Power Connector

6 CKT Co n e cto r n H2

CRNT_S NS_1 2m

CRNT_ SNS _24m

CRNT_ SNS _36m

Digital Li ne Buffer

Header to H-Bridge

F WD _1

+1 -1

1 2 3

CRNT_ SNS _12h

IN-

IN+

CRNT _S NS _24h

IN-

IN+

CRNT _S NS _36h

REV _1

C2 7 6 n 8 f

C2 9 68nf

C3 1 68nf

+2

Vss 8 15V

PWM_1

C C C C C

H-Bridge

Q1 = ( FWD * RE V) + (F WD * ~RE V * P WM) Q2 = ( FWD * RE V) + (~ FWD * RE V * P WM)

-2

G ND

Current sense capability

D

R1 6 100 G ND

R1 7 100 G ND 2 x 1 L g i c Bu f e r 0 o U5 1

x 3 . V TH - 1 3 3 1 2 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 8 1 2 1 1 9 10 TP2 1 1 11 GND 5 V 6 7 3 TP2 0 4 4 5 2

1 x1 1 C o n e to n c r B2

R2 0 10 0 GND

R2 1 10 0 GND 2 x1 0 L o g c Bu ffe r i U7 1

3 .3 V

TH -1 x3 1 2

1 1 Co n e cto r x 1 n B4

GND TP5 PMO S 3 3 1 D5 D6 PMOS Q2 1 TP6 1

5 20 19 18 17 16 15 14 13 8 12 11 9 10 Vm cu GND 5V 6 7 3 TP4 4 0 4 2 J6

CRNT_S NS_47 m

O ptocouplers

CRNT_S NS_4 7h

OE 1 I0 I1 I2 I3 I4 I5 I6 I7 GND

V cc OE 2 O0 O1 O2 O3 O4 O5 O6 O7

OE1 I0 I1 I2 I3 I4 I5 I6 I7 GN D

V cc OE 2 O0 O1 O2 O3 O4 O5 O6 O7

J4

H 11 S

HS2 1

2 3 4

FWD_23 P WM_23 R V _23 E FWD_24 P WM_24 R V _24 E

TP2 0 1 TP2 0 2 TP2 0 3 TP2 0 8 TP2 0 9 TP2 1 0

2 3 4 5 6 7 8 9 10

C RNT_ SNS _23h P resence_ 2

FWD 7 _4 P WM_ 47 RE V_ 47 FWD 8 _4 P WM_ 48 RE V_ 48

TP4 0 1 TP4 0 2 TP4 0 3 TP4 0 8 TP4 0 9 TP4 1 0

2 3 4 5 6 7 8 9 10

CRNT_S NS_4 7h Pre sence_4

5 C3 2 68nf

2 x4 -Cu rre n Se n t se ACS7 1 2 2 0 x A U6 8 IP+ Vcc 7 IP+ VI UT O 6 IP- FIL TER 5 IPGND

C2 2 . 7u 4 G ND_ M

CR _SNS _1 NT

TP4 C1 0 10 u

GND

G ND

GND

1 x1 1 Co n n e to c r H1 1 2

-1

TP8

FWD_1 P WM _1 REV _1 CRNT_S NS_1 Pre sence

5 V 28V R1 3 100 C6 220 u 0

GND

TP7 D1 DO-2 1 AC 4

D3 DO-2 1 4 AC 1

C RNT_ SNS _24h

G ND

CRNT_S NS_4 8h

GND

TP4 1 1

11 5

TL 3 7 1 V2 U1 5 VCC O UT G ND

1 2

CRNT_S NS_48 m

3 4 5

15V Regulator

1 5 VREG M C7 8 5 BDTG 1 VREG 1 C7 .3 3 u G ND IN O UT 3 15V

D7 DO-2 1 AC 4

D8 DO-2 1 AC 4 NM OS Q4 3

LS 11

D2

1 NMO S Q3 3

LS21

D4 DO-2 1 4 AC

Isolation between logic systems and high power drive circuitry Hardware logic implemented to prevent device damage if corrupted commands are received over USB interface Small form-factor Software Write universal communication protocol for vehicle peripherals Self-diagnosis and built-in test capability Communicate error codes on 7 segment display Resolve and command precisely variable PWM for superb positioning resolution

IN-

IN+

3 R3 7 9 0 .9 K R3 8 47K

DO-2 1 AC 4

Current Sense

CRNT_S NS_4 8h

6 7

C3 3 68nf

G ND C8 1 u 0

G ND

Current Sense

Aut hor K yle Grav s, Chr s Drew e i A UV 2009 File C:\Users\K yle Grav Document s\Classes 200 8\Spring 2009\AUV \2ND S EME S TER TURN IN\ AUV_S 09_LOGIC_V 1_3-3.dsn es\ Revision Date 1. 0

1 2 3 4 5 6

GND

G ND

GND

Title Logic B uffer/Header to H-B ridge

E

Title Logi Buffer/Header to H-B ridge c A uthor Patryck Smieciuszewski AUV 200 9 File C:\ Users\ Kyle Graves\Docu ments\Cl s ses 2008\S pring 2009\A UV \2ND S EM ES TER TURN IN\AUV_S 09_LOGIC_V 1_3-3.dsn a Rev ision Date 1.0

1 2 3 4 5 6 E

8 9 10

FWD_2 P WM _2 REV _2

GND_ M

Q3 = ~ FWD * RE V * P WM

Q4 = F WD * ~REV * PWM

Title H-B ridge B oard - B ridge 1

E

Document S heets 4

Document S heets 5

GND 11

G ND

G ND

G ND

A ll T ran sistors Off = ~F WD * ~REV

CRNT_S NS_2

Aut hor G ND Carl S purgers, Chris Drew A UV File C:\Users\K yle Grav es\Documents\ Classes 2008\S pring 2009\ AUV\2ND SE ME STE R TURN IN\A UV _S 09_H_B RI GE_V 2.dsn D Revision Date 1. 0 3/26/08

7 5 6

Document S heets 1 of 1

2/24/09

7

2/24/09

7

(Single channel representation)

Motor 1

Motor 2

Project Conclusions/Outcomes:

Logic board and high current protoboard function satisfactorily. Software development and final hardware optimizations in progress. Project on track for completion by semester end. Projected vehicle maneuverability and speed substantially exceed past performance using COTs systems. System design expected to facilitate future upgrades and interoperability throughout vehicle more readily than if COTs solutions were adopted for the motor controller system. Continuing success at the AUVSI competition expected.

Voltage Scaling Operation Amplifiers for H-Sensor to MSP Input

Logic Board Connector

+1

EESK

BCBUS0 BCBUS1 BCBUS2

R1 .2

30 29

P5 . /XT2 IN 2

3 .3 V

3. V 3

8 9

Vcc c

EECS

Ca p C2 4 12pf

Ca p C2 5 12pf

DP1

48

C yst al r

Drive mixed loads of 12A @ 28V and 4A @ 48V on different channels, simultaneously

3.3V Regulator

5 V A L DO

M SP4 0 F5 1 9 3 4 U1 A

M SP4 0 F5 1 9 3 4 U1 D

SPI/UART/I2C

P3 .0 /UCB0 STE/UCA0 CL K 33 34 35 36 39 40 41 42 A A P3 .1 /UCB0 SIMO /UCB0 SDA

1 2 3

5 VAUX 5 VCC 3 .3 VO UT 3 .3 VAUX

NC G ND NC NC

8 7 6 3 .3 V

Pow er/Program

DVCC1 DVCC2 16 64 38 87

Vm cu

RE V_ 11 RE V_ 12 RE V_ 23 RE V_ 24 RE V_ 35 RE V_ 36 RE V_ 47

P t 3 or

M SP4 3 F5 4 9 0 1 U1 C 1 x3 He d e a r H1

Vm cu

P3 .2 /UCB0 SO MI/UCB0 SCL P3 .3 /UCB0 CL K/UCA0 STE P3 .4 /UCA0 TXD/UCA0 SIMO P3 . /UCA0 RXD/UCA0 5 SO MI

P ogr am i ng r m

46 3

42 14 31

FTDI Debug

Manual Override

4 F B1

5 GND

PM OS (Pi Co re cti o n ) n Q1 2 3

DVCC3 DVCC4

A DC Input

R er ence ef

AVCC AVSS P5 . /VREF+ / e REF+ 0 V P5 .1 / R EF V -/Ve REF 1 1 1 2 9 1 0 C3 4 10nF

.1 u F

1 u 0 F

C8 .1 u F C9 C0 8 5 0

C2

C3

F B2

C1 3 4 .7 u F

C1 4 .1 u F

P er ow

C1 7 C1 5 4 uF .7 .1 u F C1 8

V_ CORE

62 C1 9 .1 u f C2 0 .1 u f C2 1 . u 1 f C2 2 .1 u f

H1.1 H1.2

1 2 3 MSP4 3 0 4 1 F5 9 U1 B

P3 .6 /UCB1 STE/UCA1 CL K P3 .7 /UCB1 SIMO /UCB1 SDA

DVSS1

15 63 37 88 Vm cu

.1 u F G ND R3 9 1k G ND

P t 5 or

DVSS2 DVSS3 DVSS4

P5 .4 /UCB1 SO MI/UCB1 SCL GND P5 .5 /UCB1 CL K/UCA1 STE P5 .6 /UCA1 TXD/UCA1 SIMO P5 . /UCA1 RXD/UCA1 7 SO MI

51 52 53 54

USB1 Vc c B DD+ GND 1 2 3 4

1 2

1 x2 He a d e 1 x2 He a e r r d F1 F2 1 2

C1 .0 u 1 F GND GND R7 47K

.0 3 3 u F G ND C1 0

Timers ( TIC/ TO C)

P1 .0 / A 0 K/ACL K T CL P1 . /TA0 .0 1 17 18 19 B B 20 21 22 23 24 P6 .0 /A0 P6 .1 /A1

9 7 9 8 9 9 10 0 1 2 3 4

T herm _1 T herm _2 T herm _3 T herm _4 CRNT_S NS_1 1m

H1.1 H1.2

7 S eg. Manual Overri de

3 .3 V 1 2

7 Segment Display

Vmc u B 7 -Se g Dri ve r U2 GND 1 2 3 4 5 6 7

.0 1 u F

TEST/SBWTCK

91 Vmc u R8 47 k

GND

P t 1 or

P1 . /TA0 .1 2 P1 . /TA0 .2 3 P1 . /TA0 .3 4

P t 6 or

P6 .2 /A2 P6 .3 /A3 P6 .4 /A4 P6 .5 /A5 P6 .6 /A6 P6 .7 /A7

P9 .0 /UCB2 STE/UCA2 CL K P9 .1 /UCB2 SIMO /UCB2 SDA

68 69 70 71 72 73 74 75

Cl ck 7-S D o

1 x3 He d e r a H4

R1 27 GND

GND

PJ . /TDO 0 PJ .1 / DI/TCL K T PJ . /TM S 2 PJ.3 /TCK /RST/NMI/SBWTDIO

C4 47pF

92 93 94 95 96

1 3 5 7 9 11

TDO TDI TMS TCK GND RST NC

VCC To o l VC CTa rg t e NC TEST NC NC NC

2 4 6 8 Ca p C2 3 2 .2 n F

P t 9 or

R3 470

JTAG He a d e r H5

P1 . /TA0 .4 5 P1 .6 /SMCL K P1 .7

Pr esence_1 Pr esence_2 Pr esence_3 Pr esence_4

CRNT_S NS_1 2m CRNT_S NS_2 3m CRNT_S NS_2 4m

P9 .2 /UCB2 SO MI/UCB2 SCL P9 .3 /UCB2 CL K/UCA2 STE P9 .4 /UCA2 TXD/UCA2 SIMO

GND S IN S CL K LA T OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7

V CC IREF S OUT B lank OUT1 5 OUT1 4 OUT1 3 OUT1 2 OUT1 1 OUT1 0 OUT9 OUT8

24 23 22 21 20 19

R1 3 7 .5 k

FT DI

C7 C6 C5 47pF R2 27 .0 3 3 u F GND .1 u F AV CC VC C VC C VCCI A O VCCI B O TP 2

Data 7- SD Red Gr een

GND

Data 7 -SD Clock 7 -S D Latch 7- SD

TP1

P7 . /TBOUTH/SVM OUT 2 10 12 14 P4 .0 /TB0 P4 .1 /TB1 43 44 45 46 47 48 49 50

5 5 5 6 5 6 7 8

P9 . /UCA2 RXD/UCA2 5 SO MI P9 .6

P W M_12

P t 7 or

P7 .3 /TA1 .2 P7 /A1 2 .4 P7 /A1 3 .5 P7 /A1 4 .6 P7 /A1 5 .7

P t 4 or

G ND 6 GND 8 7

3 OUT V3 USBDM USBDP

P t 10 or

FT2 3 2 D 2 FTDI

ADBUS0 ADBUS1 ADBUS2 ADBUS3 ADBUS4 ADBUS5 ADBUS6 ADBUS7 ACBUS0

24 23 22 21 20 19 17 16 15 13 12 11 10

1 3 5

TH - 2 3 x J1

2 4 6

MRX MTX

Vmc u 3 .3 V 1 x3 He a d r e H3 1 x3 He a d e r H2 1 2 3 G ND

13

P WM _23 P WM _24 P WM _35 P WM _36 P WM _47 P WM _48 RE V _48

C C

CRNT_S NS_3 5m CRNT_S NS_3 6m CRNT_S NS_4 7m CRNT_S NS_4 8m

P9 .7

P4 .2 /TB2 P4 .3 /TB3 P4 .4 /TB4 P4 .5 /TB5 P4 .6 /TB6 P4 .7 /TBCL K/SM CL K

GND 18 17 16 15 14 13 C

GND

P1 .0 /UCB3 0 STE/UCA3 CL K P1 0 .1 /UCB3 SIM O/UCB3 SDA P1 .2 /UCB3 0 SO MI/UCB3 SCL P1 .3 /UCB3 K/UCA3 STE 0 CL P1 .4 /UCA3 0 TXD/UCA3 SIMO P1 0 .5 /UCA3 RXD/UCA3 SOM I

76 77

8 9

78 10 79 80 81 82 83

RST IN#F

R T IN M S #

1 2 3

RS TIN#M M TX M RX

11 12

R4 1 .5 K 5 GND RSTOUT# RESET#

3 .3 V

P8 . /TA0 .0 0

57 58 59 60

P1 .6 0 P1 .7 0

RST IN#F

C1 1 47pF X1 6 MHz C1 2 47pF

SI/WUA

20

19

18

17

16

15

14

13

12

P8 . /TA0 .4 4 P8 . /TA1 .0 5

61 65 66 67 M SP4 3 F5 4 9 0 1 U1 E

43

XTI N

BDBUS0 BDBUS1 BDBUS2 BDBUS3 BDBUS4 BDBUS5 BDBUS6 BDBUS7

44

38 37 36 35 33 32

Ther m_1 Ther m_2 Ther m_3 Ther m_4

4 Re s. Ne t. 5 6 7 8

Vcc a

Vcc a

40 39

XTOUT

3 5 7

4 6 8

P8 . /TA1 .1 6 P8 .7

La tch 7-S D

Cl ock s

P7 .0 /XIN P7 . /XOUT 1 1 3 1 4 Crysta l X2

Status LED

7 -Se g Di sp l a y U3

TH -2 x 4 J2

11

Thermistor Header

Vm cu

P t 8 or

ACBUS1 ACBUS2 ACBUS3

Progr amming Header

P8 . /TA0 .1 1 P8 . /TA0 .2 2 P8 . /TA0 .3 3

FTDI Connection

5V

TP PM 0303

F W D_4 8

Potrebbero piacerti anche

- Electronic Circuit Design Ideas: Edn Series for Design EngineersDa EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersValutazione: 5 su 5 stelle5/5 (2)

- Clevo C5500 C5500Q - 6-7P-C5505-002 PDFDocumento0 pagineClevo C5500 C5500Q - 6-7P-C5505-002 PDFfclodoaldoNessuna valutazione finora

- 110 Semiconductor Projects for the Home ConstructorDa Everand110 Semiconductor Projects for the Home ConstructorValutazione: 4 su 5 stelle4/5 (1)

- Sony Vaio Mbx-126 - Quanta Je5.1Documento36 pagineSony Vaio Mbx-126 - Quanta Je5.1nunoq171Nessuna valutazione finora

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsDa EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsValutazione: 1 su 5 stelle1/5 (1)

- TRK MPC5604B Rev B Schematic LayoutDocumento17 pagineTRK MPC5604B Rev B Schematic LayouthorsecraiovaNessuna valutazione finora

- Benq VL2040A 4H.28T01.S02Documento5 pagineBenq VL2040A 4H.28T01.S02pasmanteriabellaNessuna valutazione finora

- Sony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICDocumento36 pagineSony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICvideoson0% (1)

- MPC3500 - MPC4500 PP - v00 PDFDocumento18 pagineMPC3500 - MPC4500 PP - v00 PDFvladimir2426Nessuna valutazione finora

- Covr Lcd1: PIIC208 PIIC204 PIIC208Documento3 pagineCovr Lcd1: PIIC208 PIIC204 PIIC208Nguyễn Văn HinhNessuna valutazione finora

- Adaptive Systems in Control and Signal Processing 1992: Selected Papers from the 4th IFAC Symposium Grenoble, France, 1 - 3 July 1992Da EverandAdaptive Systems in Control and Signal Processing 1992: Selected Papers from the 4th IFAC Symposium Grenoble, France, 1 - 3 July 1992Nessuna valutazione finora

- BK BambooDocumento1 paginaBK BambooAT_No1Nessuna valutazione finora

- Itautec A7520 - 6-71-W2400-D03 GPDocumento45 pagineItautec A7520 - 6-71-W2400-D03 GPAlex Morais67% (9)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- Gc150ata 01Documento5 pagineGc150ata 01ValdairVelozoSoaresNessuna valutazione finora

- HT1621 PDFDocumento20 pagineHT1621 PDFJose Luis Mata LedesmaNessuna valutazione finora

- Schematic1 - Page1Documento1 paginaSchematic1 - Page1VânSơn100% (2)

- DOP7Documento2 pagineDOP7Nghia Do100% (1)

- Tecv1 01Documento1 paginaTecv1 01Ana Claudia BarbosaNessuna valutazione finora

- W375 L3 V1.2 SchemDocumento3 pagineW375 L3 V1.2 SchemAdrian PeterNessuna valutazione finora

- Ak1 MB 1213aDocumento30 pagineAk1 MB 1213aAshok JangraNessuna valutazione finora

- So Do Ket Noi 89c51 - Mt8880Documento2 pagineSo Do Ket Noi 89c51 - Mt8880Thắng HoàngNessuna valutazione finora

- Car Monitoring System Team IPA: Kirill Belyayev Amjad Chaudhry Arush Dhawan Aditya Kaundinya Bilal YousufiDocumento42 pagineCar Monitoring System Team IPA: Kirill Belyayev Amjad Chaudhry Arush Dhawan Aditya Kaundinya Bilal YousufiSaleh AlsaqerNessuna valutazione finora

- Wireles S Home Security System: R.N. Modi Engineering College, KotaDocumento17 pagineWireles S Home Security System: R.N. Modi Engineering College, KotaUtkarsh BhaskarNessuna valutazione finora

- Service Manual: 14" CTV-37V10, 37V20, 37X10 21" CTV-55V10, 55S10, 55X10, 55Z10Documento11 pagineService Manual: 14" CTV-37V10, 37V20, 37X10 21" CTV-55V10, 55S10, 55X10, 55Z10NeutrinosoNessuna valutazione finora

- PIC18 Eather 03 PDFDocumento1 paginaPIC18 Eather 03 PDFMarvinQuirozNessuna valutazione finora

- ML-1200 Repair ManualDocumento26 pagineML-1200 Repair ManualGreg Burkhart0% (1)

- With PLL DCG-105: Exploded ViewDocumento11 pagineWith PLL DCG-105: Exploded ViewpasantitoNessuna valutazione finora

- Conector Tipo B: Rxleda# TCK TDI TDO TMS NTRST RTCK RST DBGRQ Dbgack Acbus1Documento2 pagineConector Tipo B: Rxleda# TCK TDI TDO TMS NTRST RTCK RST DBGRQ Dbgack Acbus1juenkkinNessuna valutazione finora

- Schematic DiagramDocumento13 pagineSchematic DiagramSas WajiNessuna valutazione finora

- Io Controller1v0 Dcsupply Sch1r3.DsnDocumento12 pagineIo Controller1v0 Dcsupply Sch1r3.DsnEdwin McconnellNessuna valutazione finora

- Cpu Logic DiagramDocumento0 pagineCpu Logic DiagramMauricio RaúlNessuna valutazione finora

- Solar Panel Inverter Schematic V2.3Documento6 pagineSolar Panel Inverter Schematic V2.3Amanda PalmgrenNessuna valutazione finora

- Main Power Supply 12 Volt DC Relays: AC Volts AC VoltsDocumento1 paginaMain Power Supply 12 Volt DC Relays: AC Volts AC VoltsNaeemLatifNessuna valutazione finora

- 6Q7 9Q8 1 1 Q9 1 2 Q 5 - 9 1Gnd 2Trg 3out 4Rst5Ctl 6Thr 7dis 8VccDocumento4 pagine6Q7 9Q8 1 1 Q9 1 2 Q 5 - 9 1Gnd 2Trg 3out 4Rst5Ctl 6Thr 7dis 8VccAlexon DomingoNessuna valutazione finora

- SIM808 UNO SchematicDocumento1 paginaSIM808 UNO Schematicdark hiramekiNessuna valutazione finora

- Steval Mki062v2 SchematicDocumento2 pagineSteval Mki062v2 Schematicd280299Nessuna valutazione finora

- TM 7043Documento13 pagineTM 7043Radek KurekNessuna valutazione finora

- Can Bus SCHDocumento1 paginaCan Bus SCHhoangdai100% (3)

- Top-Level Diagram: SHEET 13-18Documento21 pagineTop-Level Diagram: SHEET 13-18Aref MGHNessuna valutazione finora

- MakerBot MightyBoard REVE SchematicDocumento1 paginaMakerBot MightyBoard REVE SchematicblablablouNessuna valutazione finora

- Hws 13642Documento3 pagineHws 13642dhieward100% (2)

- RAM Mapping 32 8 LCD Controller For I/O MC: FeaturesDocumento17 pagineRAM Mapping 32 8 LCD Controller For I/O MC: FeaturesfarhanNessuna valutazione finora

- Frequency Counter PDFDocumento1 paginaFrequency Counter PDFJunaid IqbalNessuna valutazione finora

- SAP-1 Simple As Possible Microprocessor - Original DesignDocumento1 paginaSAP-1 Simple As Possible Microprocessor - Original DesignFarhan S. Adul100% (1)

- China TV Chassis 3Y11Documento29 pagineChina TV Chassis 3Y11dl1476Nessuna valutazione finora

- Over Load Protection For TransformerDocumento45 pagineOver Load Protection For Transformerupender_kalwaNessuna valutazione finora

- MMB0 RevC SchematicDocumento1 paginaMMB0 RevC SchematicbiotekyNessuna valutazione finora

- PE4H VER24 SchematicDocumento2 paginePE4H VER24 SchematicB Huerta MuñozNessuna valutazione finora

- Philips Dvp-3010 SCHDocumento17 paginePhilips Dvp-3010 SCHnike03Nessuna valutazione finora

- F-Series (Single Alt.) : Engine Mounted ComponentsDocumento2 pagineF-Series (Single Alt.) : Engine Mounted ComponentsGracie Allen0% (1)

- Schematic MSP430G2553 DEV V1rev 4Documento1 paginaSchematic MSP430G2553 DEV V1rev 4Ky PhanNessuna valutazione finora

- Reflow Toaster v2 SchematicDocumento1 paginaReflow Toaster v2 SchematicBest PC BoxNessuna valutazione finora

- GT S5360Documento51 pagineGT S5360radiobrunoNessuna valutazione finora

- Antenna Training System PDFDocumento2 pagineAntenna Training System PDFMerlin Gilbert Raj0% (1)

- Yamaha DVD-S1200 - Service ManualDocumento84 pagineYamaha DVD-S1200 - Service ManualcristakeNessuna valutazione finora

- Computer Architecture...Documento8 pagineComputer Architecture...abdul.mannan.bcs.24Nessuna valutazione finora

- Woodward L Series Application NoteDocumento17 pagineWoodward L Series Application NoteDave WallaceNessuna valutazione finora

- Loudspeakers in Vented Boxes: Part L: A. N. ThieleDocumento11 pagineLoudspeakers in Vented Boxes: Part L: A. N. Thieledonald141Nessuna valutazione finora

- Thông Số Cài Đặt VFD CTK3Documento84 pagineThông Số Cài Đặt VFD CTK3Nguyen Hai DangNessuna valutazione finora

- 2008-ELT-Fully-differential Self-Biased Bio-Potential AmplifierDocumento3 pagine2008-ELT-Fully-differential Self-Biased Bio-Potential AmplifierLuật TrầnNessuna valutazione finora

- 2005 RD 1 Questions tcm18-190744Documento12 pagine2005 RD 1 Questions tcm18-190744DeepMukherjeeNessuna valutazione finora

- Chapter14. Wave PropagationDocumento44 pagineChapter14. Wave PropagationKianJohnCentenoTuricoNessuna valutazione finora

- KBC Quiz: Bachelor of Technology in Computer Science & EngineeringDocumento7 pagineKBC Quiz: Bachelor of Technology in Computer Science & EngineeringParveen JaatNessuna valutazione finora

- Electrical Systems Simulation LAB MANUAL 2019-2020Documento25 pagineElectrical Systems Simulation LAB MANUAL 2019-2020Vinay Kumar50% (2)

- Cenik FocusDocumento14 pagineCenik Focusalegru usNessuna valutazione finora

- Module Code and Title: Programme: Credit: Module Tutor: General ObjectivesDocumento5 pagineModule Code and Title: Programme: Credit: Module Tutor: General ObjectivesAmrith SubidiNessuna valutazione finora

- HANDBOOKDocumento31 pagineHANDBOOKCineide FerreiraNessuna valutazione finora

- Plus Elite Cabin Regatta: User and Installation Guide Manuel D'emploi Et D'installationDocumento85 paginePlus Elite Cabin Regatta: User and Installation Guide Manuel D'emploi Et D'installationmansoorNessuna valutazione finora

- Classification of ComputersDocumento5 pagineClassification of Computerspolaris1543Nessuna valutazione finora

- CET Power - AGIL Tri-Mono Datasheet v1.3Documento2 pagineCET Power - AGIL Tri-Mono Datasheet v1.3jokotsNessuna valutazione finora

- Brake Switch B HighDocumento2 pagineBrake Switch B HighDannyDDannyDNessuna valutazione finora

- Epoch 1000i FeaturesDocumento15 pagineEpoch 1000i FeaturesRamakrishnan AmbiSubbiahNessuna valutazione finora

- Z TT Plus ManualDocumento44 pagineZ TT Plus ManualHerbert Frota CuradoNessuna valutazione finora

- Emu4 Modbus MapaDocumento81 pagineEmu4 Modbus MapaAlberto Suazo BasaezNessuna valutazione finora

- ZCAR-1600A Six Phase Protective Relay Tester IntroductionDocumento4 pagineZCAR-1600A Six Phase Protective Relay Tester IntroductionMagidiel AraujoNessuna valutazione finora

- Wbjee PhysicsDocumento2 pagineWbjee PhysicsPinaki BiswasNessuna valutazione finora

- Syron v.2008-2009 PDFDocumento26 pagineSyron v.2008-2009 PDFAsep Arus100% (1)

- Murata Power Supply Noise Suppression & Decoupling For Digital ICs Application ManualDocumento85 pagineMurata Power Supply Noise Suppression & Decoupling For Digital ICs Application Manualkn65238859Nessuna valutazione finora

- Kuka YouBot Technical Specs PDFDocumento4 pagineKuka YouBot Technical Specs PDFWilliam GuarientiNessuna valutazione finora

- IM ch04Documento8 pagineIM ch04Edbert CatapangNessuna valutazione finora

- Gold and Nanotechnology in The Age of InnovationDocumento24 pagineGold and Nanotechnology in The Age of InnovationGoldGenie AsiaNessuna valutazione finora

- Direct Methanol Fuel Cell Systems For Portable Applications (Samsung)Documento21 pagineDirect Methanol Fuel Cell Systems For Portable Applications (Samsung)Dimitrios TsiplakidesNessuna valutazione finora

- Manoj Updated CVDocumento5 pagineManoj Updated CVArun TiwariNessuna valutazione finora