Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Biasing Using A Current Source

Caricato da

ilg1Descrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Biasing Using A Current Source

Caricato da

ilg1Copyright:

Formati disponibili

Current Source Biasing

Integrated circuits have transistors which are manufactured

simultaneously with the same device parameters (parameters from chip

to chip will vary)

As a result, different bias techniques are employed than in discrete

designs

One common technique is current source biasing, which allows the

designer to take advantage of matched devices

We will begin by looking at some simple current source circuits

A current source is not a naturally occurring device. It can be

simulated by a network of transistors and circuit elements.

The voltage across R

E

is approximately constant.

I

E

is held at a constant value

I

V V

R

E

EE BE

E

Problem: For the previous circuits find the bias

values I

C

and V

CE

for each transistor

Solution

Assume D

1

and D

2

forward biases (I

1

> I

B2

)

V V V

V V I R

V V

I

V

R

I I

I I

B EE F

F BE E

BE F

E

F

C E

C C

+ +

+

2 10 2 0 7 8 6

0 7

180

37

39

2 2 2

2

2

2

1 2

V V) V

Using KVL around loop A

2

Since

V

mA

Since

mA

( . .

.

.

.

Check that D

1

and D

2

are forward biased for a worst

case minimum

F

= 20

I

I

I

V V

R

V V I R

V V V

V V V

V V V

V V V

B

C

F

CC B

C CC C C

E B BE

E C BE

CE C E

CE C E

2

2

1

1

1 1

2 2

1 2 1

1 1 1

2 2 2

019

10 8 6

50

037

10 39 61

8 6 0 7 93

0 0 7

61 0 7 68

0 7 93 8 6

.

( . )

.

( . ) .

. . .

.

. ( . .

. ( . .

mA

V V

k

mA

V mA)(1k V

V V V

V V

V V) V

V V) V

Current Mirrors

Current mirrors also take advantage of matched transistors but require

a minimal number of resistors. They are also well suited for circuits

with more than one stage.

Basic BJT Current Mirror

I

V V V

R

V V V

R

I I I I

I I I I

I I

A

CC CE EE

A

CC BE EE

A

A REF B B

B REF B REF

REF A

+ +

<< <<

( )

1 1

1 2

1 2

IF is large

F

Problem

For the following circuit I

C3

= 3 mA and

V

CE

= 5.4 V. Find the quiescent (DC bias)

power dissipated in each transistor.

I I I I

I

V V

R

R

V V

I

V V V

V V

R

C o REF A

A

F EE

A

A

F EE

REF

E CE C

CC C

C

3

0

0 7 10

31

0 7 54 4 7

10 4 7 53

53

3

18

V

V V)

3mA

k

V; To achieve V V

V V V

V

mA

k

( )

. (

.

. . , .

. .

.

.

The DC power in each transistor is given by:

P I V I V I V

P

P

P

Q C CE B BE C CE

Q

Q

Q

+

1

2

3

3 0 7 0 2

3 0 7 10 28

3 16

( ( . .

( . (

(

mA) V) mW

mA)[ V V)] mW

mA)(5.4V) mW

MOSFET Current Mirror

Advantage: I

REF

= I

A

Gate current is negligible

Widlar Current Source

The basic current mirror requires that the bias current and reference

current be equal

The wildar current source sets the mirrored current to a value smaller

than I

REF

by using an extra resistor

The widlar current source allows you to establish small bias currents

(A) without using large resistor values

I

V V V

R

V V I R

I I e I e

V V

I

I

V

I

I

V

I

I

I R

I R V

I

I

REF

CC EE BE

A

BE BE E

E EO

V

V

EO

V

V

BE T

E

EO

T

E

EO

T

E

EO

E

E T

E

E

BE

T

BE

T

+

|

.

`

,

1

1 2 2 2

1 1

2 2

2 2

1

2

1

ln

ln ln

ln

Assuming matched BJTs

I I I I

I

V

R

I

I

E REF E o

o

T REF

o

1 2

2

ln

Equation difficult to solve in closed form. Use

successive iteration or trial and error

When you know the desired I

o

then I

REF

can be

found directly

I I

I R

V

REF o

o

T

|

.

`

,

exp

2

Problem:

Using a widlar current source find the values of

R

A

and R

B

that will produce I

o

= 100

A. Given

V

CC

= 10 V, VEE = -10 V, V

F

= 0.7 V and

= 1.

Solution:

Select a value of R

2

such that

I R V

o T 2

To keep exponent from becoming too large

V

I R R

I

I

V V V

R

R

T

o

REF

REF

CC EE F

A

A

]

]

]

25

100 1

100

100

0 025

546

10 10 0 7

354

2 2

mV

Choose mV k

A

A)(1k

V

mA

V V) V

5.46mA

k

( ) exp

( )

.

.

( .

.

Wilson Current Source

Refined Widlar source that can produce I

O

> I

REF

The balance between V

BE1

and V

BE2

is set by the

ratio of R

1

to R

2

Assuming

Assuming matched devices

I I

V I R V I R

V

I

I

I R V

I

I

I R

I

V

R

I

I

I

R

R

C E

BE REF BE o

T

REF

EO

REF T

o

EO

o

o

T REF

o

REF

+ +

+ +

+

1 1 2 2

1

1

2

2

2

1

2

ln ln

ln

Small Signal Modeling of Three Terminal Devices

Incremental signals

Piecewise linear models

Incremental circuit models

BJT

FET

Refinements to incremental model

Output resistance

Input resistance

Alternative BJT representation

Two - port representations

Small Signal Modeling of Three Terminal Devices

Related to PWL concept in which the V-I characteristics are modeled

by a straight line tangent to the curve at a particular operating point

With three terminal devices the relationship between the output port

and input port must be taken into account. This generally leads to a

PWL model with a linearly dependent source.

Circuits containing small signal models can be analyzed using linear

circuit theory under proper conditions

The terms small-signal and incremental will be used interchangeably

Incremental Signals

Any transient, periodic or AC fluctuation in a voltage or current

An incremental signal is small in magnitude compared to the bias

voltages or currents in the circuit

Incremental signal carries the signal information processed by the

circuit

PWL Models of Three Terminal Devices

Formation of small signal model begins with PWL model

PWL model can be applied to three terminal device if the dependency

of the output port is considered

r

v

i

V

I

BE

be

b

V I

T

B

BE B

,

Model valid only in constant current region

If the circuit in which the BJT is connected

produces a signal as well as a bias component to i

B

then:

i t i t

c b

( ) ( )

where i

c

and i

b

are inc

remental signals and

is the incremental current

gain

Since

F

is fairly constant it is possible to assume

=

F

in many

cases

The symbols h

FE

and h

fe

are sometimes used instead of

F

and

when

using h-parameter analysis

Incremental Circuit Model

In analyzing the small signal performance of a

circuit it is customary to ignore the DC components

of the model once the bias conditions have been

established.

This can be accomplished by the following

procedure:

1. Find the DC bias point and determine an

appropriate PWL model

2. Set all bias values to zero by setting all DC sources

to zero (including those in the PWL model)

3. Solve the desired variables using linear circuit

theory

4. Superimpose the signal variables onto the

corresponding DC bias voltages and currents to

obtain the total voltage and current values

I

V V

R

I I

V V V I R

B

BB F

B

C F B

OUT CE CC C C

1 0 7

10

30

100 30 3

10 3 7

V V

k

A

A mA

V mA)(1k V

.

( )( )

( )

Transistor operates in constant current therefore we

can use PWL model developed earlier

r

V

I

be

T

B

1 0 025

30

833

( . )

A

i

v

R r

v i R

v

R

R r

v v v

R

R r

V V v t v t

b

s

B be

o b C

o

C

B be

s s s

C

B be

OUT CE o s

+

+

+

+

+

100 1

10 0833

9 2

7 9 2

( )

.

.

( ) . ( )

k

k k

is the incremental or small - signal voltage gain

V

Total Bias Incremental

Voltage Voltage Signal

Problem:

For the following circuit find the incremental components of v

c

and v

e

.

Note: v

s

connection does not represent typical

amplifier design.

KVL around the input loop for incremental signal

( )

v

R

R R

i R R i r i R

i

v

R

R R

R R r R

v i R

R

R

R R

v

R R r R

v i R

R

R

R R

v

R R r R

s b b b E

b

s

E

e b E

E s

E

c b C

C s

E

1

1 2

1 2

1

1 2

1 2

1

1 2

1 2

1

1 2

1 2

1

1

1

1

1

1

+

+ + +

]

]

]

+ + +

+

+

+

]

]

]

+ + +

+

]

]

]

+ + +

( ) ( )

( )

( ) ( )

( )

( )

( ) ( )

( )

( )

( ) ( )

In the limit R R R

r R

v

R

R R

v

v

R

R

R

R R

v

E

E

e s

c

C

E

s

1 2

1

1 2

1

1 2

1

1

1

<< +

+

<< +

+

+

( )

( )

Incremental Model of MOSFET

[ ]

g

i

v v

k V V k V V

V V

I

k

g k I

m

D

GS

V I

GS

GS TR

V I

GS TR

GS TR

D

m D

GS D

GS D

|

.

`

,

,

,

/

( ) ( )

2

1 2

2

2

Assume constant current operation

Similar expression can be derived for JFET

An incremental description for a FET can also be defined for triode

(resistive) region

It can be shown that the incremental model is as follows

( )

r

k V V

g k V

ds

GS TR

m DS

1

2

2

Problem:

(A) Find the small signal componont of V

OUT

for the

following circuitd v

s

= 0.1 Sin

t, k = 0.2 mA/V

2

,

V

TR

= -2 V.

(B) Find the Thevenin circuit between V

OUT

and ground

..

The bias values can be found to be

mA V I V I R

D GS D E

0 47 0 47 . .

Applying KVL to output loop

V V I R R

DS DD D D E

+ ( ) ( . . 10 0 47 8 6 V mA)(3k) V

Since V

DS

> (V

GS

V

TR

) = 1.53 V the device

operates in the constant current region

The incremental transconductance g

m

is given by

[ ]

g k V V

m GS TR

2

2 0 2 0 47 2

0 61

2

( )

( . ) . (

.

mA / V V V)

mA / V

The signal component of v

OUT

can be found by substituting the PWL

model and setting all DC sources to zero

Applying KVL to the output loop

Note feedback limits the fraction of v that appears

as v

mA / V)(2 k

1+ (0.61mA / V)(1k

t) = t

s

gs

v v i R v g v R

v

v

g R

v i R g v R

v

g R

g R

v

a

v

v

g R

g R

v a v

gs s d E s m gs E

gs

s

m E

OUT d D m gs D

OUT

m D

m E

s

V

OUT

s

m D

m E

OUT V s

+

+

( )

( . )

)

.

( . )( . sin . sin

1

1

1

0 61

0 76

0 76 01 0 076

Since v

OUT

is computed with no load it represents the incremental open

circuit Thevenin voltage

The incremental r

th

can be found by setting v

s

to zero and applying

v

TEST

v g v R

i

v

R

r

v

i

R

gs m gs E

test

test

D

th

test

test

D

can only be satisfied if v

gs

0

Potrebbero piacerti anche

- Bayesian Inference 4 LMS PDFDocumento91 pagineBayesian Inference 4 LMS PDFilg1Nessuna valutazione finora

- SolarPowerRemoteMonitoringand ControllingUsingArduino, LabVIEWandWeb BrowserDocumento4 pagineSolarPowerRemoteMonitoringand ControllingUsingArduino, LabVIEWandWeb Browserilg1Nessuna valutazione finora

- Smart Plug Prototype For Monitoring Electrical Appliances in Home Energy Management SystemDocumento5 pagineSmart Plug Prototype For Monitoring Electrical Appliances in Home Energy Management Systemilg1Nessuna valutazione finora

- Home Automation Using Internet of Things PDFDocumento6 pagineHome Automation Using Internet of Things PDFilg1Nessuna valutazione finora

- The Research of Automatic Sunlight CollectingDocumento3 pagineThe Research of Automatic Sunlight Collectingilg1Nessuna valutazione finora

- Linear AbridgedDocumento145 pagineLinear AbridgedFrancisco BenítezNessuna valutazione finora

- Detecting Integrity Attacks On Scada Systems 2014 PDFDocumento12 pagineDetecting Integrity Attacks On Scada Systems 2014 PDFilg1Nessuna valutazione finora

- Constantly Functioning Adruino Based Solar TrackerDocumento6 pagineConstantly Functioning Adruino Based Solar Trackerilg1Nessuna valutazione finora

- RLDocumento37 pagineRLilg1Nessuna valutazione finora

- 06820253Documento4 pagine06820253ilg1Nessuna valutazione finora

- Towards Energy-Autonomous Wake-Up Receiver Using VLCDocumento6 pagineTowards Energy-Autonomous Wake-Up Receiver Using VLCilg1Nessuna valutazione finora

- Framework Forecasting Self-Organizing: Quality Models UsingDocumento6 pagineFramework Forecasting Self-Organizing: Quality Models Usingilg1Nessuna valutazione finora

- Ronan Et Al. - 2007 - A Reconfigurable Processor for the Cryptographic η T Pairing in Characteristic 3-AnnotatedDocumento6 pagineRonan Et Al. - 2007 - A Reconfigurable Processor for the Cryptographic η T Pairing in Characteristic 3-Annotatedilg1Nessuna valutazione finora

- Abstract - Smart ATM Access & Security System Using Face Recognition & GSM TechnologyDocumento1 paginaAbstract - Smart ATM Access & Security System Using Face Recognition & GSM Technologyilg1Nessuna valutazione finora

- Free Range VHDLDocumento151 pagineFree Range VHDLpickup666Nessuna valutazione finora

- Elliptic NotesDocumento74 pagineElliptic Notesalin444444Nessuna valutazione finora

- 8Documento20 pagine8Amit Kumar JainNessuna valutazione finora

- Coordination of Suck-Swallow and Swallow Respiration in Preterm InfantsDocumento8 pagineCoordination of Suck-Swallow and Swallow Respiration in Preterm Infantsilg1Nessuna valutazione finora

- Wyoming Elliptic CurveDocumento104 pagineWyoming Elliptic CurveSalman HabibNessuna valutazione finora

- An Effective Means of Transmission Line Protegtion byDocumento22 pagineAn Effective Means of Transmission Line Protegtion byilg1Nessuna valutazione finora

- OpenCV On BBBDocumento4 pagineOpenCV On BBBilg1Nessuna valutazione finora

- Object Counting and Density Calculation Using MatlabDocumento46 pagineObject Counting and Density Calculation Using Matlabilg1Nessuna valutazione finora

- CAD Tool Autogeneration of VHDL FFT For FPGA ASIC Implementation PDFDocumento4 pagineCAD Tool Autogeneration of VHDL FFT For FPGA ASIC Implementation PDFilg1Nessuna valutazione finora

- Design For Visually Impaired To Work at Industry Using RFID TechnologyDocumento5 pagineDesign For Visually Impaired To Work at Industry Using RFID Technologyilg1Nessuna valutazione finora

- Development of A Wireless Oral-Feeding Monitoring System For Preterm InfantsDocumento8 pagineDevelopment of A Wireless Oral-Feeding Monitoring System For Preterm Infantsilg1Nessuna valutazione finora

- Mimo Pillow-An Intelligent Cushion Designed With Maternal Heart Beat Vibrations For Comforting Newborn InfantsDocumento7 pagineMimo Pillow-An Intelligent Cushion Designed With Maternal Heart Beat Vibrations For Comforting Newborn Infantsilg1Nessuna valutazione finora

- Smart Home Energy Management System Including Renewable Energy Based On ZigBee and PLCDocumento5 pagineSmart Home Energy Management System Including Renewable Energy Based On ZigBee and PLCilg1Nessuna valutazione finora

- Non-Nutritive Sucking For Promoting Physiologic Stability and Nutrition in Preterm Infants (Review)Documento30 pagineNon-Nutritive Sucking For Promoting Physiologic Stability and Nutrition in Preterm Infants (Review)ilg1Nessuna valutazione finora

- Esquema Arduino UNO R3Documento1 paginaEsquema Arduino UNO R3stangne1Nessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Privileged Planet-Q S and OverviewDocumento9 pagineThe Privileged Planet-Q S and OverviewChad BrosiusNessuna valutazione finora

- Agar Extraction Process For Gracilaria CliftoniiDocumento7 pagineAgar Extraction Process For Gracilaria CliftoniiAdaNessuna valutazione finora

- Dimensional Analysis Similarity Lesson2 Dimensional Parameters HandoutDocumento11 pagineDimensional Analysis Similarity Lesson2 Dimensional Parameters HandoutRizqi RamadhanNessuna valutazione finora

- The Pore-Pressure Coefficients A and B: A (Ao, - AU,) ) Est Mentally B Are Given. BDocumento5 pagineThe Pore-Pressure Coefficients A and B: A (Ao, - AU,) ) Est Mentally B Are Given. BdaveNessuna valutazione finora

- 69kV and Above Oil Immersed Transformer Instruction ManualDocumento30 pagine69kV and Above Oil Immersed Transformer Instruction ManualYaser MajeedNessuna valutazione finora

- Special Types of Matrices: By: Engr. Glenda Alega - de MesaDocumento22 pagineSpecial Types of Matrices: By: Engr. Glenda Alega - de Mesasairin parkNessuna valutazione finora

- 2 Manual de Proteccin Catdica Cathodic Protection HandbooDocumento59 pagine2 Manual de Proteccin Catdica Cathodic Protection Handboogoyote100% (1)

- 2011121503-3-Wannate 8221enDocumento2 pagine2011121503-3-Wannate 8221en8612106535Nessuna valutazione finora

- To Estimate The Charge Induced On Each One of The Two Identical Styrofoam BallsDocumento15 pagineTo Estimate The Charge Induced On Each One of The Two Identical Styrofoam Ballskiran ViratNessuna valutazione finora

- Apendice B - Transport Phenomena - Bird 2edDocumento9 pagineApendice B - Transport Phenomena - Bird 2edarur007Nessuna valutazione finora

- SI-E1-2009-R001-Structural Calculation-15-05-20 PDFDocumento138 pagineSI-E1-2009-R001-Structural Calculation-15-05-20 PDFரதி சுரேஷ்100% (1)

- Adaptive Control by LandauDocumento6 pagineAdaptive Control by LandauSabit RashidNessuna valutazione finora

- 2017 Specimen Markscheme 1Documento14 pagine2017 Specimen Markscheme 1Bassem Khalid YasseenNessuna valutazione finora

- ChapterDocumento18 pagineChapterSharaf HantooshNessuna valutazione finora

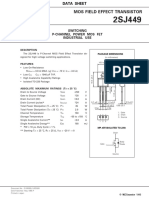

- 2SJ 449 - NecDocumento9 pagine2SJ 449 - NecStevenNessuna valutazione finora

- Penerapan Metode Sonikasi Terhadap Adsorpsi FeIIIDocumento6 paginePenerapan Metode Sonikasi Terhadap Adsorpsi FeIIIappsNessuna valutazione finora

- The Klein-Gordon EquationDocumento22 pagineThe Klein-Gordon EquationAnderson CalistroNessuna valutazione finora

- Simulation work on Fractional Order PIλ Control Strategy for speed control of DC motor based on stability boundary locus methodDocumento7 pagineSimulation work on Fractional Order PIλ Control Strategy for speed control of DC motor based on stability boundary locus methodseventhsensegroupNessuna valutazione finora

- Phase Locked Loop PLLDocumento35 paginePhase Locked Loop PLLenzuekNessuna valutazione finora

- Mechanics of Deformable BodiesDocumento14 pagineMechanics of Deformable BodiesarjunNessuna valutazione finora

- ErrtDocumento101 pagineErrtMadhav KumarNessuna valutazione finora

- Vignan University VSAT 2013 Entrance Test Model Question PaperDocumento5 pagineVignan University VSAT 2013 Entrance Test Model Question PaperPremKumarKalikiri67% (3)

- Divided Wall Column 496Documento6 pagineDivided Wall Column 496GeorgeNessuna valutazione finora

- 02 VF10 Appliance Information enDocumento2 pagine02 VF10 Appliance Information enGabriel ZorattiNessuna valutazione finora

- Imaging The Velocity Profiles in Tubeless Siphon Ow by NMR MicrosDocumento4 pagineImaging The Velocity Profiles in Tubeless Siphon Ow by NMR MicrosLeonardo JaimesNessuna valutazione finora

- Capability Guidance Sheet - Three Point EstimatesDocumento1 paginaCapability Guidance Sheet - Three Point EstimatesSaleha ShakoorNessuna valutazione finora

- Exercise 3 Rice Combine HarvesterDocumento6 pagineExercise 3 Rice Combine Harvesterangelo lorenzo tamayoNessuna valutazione finora

- A Companion To Fourier Analysis For Physics Students: Gol Mohammad NafisiDocumento25 pagineA Companion To Fourier Analysis For Physics Students: Gol Mohammad NafisiIridian ÁvilaNessuna valutazione finora

- B-64504en - 02 Fanuc Series 30i-Pb, Series 31i-Pb Operator's ManualDocumento1.216 pagineB-64504en - 02 Fanuc Series 30i-Pb, Series 31i-Pb Operator's ManualGiang Nguyen VanNessuna valutazione finora