Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

UART

Caricato da

flyingdreamsDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

UART

Caricato da

flyingdreamsCopyright:

Formati disponibili

Hardware Design with VHDL Design Example: UART ECE 443

UART

Universal Asynchronous Receiver and Transmitter

A serial communication protocol that sends parallel data through a serial line.

Typically used with RS-232 standard.

Your FPGA boards have an RS-232 port with a standard 9-pin connector.

The voltages of the FPGA and serial port are different, and therefore a level-

converter circuit is also present on the board.

The board handles the RS-232 standard and therefore our focus is on the UART.

The UART includes both a transmitter and receiver.

The transmitter is a special shift register that loads data in parallel and then

shifts it out bit-by-bit.

The receiver shifts in data bit-by-bit and reassembles the data byte.

The data line is ’1’ when idle.

ECE UNM 1 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Spec

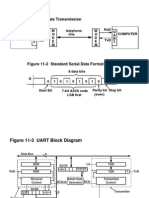

Transmission starts when a start bit (a ’0’) is sent, followed by a number of data bits

(either 6, 7 or 8), an optional partity bit and stop bits (with 1, 1.5 or 2 ’1’s).

idle start stop

d0 d1 d2 d3 d4 d5 d6 d7

This is the transmission of 8 data bits and 1 stop bit.

Note that no clk signal is sent through the serial line.

This requires agreement on the transmission parameters by both the transmitter

and receiver in advance.

This information includes the band rate (number of bits per second), the num-

ber of data bits and stop bits, and whether parity is being used.

Common baud rates are 2400, 4800, 9600 and 19,200.

ECE UNM 2 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem

An oversampling scheme is commonly used to locate the middle position of the trans-

mitted bits, i.e., where the actual sample is taken.

The most common oversampling rate is 16 times the baud rate.

Therefore, each serial bit is sampled 16 times but only one sample is saved as

we will see.

The oversampling scheme using N data bits and M stop bits:

• Wait until the incoming signal becomes ’0’ (the start bit) and then start the sampling

tick cnter.

• When the cnter reaches 7, the incoming signal reaches the middle position of the

start bit. Clear the cnter and restart.

• When the cnter reaches 15, we are at the middle of the first data bit. Retrieve it and

shift into a register. Restart the cnter.

• Repeat the above step N-1 times to retrieve the remaining data bits.

• If optional parity bit is used, repeat this step once more.

• Repeat this step M more times to obtain the stop bits.

ECE UNM 3 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem

The oversampling scheme replaces the function of the clock.

Instead of using the rising edge to sample, the sampling ticks are used to esti-

mate the center position of each bit.

Note that the system clock must be much faster than the baud rate for oversampling

to be possible.

The receiver block diagram consists of three components

rx d_out d_out r_data

rx

clk rx_done_tick rd_uart

s_tick rx_empty

tick UART interface

baud receiver circuit

rate

generator

The interface circuit provides a buffer and status between the UART and the com-

puter or FPGA.

ECE UNM 4 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem

The baud rate generator generates a sampling signal whose frequency is exactly 16

times the UART’s designated baud rate.

To avoid creating a new clock domain, the output of the baud rate generator will

serve to enable ticks within the UART rather than serve as the clk signal.

The whole system will use one clk as we will see.

For a 19,200 baud rate, the sampling rate has to be 307,200 (19,200*16) ticks per

second.

With a system clk at 50 MHz, the baud rate generator need a mod-163 cnter (50

MHz/307,200).

Therefore, the tick output will assert for one clk cycle every 163 clk cycles of the

system clk.

The following code from page 83 of the text can be used to implement a mod-163

cnter.

ECE UNM 5 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: mod-163 cnter

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity mod_m_cnter is

generic(

N: integer := 4;

M: integer := 10;

);

port(

clk, reset: in std_logic;

max_tick: out std_logic;

q: out std_logic_vector(N-1 downto 0);

);

end mod_m_cnter;

architecture arch of mod_m_cnter is

signal r_reg: unsigned(N-1 downto 0);

signal r_next: unsigned(N-1 downto 0);

ECE UNM 6 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: mod-163 cnter

begin

process(clk, reset)

begin

if (reset = ’1’) then

r_reg <= (others => ’0’);

elsif (clk’event and clk=’1’) then

r_reg <= r_next;

end if;

end process;

end arch;

-- next state logic

r_next <= (others => ’0’) when r_reg=(M-1) else

r_reg + 1;

-- output logic

q <= std_logic_vector(r_reg);

max_tick <= ’1’ when r_reg=(M-1) else ’0’;

end arch;

ECE UNM 7 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: UART receiver

The ASMD chart for the receiver is shown below:

idle data stop

F F F

rx = 0 s_tick=1 s_tick=1

s <= 0 F s=15 F s=SB_TICK-1

start s <= s+1

s <= s+1

F s <= 0

s_tick=1 b <= rx&(b>>1) rx_done_tick <= 1

F F

s=7 n=D_BIT-1

s <= s+1 s <= 0 states: idle, start, data, stop

n <= 0 n <= n+1

s_tick is enable tick from

baud generator.

D_BIT indicates the number of data bits and SB_TICK indicates the number of ticks

needed for the stop bits (16, 24 and 32 for 1, 1.5 and 2 stop bits).

ECE UNM 8 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: UART receiver

We will assign D_BIT and SB_TICK to 8 and 16, respectively, in our design.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity uart_rx is

generic(

DBIT: integer := 8;

SB_TICK: integer := 16;

);

port(

clk, reset: in std_logic;

rx: in std_logic;

s_tick: in std_logic;

rx_done_tick: out std_logic;

dout: out std_logic_vctor(7 downto 0)

);

end uart_rx;

ECE UNM 9 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: UART receiver

architecture arch of uart_rx is

type state_type is (idle, start, data, stop);

signal state_reg, state_next: state_type;

signal s_reg, s_next: unsigned(3 downto 0);

signal n_reg, n_next: unsigned(2 downto 0);

signal b_reg, b_next: std_logic_vector(7 downto 0);

begin

process(clk, reset) -- FSMD state and data regs.

begin

if (reset = ’1’) then

state_reg <= idle;

s_reg <= (others => ’0’);

n_reg <= (others => ’0’);

b_reg <= (others => ’0’);

elsif (clk’event and clk=’1’) then

state_reg <= state_next;

s_reg <= s_next;

n_reg <= n_next;

ECE UNM 10 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: UART receiver

b_reg <= b_next;

end if;

end process;

-- next state logic

process (state_reg, s_reg, n_reg, b_reg, s_tick, rx)

begin

state_next <= state_reg;

s_next <= s_reg;

n_next <= n_reg;

b_next <= b_reg;

rx_done_tick <= ’0’;

case state_reg is

when idle =>

if (rx = ’0’) then

state_next <= start;

s_next <= (others => ’0’);

end if;

ECE UNM 11 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: UART receiver

when start =>

if (s_tick = ’1’) then

if (s_reg = 7) then

state_next <= data;

s_next <= (others => ’0’);

n_next <= (others => ’0’);

else

s_next <= s_reg + 1;

end if;

end if;

when data =>

if (s_tick = ’1’) then

if (s_reg = 15) then

s_next <= (others => ’0’);

b_next <= rx & b_reg(7 downto 1);

if (n_reg = (DBIT - 1)) then

state_next <= stop;

else

ECE UNM 12 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: UART receiver

n_next <= n_reg + 1;

end if;

else

s_next <= s_reg + 1;

end if;

end if;

when stop =>

if (s_tick = ’1’) then

if (s_reg = (SB_TICK-1)) then

state_next <= idle;

rx_done_tick <= ’1’;

else

s_next <= s_reg + 1;

end if;

end if;

end case;

end process;

dout <= b_reg; end arch;

ECE UNM 13 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: Interface Circuit

The receiver interface circuit has two functions:

• It provides a mechanism to signal the availability of a new word

• It provides buffer space between the receiver and main system.

Several architectures are possible, including one with a FIFO. Here is one with a flag

FF (to indicate the reception of a data byte) and a one byte buffer.

rx d_out d_out q r_data

rx

clk rx_done_tick en rd_uart

s_tick register

tick UART

baud rx_empty

receiver set_flag flag

rate

generator clr_flag

register rd_uart

Here, rx_done_tick is connected to set_flag while the system connects to clr_flag.

The system checks rx_empty to determine when a data byte is available.

ECE UNM 14 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: Interface Circuit

When rx_done_tick is asserted, the received byte is loaded to the buffer and the flag

FF is asserted.

The receiver can continue to fetch the next byte, giving time for the system to

retrieve the current byte.

library ieee;

use ieee.std_logic_1164.all;

entity flag_buff is

generic(W: integer := 8);

port(

clk, reset: in std_logic;

clr_flag, set_flag: in std_logic;

din: in std_logic_vector(W-1 downto 0);

dout: out std_logic_vector(W-1 downto 0);

flag: out std_logic

);

end flag_buff;

ECE UNM 15 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: Interface Circuit

architecture arch of flag_buff is

signal buf_reg, buf_next: std_logic_vector(W-1 downto

0);

signal flag_reg, flag_next: std_logic;

begin

process(clk, reset)

begin

if (reset = ’1’) then

buf_reg <= (others =>’0’);

flag_reg <= ’0’;

elsif (clk’event and clk=’1’) then

buf_reg <= buf_next;

flag_reg <= flag_next;

end if;

end process;

-- next-state logic

ECE UNM 16 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Receiving Subsystem: Interface Circuit

process (buf_reg, flag_reg, set_flag, clr_flag, din)

begin

buf_next <= buf_reg;

flag_next <= flag_reg;

if (set_flag = ’1’) then

buf_next <= din;

flag_next <= ’1’;

elsif (clr_flag = ’1’) then

flag_next <= ’0’;

end if;

end process;

-- output logic

dout <= buf_reg;

flag <= flag_reg;

end arch;

ECE UNM 17 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Transmitting Subsystem

The UART transmitting subsystem is similar to the receiving subsystem.

It consists of UART transmitter, baud rate generator and interface circuit.

Roles are reversed for the interface circuit, i.e., the system sets the flag FF or writes

the buffer interface circuit while the UART transmitter clears FF or reads the buffer.

The transmitter is essentially a shift register that shifts out data bits.

Since no oversampling is involved, the frequency of the ticks are 16 times

slower than that of the receiver.

However, instead of introducing another cnter, the transmitter usually shares the

baud rate generator and uses an internal cnter to cnt through the 16 ticks.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

ECE UNM 18 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Transmitting Subsystem

entity uart_tx is

generic(

DBIT: integer := 8;

SB_TICK: integer := 16;

);

port(

clk, reset: in std_logic;

tx_start: in std_logic;

s_tick: in std_logic;

din: out std_logic_vctor(7 downto 0)

tx_done_tick: out std_logic;

tx: out std_logic

);

end uart_tx;

ECE UNM 19 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Transmitting Subsystem

architecture arch of uart_tx is

type state_type is (idle, start, data, stop);

signal state_reg, state_next: state_type;

signal s_reg, s_next: unsigned(3 downto 0);

signal n_reg, n_next: unsigned(2 downto 0);

signal b_reg, b_next: std_logic_vector(7 downto 0);

signal tx_reg, tx_next: std_logic;

begin

process(clk, reset) -- FSMD state and data regs.

begin

if (reset = ’1’) then

state_reg <= idle;

s_reg <= (others => ’0’);

n_reg <= (others => ’0’);

b_reg <= (others => ’0’);

tx_reg <= ’1’;

ECE UNM 20 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Transmitting Subsystem

elsif (clk’event and clk=’1’) then

state_reg <= state_next;

s_reg <= s_next;

n_reg <= n_next;

b_reg <= b_next;

tx_reg <= tx_next;

end if;

end process;

-- next state logic

process (state_reg, s_reg, n_reg, b_reg, s_tick,

tx_reg, tx_start, din)

begin

state_next <= state_reg;

s_next <= s_reg;

n_next <= n_reg;

b_next <= b_reg;

tx_next <= tx_reg;

ECE UNM 21 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Transmitting Subsystem

tx_done_tick <= ’0’;

case state_reg is

when idle =>

tx_next <= ’1’;

if (tx_start = ’1’) then

state_next <= start;

s_next <= (others => ’0’);

b_next <= din;

end if;

when start =>

tx_next <= ’0’;

if (s_tick = ’1’) then

if (s_reg = 15) then

state_next <= data;

s_next <= (others => ’0’);

n_next <= (others => ’0’);

else

s_next <= s_reg + 1;

ECE UNM 22 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Transmitting Subsystem

end if;

end if;

when data =>

tx_next <= b_reg(0);

if (s_tick = ’1’) then

if (s_reg = 15) then

s_next <= (others => ’0’);

b_next <= ’0’ & b_reg(7 downto 1);

if (n_reg = (DBIT - 1)) then

state_next <= stop;

else

n_next <= n_reg + 1;

end if;

else

s_next <= s_reg + 1;

end if;

end if;

ECE UNM 23 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

UART Transmitting Subsystem

when stop =>

tx_next <= ’1’;

if (s_tick = ’1’) then

if (s_reg = (SB_TICK-1)) then

state_next <= idle;

rx_done_tick <= ’1’;

else

s_next <= s_reg + 1;

end if;

end if;

end case;

end process;

tx <= tx_reg;

end arch;

ECE UNM 24 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

Entire UART System

Block diagram of whole system

w_data

rx d_out r_data

rx r_data

clk rx_done_tick wr rd_uart

s_tick register

tick UART rx_empty

baud set_flag flag

receiver clr_flag

rate

generator

register rd_uart

tx d_in r_data w_data

w_data

tx wr_uart

tx_done_tick rd

register

s_tick tx_start

tx_full

UART set_flag flag

transmitter clr_flag

register rd_uart

ECE UNM 25 (9/17/08)

Hardware Design with VHDL Design Example: UART ECE 443

Entire UART System

See text for the UART main module that instantiates the entities discussed above.

Note text uses a FIFO buffer so the diagram above is different.

The text also includes a loop-back circuit that instantiates the UART and connects

the outputs of the receiver with the inputs of the transmitter on the FPGA.

It also adds ’1’ to the incoming data before looping it back to the computer.

Windows hyperterminal is discussed as a mechanism to communicate directly to the

serial ports on your computer.

ECE UNM 26 (9/17/08)

Potrebbero piacerti anche

- Topic 6 - Clocking & Met A StabilityDocumento9 pagineTopic 6 - Clocking & Met A Stabilityanish1988100% (1)

- USB To RS-232 ConverterDocumento11 pagineUSB To RS-232 Converteryeateshwarrior100% (1)

- Introduction I2c and SPIDocumento14 pagineIntroduction I2c and SPIHaris Jeelani100% (1)

- Open Core SpiDocumento13 pagineOpen Core SpiBhanu Pratap Singh100% (1)

- Spi ModuleDocumento13 pagineSpi ModuleMuhammadSaeedTahir100% (2)

- UART Wishbone SpecDocumento20 pagineUART Wishbone SpecSandeep Thakur100% (1)

- Embeddded Pic 18f Starter KitDocumento3 pagineEmbeddded Pic 18f Starter KitEmblitz Rajajinagar100% (1)

- Interfacing Example - 16 Character X 2 Line LCD: DescriptionDocumento5 pagineInterfacing Example - 16 Character X 2 Line LCD: DescriptionManish Kumar sharma100% (1)

- Spi and I2cDocumento11 pagineSpi and I2cAbhay Tomar100% (1)

- Brushless DC Electric Motor Control by CPLDDocumento6 pagineBrushless DC Electric Motor Control by CPLDIonela100% (3)

- Inter Integrated Circuit Bus Protocol (I C) : By: Prof. Mitesh LimachiaDocumento53 pagineInter Integrated Circuit Bus Protocol (I C) : By: Prof. Mitesh LimachiaFarman Rizvi100% (2)

- 8086 PPTDocumento30 pagine8086 PPTKavitha Subramaniam100% (1)

- Elc 2014 Usb 0 PDFDocumento96 pagineElc 2014 Usb 0 PDFAhmed Hamouda100% (1)

- Uart Ip Core Specification: Systemverilog VersionDocumento20 pagineUart Ip Core Specification: Systemverilog VersionSujay M100% (1)

- Datasheet lcd03 20x4 B PDFDocumento8 pagineDatasheet lcd03 20x4 B PDFFrancis100% (1)

- Details of ARP and PPPDocumento40 pagineDetails of ARP and PPPYogesh Palkar100% (1)

- E:/#0-2S2017/#1-TEC - SELDI/SAP-02 - Projeto Forno MCU/SELDI - SAP-02 MCU - FW/Forno - DSET-SAP01 - 137-V1.X/forno.hDocumento7 pagineE:/#0-2S2017/#1-TEC - SELDI/SAP-02 - Projeto Forno MCU/SELDI - SAP-02 MCU - FW/Forno - DSET-SAP01 - 137-V1.X/forno.hVinícius Lopes Sampaio100% (1)

- Overview of The Inter-Integrated Circuit (I C) Bus: 2 ECPE 4536 Microprocessor System Design II Virginia TechDocumento7 pagineOverview of The Inter-Integrated Circuit (I C) Bus: 2 ECPE 4536 Microprocessor System Design II Virginia Techdineshvhaval100% (1)

- I2c Rev03Documento17 pagineI2c Rev03varunmr100% (1)

- Agribot Project PresentationDocumento21 pagineAgribot Project Presentationumaiya1990100% (1)

- I2C Protocol in Fpga Using VHDL: Main Project Interim Report As A Partial Fullment of The CurriculumDocumento18 pagineI2C Protocol in Fpga Using VHDL: Main Project Interim Report As A Partial Fullment of The CurriculumShuvra Saha100% (1)

- PIC Microcontroller ArchitectureDocumento20 paginePIC Microcontroller ArchitecturePeeyush Kp100% (1)

- Rekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentDocumento4 pagineRekonstrukt: FPGA Based Forth Development Environment / Forth Based FPGA Development EnvironmentSuraj Kumar100% (1)

- Using The TWI Module As I2C MasterDocumento11 pagineUsing The TWI Module As I2C Mastermithrandair100% (1)

- MicrocontrollersDocumento14 pagineMicrocontrollersanshu4u06100% (1)

- DMA Versus Polling or Interrupt Driven I/ODocumento13 pagineDMA Versus Polling or Interrupt Driven I/OCyrus Patrick Dacoco100% (1)

- Power Dissipation in CMOS Circuits: Advanced VLSI EEE 6405 Slide1 Abm Harun-Ur RashidDocumento28 paginePower Dissipation in CMOS Circuits: Advanced VLSI EEE 6405 Slide1 Abm Harun-Ur RashidAbu RaihanNessuna valutazione finora

- RS-232, RS-422, RS-485 Serial Communication General ConceptsDocumento7 pagineRS-232, RS-422, RS-485 Serial Communication General ConceptsVidhya Dharan100% (1)

- 9-Serial Comm (Autosaved)Documento48 pagine9-Serial Comm (Autosaved)M ADNAN Z100% (1)

- Build A Simple Computer: Lecturer: Pazir AhmadDocumento80 pagineBuild A Simple Computer: Lecturer: Pazir AhmadfayeqNessuna valutazione finora

- Moving Up To ARMDocumento128 pagineMoving Up To ARMlilianfis100% (1)

- BGK MPMC Unit-3 Q and ADocumento21 pagineBGK MPMC Unit-3 Q and AMallesh ArjaNessuna valutazione finora

- Design and Functional Verification of I2C Master Core Using OVMDocumento6 pagineDesign and Functional Verification of I2C Master Core Using OVMPraveen Kumar100% (1)

- Port PDFDocumento16 paginePort PDFdharanika100% (1)

- History of The I2C BusDocumento24 pagineHistory of The I2C BusManoj Kavedia100% (1)

- Register and Its OperationsDocumento56 pagineRegister and Its OperationsSARTHAK VARSHNEYNessuna valutazione finora

- Ladder Logic For PIC and AVRDocumento6 pagineLadder Logic For PIC and AVRTomás Totaro100% (1)

- VHDL 4 RTL ModelsDocumento33 pagineVHDL 4 RTL ModelsNguyễn Minh NghĩaNessuna valutazione finora

- Organization: Basic Computer Organization and DesignDocumento29 pagineOrganization: Basic Computer Organization and DesignGemechisNessuna valutazione finora

- Serial CommunicationsDocumento23 pagineSerial CommunicationsPhuoc Trung Tran100% (1)

- Design of A Micro-Uart For Soc ApplicationDocumento12 pagineDesign of A Micro-Uart For Soc ApplicationUtkarsh Jain100% (1)

- Frequently Asked Questions - AVRDocumento18 pagineFrequently Asked Questions - AVRSagar Gupta100% (2)

- Pic18 Interrupt 2Documento19 paginePic18 Interrupt 2adamwaiz100% (3)

- Chapter 4 PIC IO ProgrammingDocumento28 pagineChapter 4 PIC IO ProgrammingAndy Wo100% (1)

- Bus System & Data TransferDocumento5 pagineBus System & Data Transferlmehta16Nessuna valutazione finora

- Understanding I2C BusDocumento8 pagineUnderstanding I2C BusMai Khoa100% (1)

- DMA Controller (DMAC) : - Data transfer between the μP's main memory & an externalDocumento6 pagineDMA Controller (DMAC) : - Data transfer between the μP's main memory & an externalharinik7100% (1)

- 8259 A FinalDocumento52 pagine8259 A FinalAnitha Joseph100% (1)

- PIC Introduction PDFDocumento46 paginePIC Introduction PDFPeeyush Kp100% (1)

- HBridgeMotorControl With PICDocumento11 pagineHBridgeMotorControl With PICcoceicr100% (3)

- Nxbyte Arm-Legv8Documento15 pagineNxbyte Arm-Legv8Jonathan Manzaki100% (1)

- Tshoot EthernetDocumento11 pagineTshoot Ethernetmrigank shekhar100% (1)

- UartDocumento21 pagineUartSusie MaestreNessuna valutazione finora

- FPGA Implementation of Universal Asynchronous Receiver and Transmitter (UART)Documento13 pagineFPGA Implementation of Universal Asynchronous Receiver and Transmitter (UART)VaseaPupchinNessuna valutazione finora

- Modular UARTDocumento28 pagineModular UARTpreetiNessuna valutazione finora

- UART in VHDL and Verilog For An FPGADocumento10 pagineUART in VHDL and Verilog For An FPGATrọngHữuNguyễnNessuna valutazione finora

- Serial Communication in Embedded SystemsDocumento30 pagineSerial Communication in Embedded SystemsRishabh RanjanNessuna valutazione finora

- ELEC 418 Advanced Digital Systems Dr. Ron Hayne: Images Courtesy of Thomson EngineeringDocumento34 pagineELEC 418 Advanced Digital Systems Dr. Ron Hayne: Images Courtesy of Thomson EngineeringRama KrishnaNessuna valutazione finora

- VHDL UartDocumento53 pagineVHDL UartEhsan Mahdavi100% (1)

- Development Board For Stm8S003F3: by Nitin Chand M S (2018H1400171P), Rohith Krishnan P (2018H1400180P)Documento13 pagineDevelopment Board For Stm8S003F3: by Nitin Chand M S (2018H1400171P), Rohith Krishnan P (2018H1400180P)Thông NguyễnNessuna valutazione finora

- Exercise - Manage Disk QuotasDocumento3 pagineExercise - Manage Disk Quotassumit singhNessuna valutazione finora

- ARRAYSDocumento4 pagineARRAYSOluwamodupe EstherNessuna valutazione finora

- CS Interview Questions: "Real Companies, Real Questions"Documento100 pagineCS Interview Questions: "Real Companies, Real Questions"Akula PranathiNessuna valutazione finora

- Creating HA Device With StarWind Virtual SAN FreeDocumento9 pagineCreating HA Device With StarWind Virtual SAN FreeHarish PatilNessuna valutazione finora

- Turbo HD DVR V3.4.83 - Build170526 Release Notes - ExternalDocumento2 pagineTurbo HD DVR V3.4.83 - Build170526 Release Notes - ExternalLuis Rivera MendozaNessuna valutazione finora

- Definition - What Does Cache Memory Mean?Documento5 pagineDefinition - What Does Cache Memory Mean?John YohansNessuna valutazione finora

- Reset Sony HCD-GR8Documento1 paginaReset Sony HCD-GR8pepitito22Nessuna valutazione finora

- TP Debug InfoDocumento198 pagineTP Debug InfoAnju BalaNessuna valutazione finora

- Typeedit v11 69 PDFDocumento3 pagineTypeedit v11 69 PDFJacobNessuna valutazione finora

- UMA CardDocumento10 pagineUMA CardramireddyNessuna valutazione finora

- AIX Performance TuningDocumento42 pagineAIX Performance Tuningmcfaria20009603Nessuna valutazione finora

- Web API Apps Nguyen Thanh Bao LongDocumento5.326 pagineWeb API Apps Nguyen Thanh Bao Longthanhhaiit99Nessuna valutazione finora

- CS6611 2013 Regulation-Lesson plan-CS6611-MOBILE APP DEVELOP LAB - 6th SemDocumento3 pagineCS6611 2013 Regulation-Lesson plan-CS6611-MOBILE APP DEVELOP LAB - 6th SemaddssdfaNessuna valutazione finora

- Instruction For Tabula (Python)Documento33 pagineInstruction For Tabula (Python)SEAN YONATHAN TANJUNG ,Nessuna valutazione finora

- HDFView UsersGuideDocumento84 pagineHDFView UsersGuidekrokoboneNessuna valutazione finora

- EQQQ1MSTDocumento42 pagineEQQQ1MSTrajesh_kumar282Nessuna valutazione finora

- Session 17Documento2 pagineSession 17ganeshNessuna valutazione finora

- LogDocumento19 pagineLogBustamin TaepabuNessuna valutazione finora

- STT Hãng Công Cụ Kết Nối: 1 Siemens Tool Siemens Rs232 To Usb (db9 To Usb + rs232 Đực To rs232 Cái)Documento2 pagineSTT Hãng Công Cụ Kết Nối: 1 Siemens Tool Siemens Rs232 To Usb (db9 To Usb + rs232 Đực To rs232 Cái)TocXoanBkaNessuna valutazione finora

- Uvm Cookbook CollectionDocumento54 pagineUvm Cookbook CollectionQuý Trương QuangNessuna valutazione finora

- Modem Huawei 1750 USB (10 BL) Download Speed Up To 7,2Mbps 240.000Documento2 pagineModem Huawei 1750 USB (10 BL) Download Speed Up To 7,2Mbps 240.000Ŝëtýáwän ŴŔNessuna valutazione finora

- APM210+Lab+ +Core+APM+I +essentials+ +Student+Lab+GuideDocumento60 pagineAPM210+Lab+ +Core+APM+I +essentials+ +Student+Lab+GuideGurvinder Singh SethiNessuna valutazione finora

- 8086 ArchitectureDocumento9 pagine8086 ArchitecturegiridharsinghNessuna valutazione finora

- Cisco MDS 9700 Series: Multilayer SAN DirectorsDocumento2 pagineCisco MDS 9700 Series: Multilayer SAN DirectorsFernandoNessuna valutazione finora

- 8.3.3.3 Lab - Collecting and Analyzing NetFlow Data - ILM PDFDocumento13 pagine8.3.3.3 Lab - Collecting and Analyzing NetFlow Data - ILM PDFEl Amrani MoutiaNessuna valutazione finora

- Lenovo-Legion-5 AMD 15INCH PDFDocumento2 pagineLenovo-Legion-5 AMD 15INCH PDFManish SinghNessuna valutazione finora

- Hotel Management System Project ReportDocumento10 pagineHotel Management System Project Reportkatha_shekhar75% (4)

- Commodore Magazine Vol-10-N05 1989 MayDocumento100 pagineCommodore Magazine Vol-10-N05 1989 MaySteven D100% (2)

- Huawei E220 Hsdpa Usb Modem User ManualDocumento45 pagineHuawei E220 Hsdpa Usb Modem User ManualAdam HartonoNessuna valutazione finora

- Invitation To Computer Science 8Th Edition G Michael Schneider Full ChapterDocumento67 pagineInvitation To Computer Science 8Th Edition G Michael Schneider Full Chaptererika.hemmings524100% (4)