Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

8-bit A/D Converter Control Registers

Caricato da

Ricardo José ItriagoDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

8-bit A/D Converter Control Registers

Caricato da

Ricardo José ItriagoCopyright:

Formati disponibili

M

21

Convertor

8-bit A/D

Section 21. 8-bit A/D Converter

HIGHLIGHTS

This section of the manual contains the following major topics:

21.1 Introduction ..................................................................................................................21-2

21.2 Control Registers .........................................................................................................21-3

21.3 Operation .....................................................................................................................21-5

21.4 A/D Acquisition Requirements .....................................................................................21-6

21.5 Selecting the A/D Conversion Clock ............................................................................21-8

21.6 Configuring Analog Port Pins.......................................................................................21-9

21.7 A/D Conversions ........................................................................................................21-10

21.8 A/D Operation During Sleep ......................................................................................21-12

21.9 A/D Accuracy/Error ....................................................................................................21-13

21.10 Effects of a RESET ....................................................................................................21-13

21.11 Use of the CCP Trigger ..............................................................................................21-14

21.12 Connection Considerations ........................................................................................21-14

21.13 Transfer Function .......................................................................................................21-14

21.14 Initialization ................................................................................................................21-15

21.15 Design Tips ................................................................................................................21-16

21.16 Related Application Notes..........................................................................................21-17

21.17 Revision History .........................................................................................................21-18

Note: Please refer to Appendix C.3 or device Data Sheet to determine which devices use

this module.

1997 Microchip Technology Inc. DS31021A page 21-1

PICmicro MID-RANGE MCU FAMILY

21.1 Introduction

The analog-to-digital (A/D) converter module has up to eight analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number. The

output of the sample and hold is the input into the converter, which generates the result via suc-

cessive approximation. The analog reference voltage is software selectable to either the device’s

positive supply voltage (VDD) or the voltage level on the VREF pin. The A/D converter has a

unique feature of being able to operate while the device is in SLEEP mode.

The A/D module has three registers. These registers are:

• A/D Result Register (ADRES)

• A/D Control Register0 (ADCON0)

• A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Figure 21-1, controls the operation of the A/D module. The

ADCON1 register, shown in Figure 21-2, configures the functions of the port pins. The I/O pins

can be configured as analog inputs (one I/O can also be a voltage reference) or as digital I/O.

The block diagram of the A/D module is shown in Figure 21-1.

Figure 21-1: 8-bit A/D Block Diagram

CHS2:CHS0

111

AN7

110

AN6

101

AN5

100

AN4

VAIN

(Input voltage) 011

AN3/VREF

010

8-bit A/D AN2

Converter

001

AN1

VDD (1) 000

AN0

000 or

VREF 010 or

100

(Reference

voltage) 001 or

011 or

101

PCFG2:PCFG0

Note: On some devices this is a separate pin called AVDD. This allows the A/D VDD to be connected to a precise voltage source.

DS31021A-page 21-2 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

21.2 Control Registers

21

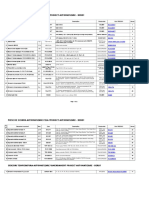

Register 21-1: ADCON0 Register

Converter

8-bit A/D

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

ADCS1 ADCS0 CHS2 CHS1 CHS0 GO/DONE Resv ADON

bit 7 bit 0

bit 7:6 ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = FOSC/2

01 = FOSC/8

10 = FOSC/32

11 = FRC (clock derived from the internal A/D RC oscillator)

bit 5:3 CHS2:CHS0: Analog Channel Select bits

000 = channel 0, (AN0)

001 = channel 1, (AN1)

010 = channel 2, (AN2)

011 = channel 3, (AN3)

100 = channel 4, (AN4)

101 = channel 5, (AN5)

110 = channel 6, (AN6)

111 = channel 7, (AN7)

Note: For devices that do not implement the full 8 A/D channels, the unimplemented selec-

tions are reserved. Do not select any unimplemented channels.

bit 2 GO/DONE: A/D Conversion Status bit

When ADON = 1

1 = A/D conversion in progress

(Setting this bit starts the A/D conversion. This bit is automatically cleared

by hardware when the A/D conversion is complete)

0 = A/D conversion not in progress

bit 1 Reserved: Always maintain this bit cleared.

bit 0 ADON: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shutoff and consumes no operating current

Legend

R = Readable bit W = Writable bit

U = Unimplemented bit, read as ‘0’ - n = Value at POR reset

1997 Microchip Technology Inc. DS31021A-page 21-3

PICmicro MID-RANGE MCU FAMILY

Register 21-2: ADCON1 Register

U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0

— — — — — PCFG2 PCFG1 PCFG0

bit 7 bit 0

bit 7:3 Unimplemented: Read as '0'

bit 2:0 PCFG2:PCFG0: A/D Port Configuration Control bits

PCFG2:PCFG0 AN7 AN6 AN5 AN4 AN3 AN2 AN1 AN0

000 A A A A A A A A

001 A A A A VREF A A A

010 D D D A A A A A

011 D D A A VREF A A A

100 D D D D A D A A

101 D D D D VREF D A A

11x D D D D D D D D

A = Analog input D = Digital I/O

Note: When AN3 is selected as VREF, the A/D reference is the voltage on the AN3

pin. When AN3 is selected as an analog input (A), then the voltage reference

for the A/D is the device VDD.

Legend

R = Readable bit W = Writable bit

U = Unimplemented bit, read as ‘0’ - n = Value at POR reset

Note 1: On any device reset, the Port pins multiplexed with analog functions (ANx) are

forced to be an analog input.

DS31021A-page 21-4 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

21.3 Operation

21

When the A/D conversion is complete, the result is loaded into the ADRES register, the

Converter

GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit, ADIF, is set.

8-bit A/D

After the A/D module has been configured as desired, the selected channel must be acquired

before the conversion is started. The analog input channels must have their corresponding TRIS

bits selected as an input. To determine acquisition time, see Subsection 21.4 “A/D Acquisition

Requirements.” After this acquisition time has elapsed the A/D conversion can be started. The

following steps should be followed for doing an A/D conversion:

1. Configure the A/D module:

• Configure analog pins / voltage reference / and digital I/O (ADCON1)

• Select A/D input channel (ADCON0)

• Select A/D conversion clock (ADCON0)

• Turn on A/D module (ADCON0)

2. Configure A/D interrupt (if desired):

• Clear the ADIF bit

• Set the ADIE bit

• Set the GIE bit

3. Wait the required acquisition time.

4. Start conversion:

• Set the GO/DONE bit (ADCON0)

5. Wait for A/D conversion to complete, by either:

• Polling for the GO/DONE bit to be cleared

OR

• Waiting for the A/D interrupt

6. Read A/D Result register (ADRES), clear the ADIF bit, if required.

7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is

defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

Figure 21-2 shows the conversion sequence, and the terms that are used. Acquisition time is the

time that the A/D module’s holding capacitor is connected to the external voltage level. Then

there is the conversion time of 10 TAD, which is started when the GO bit is set. The sum of these

two times is the sampling time. There is a minimum acquisition time to ensure that the holding

capacitor is charged to a level that will give the desired accuracy for the A/D conversion.

Figure 21-2: A/D Conversion Sequence

A/D Sample Time

Acquisition Time Conversion Time

A/D conversion complete,

result is loaded in ADRES register.

Holding capacitor begins acquiring

voltage level on selected channel.

ADIF bit is set.

When A/D conversion is started (setting the GO bit).

Holding capacitor is disconnected from the analog input before

the conversion is started.

When A/D holding capacitor start to charge.

After A/D conversion, or new A/D channel is selected.

1997 Microchip Technology Inc. DS31021A-page 21-5

PICmicro MID-RANGE MCU FAMILY

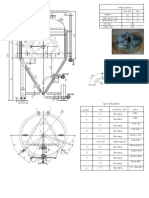

21.4 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must

be allowed to fully charge to the input channel voltage level. The analog input model is shown in

Figure 21-3. The source impedance (RS) and the internal sampling switch (RSS) impedance

directly affect the time required to charge the capacitor CHOLD. The sampling switch (RSS) imped-

ance varies over the device voltage (VDD) (Figure 21-3). The maximum recommended imped-

ance for analog sources is 10 kΩ. After the analog input channel is selected (changed) the

acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 21-1 may be used. This equation assumes

that 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed

for the A/D to meet its specified resolution.

Equation 21-1: Acquisition Time

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time +

Temperature Coefficient

= TAMP + TC + TCOFF

Equation 21-2: A/D Minimum Charging Time

VHOLD = (VREF - (VREF/512)) • (1 - e(-Tc/CHOLD(RIC + RSS + RS)))

or

Tc = -(51.2 pF)(1 kΩ + RSS + RS) ln(1/511)

Example 21-1 shows the calculation of the minimum required acquisition time TACQ. This calcu-

lation is based on the following system assumptions.

Rs = 10 kΩ

Conversion Error ≤ 1/2 LSb

VDD = 5V → Rss = 7 kΩ (see graph in Figure 21-3)

Temperature = 50°C (system max.)

VHOLD = 0V @ time = 0

Example 21-1: Calculating the Minimum Required Acquisition Time

TACQ = TAMP + TC + TCOFF

TACQ = 5 µs + Tc + [(Temp - 25°C)(0.05 µs/°C)]

TC = -CHOLD (RIC + RSS + RS) ln(1/512)

-51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020)

-51.2 pF (18 kΩ) ln(0.0020)

-0.921 µs (-6.2146)

5.724 µs

TACQ = 5 µs + 5.724 µs + [(50°C - 25°C)(0.05 µs/°C)]

10.724 µs + 1.25 µs

11.974 µs

DS31021A-page 21-6 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

21

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself

out.

Note 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

Converter

8-bit A/D

Note 3: The maximum recommended impedance for analog sources is 10 kΩ. This is

required to meet the pin leakage specification.

Note 4: After a conversion has completed, a 2.0 TAD delay must complete before acquisition

can begin again. During this time the holding capacitor is not connected to the

selected A/D input channel.

Figure 21-3: Analog Input Model

VDD

Sampling

Switch

VT = 0.6V

Rs ANx RIC ≤ 1k SS RSS

VAIN CPIN I leakage

VT = 0.6V CHOLD = 51.2 pF

5 pF ± 500 nA

VSS

Legend CPIN = input capacitance

6V

VT = threshold voltage 5V

I LEAKAGE = leakage current at the pin due to VDD 4V

various junctions 3V

RIC = interconnect resistance 2V

SS = sampling switch

CHOLD = sample/hold capacitance (from DAC) 5 6 7 8 9 10 11

VAIN = Analog input voltage

Sampling Switch

( kΩ )

1997 Microchip Technology Inc. DS31021A-page 21-7

PICmicro MID-RANGE MCU FAMILY

21.5 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5 TAD per 8-bit

conversion. The source of the A/D conversion clock is software selected. The four possible

options for TAD are:

• 2TOSC

• 8TOSC

• 32TOSC

• Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a mini-

mum TAD time of 1.6 µs for all devices, as shown in parameter 130 of the devices electrical spec-

ifications.

Table 21-1 and Table 21-2 show the resultant TAD times derived from the device operating fre-

quencies and the A/D clock source selected.

Table 21-1: TAD vs. Device Operating Frequencies (for Standard, C, Devices)

AD Clock Source (TAD) Device Frequency

Operation ADCS1:ADCS0 20 MHz 5 MHz 1.25 MHz 333.33 kHz

2TOSC 00 100 ns(2) 400ns(2) 1.6 µs 6 µs

8TOSC 01 400 ns(2) 1.6 µs 6.4 µs 24 µs(3)

32TOSC 10 1.6 µs 6.4 µs 25.6 µs (3) 96 µs(3)

RC 11 2 - 6 µs(1,4) 2 - 6 µs (1,4) 2 - 6 µs(1,4) 2 - 6 µs(1)

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4 µs.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: For device frequencies above 1 MHz, the device must be in SLEEP for the entire conversion, or the A/D

accuracy may be out of specification.

Table 21-2: TAD vs. Device Operating Frequencies (for Extended, LC, Devices)

AD Clock Source (TAD) Device Frequency

Operation ADCS1:ADCS0 4 MHz 2 MHz 1.25 MHz 333.33 kHz

2TOSC 00 500 ns(2) 1.0 µs(2) 1.6 µs(2) 6 µs

8TOSC 01 2.0 µs (2) 4.0 µs 6.4 µs 24 µs(3)

32TOSC 10 8.0 µs 16.0 µs 25.6 µs(3) 96 µs(3)

RC 11 3 - 9 µs(1,4) 3 - 9 µs(1,4) 3 - 9 µs(1,4) 3 - 9 µs(1)

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 6 µs.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: For device frequencies above 1 MHz, the device must be in SLEEP for the entire conversion, or the A/D

accuracy may be out of specification.

DS31021A-page 21-8 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

21.6 Configuring Analog Port Pins

21

ADCON1 and the corresponding TRIS registers control the operation of the A/D port pins. The

port pins that are desired as analog inputs must have their corresponding TRIS bits set (input).

Converter

8-bit A/D

If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

Note 1: When reading the port register, all pins configured as analog input channels will

read as cleared (a low level). Pins configured as digital inputs, will convert an analog

input. Analog levels on a digitally configured input will not affect the conversion

accuracy.

Note 2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0

pins), may cause the input buffer to consume current that is out of the devices spec-

ification.

1997 Microchip Technology Inc. DS31021A-page 21-9

PICmicro MID-RANGE MCU FAMILY

21.7 A/D Conversions

Example 21-2 show how to perform an A/D conversion. The I/O pins are configured as analog

inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D

conversion clock is FRC. The conversion is performed on the AN0 channel.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D,

due to the required acquition time requirement.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES

register will NOT be updated with the partially completed A/D conversion sample. That is, the

ADRES register will continue to contain the value of the last completed conversion (or the last

value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required

before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started

on the selected channel.

Example 21-2: Doing an A/D Conversion

BSF STATUS, RP0 ; Select Bank1

CLRF ADCON1 ; Configure A/D inputs

BSF PIE1, ADIE ; Enable A/D interrupts

BCF STATUS, RP0 ; Select Bank0

MOVLW 0xC1 ; RC Clock, A/D is on, Channel 0 is selected

MOVWF ADCON0 ;

BCF PIR1, ADIF ; Clear A/D interrupt flag bit

BSF INTCON, PEIE ; Enable peripheral interrupts

BSF INTCON, GIE ; Enable all interrupts

;

; Ensure that the required sampling time for the selected input

; channel has elapsed. Then the conversion may be started.

;

BSF ADCON0, GO ; Start A/D Conversion

: ; The ADIF bit will be set and the GO/DONE

: ; bit is cleared upon completion of the

: ; A/D Conversion.

Figure 21-4: A/D Conversion TAD Cycles

TAD1 TAD2 TAD3 TAD4 TAD5 TAD6 TAD7 TAD8 TAD9 TAD10 TAD11

b7 b6 b5 b4 b3 b2 b1 b0 b0

Holding capacitor is disconnected Next Q4: ADRES is loaded

from analog input GO bit is cleared

ADIF bit is set

Set GO bit

Holding capacitor is connected to analog input

DS31021A-page 21-10 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

Figure 21-5: Flowchart of A/D Operation

21

ADON = 0

Converter

8-bit A/D

Yes

ADON = 0?

No

Acquire

Selected Channel

Yes

GO = 0?

No

A/D Clock

Yes Start of A/D SLEEP Yes Finish Conversion

Conversion Delayed Instruction? GO = 0

= RC? 1 Instruction Cycle ADIF = 1

No No

Yes Abort Conversion Finish Conversion Wake-up Yes

Device in GO = 0 From Sleep? Wait 2TAD

SLEEP? ADIF = 0 GO = 0

ADIF = 1

No No

Finish Conversion SLEEP Stay in Sleep

Power-down A/D Wait 2TAD Power-down A/D

GO = 0

ADIF = 1

Wait 2TAD

1997 Microchip Technology Inc. DS31021A-page 21-11

PICmicro MID-RANGE MCU FAMILY

21.7.1 Faster Conversion - Lower Resolution Trade-off

Not all applications require a result with 8-bits of resolution, but may instead require a faster con-

version time. The A/D module allows users to make the trade-off of conversion speed to resolu-

tion. Regardless of the resolution required, the acquisition time is the same. To speed up the

conversion, the clock source of the A/D module may be switched so that the TAD time violates

the minimum specified time (see the applicable electrical specification). Once the TAD time vio-

lates the minimum specified time, all the following A/D result bits are not valid (see A/D Conver-

sion Timing in the Electrical Specifications section). The clock sources may only be switched

between the three oscillator versions (cannot be switched from/to RC). The equation to deter-

mine the time before the oscillator can be switched is as follows:

Conversion time = TAD + N • TAD + (10 - N)(2TOSC)

Where: N = number of bits of resolution required.

Since the TAD is based from the device oscillator, the user must use some method (a timer, soft-

ware loop, etc.) to determine when the A/D oscillator may be changed. Example 21-3 shows a

comparison of time required for a conversion with 4-bits of resolution, versus the 8-bit resolution

conversion. The example is for devices operating at 20 MHz (The A/D clock is programmed for

32TOSC), and assumes that immediately after 5TAD, the A/D clock is programmed for 2TOSC.

The 2TOSC violates the minimum TAD time since the last 4-bits will not be converted to correct

values.

Example 21-3: 4-bit vs. 8-bit Conversion Times

Freq. Resolution

(MHz)(1) 4-bit 8-bit

TAD 20 1.6 µs 1.6 µs

TOSC 20 50 ns 50 ns

TAD + N • TAD + (10 - N)(2TOSC) 20 8.6 µs 17.6 µs

Note 1: A minimum TAD time of 1.6 µs is required.

2: If the full 8-bit conversion is required, the A/D clock source should not be changed.

21.8 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set

to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one

instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed,

which eliminates all internal digital switching noise from the conversion. When the conversion is

completed the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the

A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled,

the A/D module will then be turned off (to conserve power), although the ADON bit will remain

set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the

present conversion to be aborted and the A/D module to be turned off, though the ADON bit will

remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC

(ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, the GO/DONE bit

must be set, followed by the SLEEP instruction.

DS31021A-page 21-12 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

21.9 A/D Accuracy/Error

21

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate

to high frequencies, TAD should be derived from the device oscillator.

Converter

8-bit A/D

The absolute accuracy specified for the A/D converter includes the sum of all contributions for

quantization error, integral error, differential error, full scale error, offset error, and monotonicity.

It is defined as the maximum deviation from an actual transition versus an ideal transition for any

code. The absolute error of the A/D converter is specified at < ±1 LSb for VDD = VREF (over the

device’s specified operating range). However, the accuracy of the A/D converter will degrade as

VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the

quantization of the analog input to a digital code. Quantization error is typically ± 1/2 LSb and is

inherent in the analog to digital conversion process. The only way to reduce quantization error is

to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code.

Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or

introduced into a system through the interaction of the total leakage current and source imped-

ance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal tran-

sition adjusted for offset error. This error appears as a change in slope of the transfer function.

The difference in gain error to full scale error is that full scale does not take offset error into

account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated

out of the system. Integral non-linearity error measures the actual code transition versus the ideal

code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width.

This measure is unadjusted.

The maximum pin leakage current is specified in the Device Data Sheet electrical specification

parameter D060.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate

to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the

minimum and should be minimized to reduce inaccuracies due to noise and sampling capacitor

bleed off.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC

clock source selection is required. In this mode, the digital noise from the modules in SLEEP are

stopped. This method gives high accuracy.

21.10 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off,

and any conversion is aborted. The value that is in the ADRES register is not modified for a

Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

1997 Microchip Technology Inc. DS31021A-page 21-13

PICmicro MID-RANGE MCU FAMILY

21.11 Use of the CCP Trigger

An A/D conversion may be started by the “special event trigger” of a CCP module. This requires

that the CCPxM3:CCPxM0 bits (CCPxCON<3:0>) be programmed as 1011 and that the A/D

module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, start-

ing the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automat-

ically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to

the desired location). The appropriate analog input channel must be selected and the minimum

acquisition done before the “special event trigger” sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the “special event trigger” will be

ignored by the A/D module, but will still reset the Timer1 counter.

21.12 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.3V, then the accuracy

of the conversion is out of specification.

An external RC filter can sometimes be added for anti-aliasing of the input signal. The R compo-

nent should be selected to ensure that the total source impedance is kept under the 10 kΩ rec-

ommended specification. Any external components connected (via hi-impedance) to an analog

input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

21.13 Transfer Function

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the

analog input voltage (VAIN) is 1 LSb (or Analog VREF / 256) (Figure 21-6).

Figure 21-6: A/D Transfer Function

FFh

Digital code output

FEh

04h

03h

02h

01h

00h

(full scale)

255 LSb

256 LSb

0.5 LSb

1 LSb

2 LSb

3 LSb

4 LSb

Analog input voltage

DS31021A-page 21-14 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

21.14 Initialization

21

Example 21-4 shows the initialization of the A/D module for the PIC16C74A

Converter

8-bit A/D

Example 21-4: A/D Initialization (for PIC16C74A)

BSF STATUS, RP0 ; Select Bank1

CLRF ADCON1 ; Configure A/D inputs

BSF PIE1, ADIE ; Enable A/D interrupts

BCF STATUS, RP0 ; Select Bank0

MOVLW 0xC1 ; RC Clock, A/D is on, Channel 0 is selected

MOVWF ADCON0 ;

BCF PIR1, ADIF ; Clear A/D interrupt flag bit

BSF INTCON, PEIE ; Enable peripheral interrupts

BSF INTCON, GIE ; Enable all interrupts

;

; Ensure that the required sampling time for the selected input

; channel has elapsed. Then the conversion may be started.

;

BSF ADCON0, GO ; Start A/D Conversion

: ; The ADIF bit will be set and the GO/DONE

: ; bit is cleared upon completion of the

: ; A/D Conversion.

1997 Microchip Technology Inc. DS31021A-page 21-15

PICmicro MID-RANGE MCU FAMILY

21.15 Design Tips

Question 1: I am using one of your PIC16C7X devices, and I find that the Analog to Dig-

ital Converter result is not always accurate. What can I do to improve accu-

racy?

Answer 1:

1. Make sure you are meeting all of the timing specifications. If you are turning the A/D mod-

ule off and on, there is a minimum delay you must wait before taking a sample, if you are

changing input channels, there is a minimum delay you must wait for this as well, and

finally there is Tad, which is the time selected for each bit conversion. This is selected in

ADCON0 and should be between 2 and 6µs. If TAD is too short, the result may not be fully

converted before the conversion is terminated, and if TAD is made too long the voltage on

the sampling capacitor can droop before the conversion is complete. These timing speci-

fications are provided in the data book in a table or by way of a formula, and should be

looked up for your specific part and circumstances.

2. Often the source impedance of the analog signal is high (greater than 1k ohms) so the

current drawn from the source to charge the sample capacitor can affect accuracy. If the

input signal does not change too quickly, try putting a 0.1 µF capacitor on the analog input.

This capacitor will charge to the analog voltage being sampled, and supply the instanta-

neous current needed to charge the 51.2 pf internal holding capacitor.

3. Finally, straight from the data book: “In systems where the device frequency is low, use of

the A/D clock derived from the device oscillator is preferred...this reduces, to a large

extent, the effects of digital switching noise.” and “In systems where the device will enter

SLEEP mode after start of A/D conversion, the RC clock source selection is required. This

method gives the highest accuracy.”

Question 2: After starting an A/D conversion may I change the input channel (for my

next conversion)?

Answer 2:

After the holding capacitor is disconnected from the input channel, one TAD after the GO bit is

set, the input channel may be changed.

Question 3: Do you know of a good reference on A/D’s?

Answer 3:

A very good reference for understanding A/D conversions is the “Analog-Digital Conversion

Handbook” third edition, published by Prentice Hall (ISBN 0-13-03-2848-0).

DS31021A-page 21-16 1997 Microchip Technology Inc.

Section 21. 8-bit A/D Converter

21.16 Related Application Notes

21

This section lists application notes that are related to this section of the manual. These applica-

tion notes may not be written specifically for the Mid-Range MCU family (that is they may be writ-

Converter

8-bit A/D

ten for the Base-Line, or High-End families), but the concepts are pertinent, and could be used

(with modification and possible limitations). The current application notes related to the 8-bit A/D

are:

Title Application Note #

Using the Analog to Digital Converter AN546

Four Channel Digital Voltmeter with Display and Keyboard AN557

1997 Microchip Technology Inc. DS31021A-page 21-17

PICmicro MID-RANGE MCU FAMILY

21.17 Revision History

Revision A

This is the initial released revision of the 8-bit A/D module description.

DS31021A-page 21-18 1997 Microchip Technology Inc.

Potrebbero piacerti anche

- Hosa User GuideDocumento258 pagineHosa User GuideKarim ShahbazNessuna valutazione finora

- Small Adt MkII Elec SchematicsDocumento19 pagineSmall Adt MkII Elec SchematicsSMM ENTREPRISENessuna valutazione finora

- Axe FX II Owners ManualDocumento201 pagineAxe FX II Owners ManualJuan Carlos Fiallos Rodas100% (1)

- Hino 700 Brake EquipmentDocumento42 pagineHino 700 Brake Equipmentjoki marzuki100% (1)

- Manual de Partes Bob CatDocumento455 pagineManual de Partes Bob CatJugaro Oscar100% (2)

- Channel Estimation With MatlabDocumento34 pagineChannel Estimation With Matlabsaeedmap95% (19)

- Diagrama de Fuente BA21F0F0102 - Fuente Philips TV LCDDocumento1 paginaDiagrama de Fuente BA21F0F0102 - Fuente Philips TV LCDneumatraxxx83% (35)

- EQ Cheatsheet MixcloudDocumento43 pagineEQ Cheatsheet MixcloudВалентин Иванов100% (1)

- This Document Has Been Printed From SPI . Not For Resale: Engine Management SystemDocumento10 pagineThis Document Has Been Printed From SPI . Not For Resale: Engine Management SystemHaidar Al Mosawi100% (1)

- Information TheoryDocumento116 pagineInformation TheoryTahir SiddiquiNessuna valutazione finora

- Advanced VAV Control Sequences - Taylor Engineering - 2013Documento122 pagineAdvanced VAV Control Sequences - Taylor Engineering - 2013Steve JacobsonNessuna valutazione finora

- BS1 - Trip - Close Coil Voltage Drop Calculation Rev ADocumento11 pagineBS1 - Trip - Close Coil Voltage Drop Calculation Rev Apriyanka236Nessuna valutazione finora

- VHDL Fir FilterDocumento31 pagineVHDL Fir FilterSyam SanalNessuna valutazione finora

- Amkasyn - Aw - 1326 (Inglés)Documento21 pagineAmkasyn - Aw - 1326 (Inglés)Isao TomitaNessuna valutazione finora

- 18 12bit AD ConverterDocumento38 pagine18 12bit AD Converternicolas8702Nessuna valutazione finora

- Universal PBA Operation GuideDocumento7 pagineUniversal PBA Operation GuideEdison EspinalNessuna valutazione finora

- CPM1A-DA041: Operating ManualDocumento2 pagineCPM1A-DA041: Operating Manualomnitech2Nessuna valutazione finora

- Servo Amplifier VT 1600 Series 3X Data SheetDocumento4 pagineServo Amplifier VT 1600 Series 3X Data SheetMagno SalgadoNessuna valutazione finora

- Vega EL 11Documento60 pagineVega EL 11shadowNessuna valutazione finora

- L1000A Technical Manual Addendum - YASKAWA AC DriveDocumento89 pagineL1000A Technical Manual Addendum - YASKAWA AC Drivem.alfarez87gmail.comNessuna valutazione finora

- Sanyo SM28DN7CDocumento32 pagineSanyo SM28DN7Ctechols.clNessuna valutazione finora

- Monte Carlo SpiceDocumento13 pagineMonte Carlo Spicetoufik bendibNessuna valutazione finora

- Re 30264Documento8 pagineRe 30264Ismail CivgazNessuna valutazione finora

- Isolated Continuous Conduction Mode Flyback Using The TPS55340Documento16 pagineIsolated Continuous Conduction Mode Flyback Using The TPS55340pietisc pietiscNessuna valutazione finora

- An4050 Stevalisv012v1 Lithiumion Solar Battery Charger StmicroelectronicsDocumento17 pagineAn4050 Stevalisv012v1 Lithiumion Solar Battery Charger Stmicroelectronicsashraf.imraishNessuna valutazione finora

- Ve 20SNDocumento26 pagineVe 20SNVladimirNessuna valutazione finora

- Ps-Fela (Berd) Date TehniceDocumento2 paginePs-Fela (Berd) Date Tehnicecorina_maria_eneNessuna valutazione finora

- CNC SERVO ADJUSTMENT GUIDEDocumento120 pagineCNC SERVO ADJUSTMENT GUIDEAlisson cruzNessuna valutazione finora

- Ispravljačza KočnicuDocumento8 pagineIspravljačza KočnicuAhmet HrustićNessuna valutazione finora

- Sanyo Eb8-A Ce21dn9fDocumento26 pagineSanyo Eb8-A Ce21dn9fvideosonNessuna valutazione finora

- Service Manual LCD Television: Model No. LCD-23XL2Documento32 pagineService Manual LCD Television: Model No. LCD-23XL2FEDE514Nessuna valutazione finora

- Op Amp StabilityDocumento32 pagineOp Amp Stabilityapdim79Nessuna valutazione finora

- NA3 AND NA4 - PARTS LISTING INDEX (p100)Documento20 pagineNA3 AND NA4 - PARTS LISTING INDEX (p100)Julio BacilioNessuna valutazione finora

- IVPAUserGuideDocumento16 pagineIVPAUserGuideYouba FofanaNessuna valutazione finora

- Compressed Air Manual Tcm44-1249312Documento8 pagineCompressed Air Manual Tcm44-1249312Osama Kamel ElghitanyNessuna valutazione finora

- Voltage Reference Scalling Techniques Increase The Accuaracy of The Converter As Well As The ResolutionDocumento6 pagineVoltage Reference Scalling Techniques Increase The Accuaracy of The Converter As Well As The Resolutionmehdi.bzinebNessuna valutazione finora

- FR-E800 Instruction Manual (Function)Documento420 pagineFR-E800 Instruction Manual (Function)Diogo CampezattoNessuna valutazione finora

- Man 8040T NFDocumento38 pagineMan 8040T NFjean bartNessuna valutazione finora

- Cp1w-Ad Da Mad Ts DRT SRT Pages From W471-E1-04Documento70 pagineCp1w-Ad Da Mad Ts DRT SRT Pages From W471-E1-04Juni HartantoNessuna valutazione finora

- Sony-Cpd E220 PDFDocumento34 pagineSony-Cpd E220 PDFyako1511Nessuna valutazione finora

- Rockchip RK3399 IO List V1.5 enDocumento27 pagineRockchip RK3399 IO List V1.5 enXeltar AégisNessuna valutazione finora

- TLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q 10-Bit Analog-To-Digital Converters With Serial Control and 11 Analog InputsDocumento27 pagineTLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q 10-Bit Analog-To-Digital Converters With Serial Control and 11 Analog InputsCarlos Alberto de Andrade Freitas JuniorNessuna valutazione finora

- Man 8040M NFDocumento44 pagineMan 8040M NFjean bartNessuna valutazione finora

- DAC ADC Interfacing With 8051Documento37 pagineDAC ADC Interfacing With 8051Gowri100% (1)

- ADC Module Configuration & ChannelsDocumento12 pagineADC Module Configuration & ChannelsAndres CalleNessuna valutazione finora

- 82 Series - Modular Timers 5 ADocumento5 pagine82 Series - Modular Timers 5 Adragos_dimitriuNessuna valutazione finora

- Pulse-Width-Modulation Control Circuits Az7500EDocumento13 paginePulse-Width-Modulation Control Circuits Az7500EMy shop Cool100% (1)

- (11863264) R00 E-S-P Parada de SegurancaDocumento36 pagine(11863264) R00 E-S-P Parada de SegurancaJean da LE Soluções em EnergiaNessuna valutazione finora

- Codigo de FallaDocumento5 pagineCodigo de FallaMarco Yarasca RomeroNessuna valutazione finora

- U209B M AtmelDocumento19 pagineU209B M Atmelyassine yassineNessuna valutazione finora

- LCD SSD1815Documento36 pagineLCD SSD1815vuhongthuy1Nessuna valutazione finora

- Tlm-1903 Service ManualDocumento40 pagineTlm-1903 Service ManualdaldoggyNessuna valutazione finora

- Sanyo EC5-A - ChassisDocumento24 pagineSanyo EC5-A - Chassisivan BarriosNessuna valutazione finora

- PIC18F4550 ADC TutorialDocumento9 paginePIC18F4550 ADC TutorialKrishanu Modak100% (1)

- Sbaa332 PDFDocumento5 pagineSbaa332 PDFAnurag RajakNessuna valutazione finora

- SED1530 Series: Dot Matrix LCD Driver-ControllerDocumento20 pagineSED1530 Series: Dot Matrix LCD Driver-ControllerJuan Carlos BarandicaNessuna valutazione finora

- CAT7105 2.0A High Efficiency Step-Down DC/DC Converter Datasheet SummaryDocumento12 pagineCAT7105 2.0A High Efficiency Step-Down DC/DC Converter Datasheet Summarymonitores culpinaNessuna valutazione finora

- 3 Axis Control Box ManualDocumento12 pagine3 Axis Control Box ManualМарко СајићNessuna valutazione finora

- JVCDocumento26 pagineJVCDaniel CharlesNessuna valutazione finora

- V/I, I/V, V/F, F/V Converters Mod. MCM7A/EV: Volume 1/2 Theory and ExercisesDocumento48 pagineV/I, I/V, V/F, F/V Converters Mod. MCM7A/EV: Volume 1/2 Theory and ExercisesbrzNessuna valutazione finora

- 128K x8 bit 3.3V Low Power CMOS SRAMDocumento12 pagine128K x8 bit 3.3V Low Power CMOS SRAMsmhzzNessuna valutazione finora

- Gdi Uns881 107542Documento11 pagineGdi Uns881 107542Nguyen Duc NhaNessuna valutazione finora

- 1 Electronica IndustrialDocumento17 pagine1 Electronica Industrialjerrygo_03Nessuna valutazione finora

- V1-Using The ADC of 80C552Documento18 pagineV1-Using The ADC of 80C552Dams Ruc100% (1)

- Anais Do Workshop De Micro-ondasDa EverandAnais Do Workshop De Micro-ondasNessuna valutazione finora

- Python Binance Readthedocs Io en LatestDocumento226 paginePython Binance Readthedocs Io en LatestRicardo José ItriagoNessuna valutazione finora

- 400L Jacketed FermenterDocumento1 pagina400L Jacketed FermenterRicardo José ItriagoNessuna valutazione finora

- 1000L Jacketed FermenterDocumento1 pagina1000L Jacketed FermenterRicardo José ItriagoNessuna valutazione finora

- EthernetDocumento3 pagineEthernetRicardo José ItriagoNessuna valutazione finora

- Signal Sampling and Quantization - 1Documento20 pagineSignal Sampling and Quantization - 1Lana AlakhrasNessuna valutazione finora

- Preferred Audio Settings IC-7610 - ON2PCODocumento2 paginePreferred Audio Settings IC-7610 - ON2PCOtester van de testNessuna valutazione finora

- Fundamentals of Equalizers and Linear EqualizersDocumento22 pagineFundamentals of Equalizers and Linear EqualizersThota DeepNessuna valutazione finora

- John Arnold SamsonDocumento5 pagineJohn Arnold SamsonJ Arnold SamsonNessuna valutazione finora

- Service ManualDocumento81 pagineService ManualKiss IstvánNessuna valutazione finora

- Gemini - Amplifier P-700 - Service ManualDocumento12 pagineGemini - Amplifier P-700 - Service Manualapi-3711045100% (2)

- TG-40SP Ultrasonic Directional SpeakerDocumento2 pagineTG-40SP Ultrasonic Directional SpeakermeichengNessuna valutazione finora

- Quad 405 Mk2 Owners ManualDocumento14 pagineQuad 405 Mk2 Owners ManualAnthony IpNessuna valutazione finora

- The Ultimate Roland JV, JD, XV F.A.Q. (Don Solaris)Documento19 pagineThe Ultimate Roland JV, JD, XV F.A.Q. (Don Solaris)CirrusStratusNessuna valutazione finora

- Data CommunicationDocumento17 pagineData CommunicationSnehal KarkiNessuna valutazione finora

- Tutoring Questions 1Documento10 pagineTutoring Questions 1labibasalam0Nessuna valutazione finora

- Common Base Amplifier: CharacteristicsDocumento8 pagineCommon Base Amplifier: CharacteristicsfarhanmadhiNessuna valutazione finora

- Lic Project ReportDocumento9 pagineLic Project ReportJayachandra JVNessuna valutazione finora

- Histogram: CII4F3 / Digital Image ProcessingDocumento61 pagineHistogram: CII4F3 / Digital Image ProcessingAqmal Insan cendekiaNessuna valutazione finora

- Decorative PendantSpeaker Decorative Pendant Inline Speaker DataSheet-G875Documento1 paginaDecorative PendantSpeaker Decorative Pendant Inline Speaker DataSheet-G875ahmad allenNessuna valutazione finora

- HERTZ TechSheet DST30.3B Rev17ADocumento1 paginaHERTZ TechSheet DST30.3B Rev17ARenato de CastroNessuna valutazione finora

- Ads 1299Documento65 pagineAds 1299Adrian QuijijeNessuna valutazione finora

- Quick start guide for VMS ML-2Documento4 pagineQuick start guide for VMS ML-2Mendo KusaiiNessuna valutazione finora

- Natural Radio ReceiverDocumento4 pagineNatural Radio ReceiverFJ GLNessuna valutazione finora

- Filter Design 2Documento0 pagineFilter Design 2www.bhawesh.com.npNessuna valutazione finora

- Lecture 9 2Documento53 pagineLecture 9 2Trường HoàngNessuna valutazione finora

- Design and Implementation of Power Factor Correction (PFC) Converter With Average Current Mode Control Using DSPDocumento4 pagineDesign and Implementation of Power Factor Correction (PFC) Converter With Average Current Mode Control Using DSPPhúc ThiệnNessuna valutazione finora

- Image ImpedanceDocumento16 pagineImage ImpedanceErick Wangila WanyonyiNessuna valutazione finora

- Musical Sound Processing CsetubeDocumento2 pagineMusical Sound Processing CsetubeSara SwathiNessuna valutazione finora